基于多尺度等效模型的SiP熱分析及散熱優(yōu)化

袁偉星,曾燕萍,張 琦,張春平

(中科芯集成電路有限公司,江蘇無(wú)錫214072)

1 引言

微系統(tǒng)技術(shù)融合了微電子、微機(jī)電和微光電技術(shù),通過(guò)系統(tǒng)架構(gòu)和軟件算法,將多個(gè)具有不同功能的有源元件與無(wú)源組件,以及MEMS、光學(xué)器件等集成于同一封裝體,構(gòu)成一體化軟、硬件多功能集成,采用微納制造及微集成工藝實(shí)現(xiàn)系統(tǒng)結(jié)構(gòu)的微納尺度化,朝著高密度、小型化、低功耗、高可靠性、高效率的方向演進(jìn)[1-2]。微系統(tǒng)封裝主要基于集成電路工藝方法的進(jìn)步,發(fā)展趨勢(shì)即系統(tǒng)級(jí)封裝(SiP)技術(shù),它主要通過(guò)中道及后道工藝實(shí)現(xiàn),即通過(guò)對(duì)流片回來(lái)的芯片進(jìn)行再布線(RDL)以及先進(jìn)封裝技術(shù)實(shí)現(xiàn)系統(tǒng)集成[3-4]。

高功率SiP采用晶圓級(jí)封裝技術(shù),包含大量微米級(jí)尺度的微凸點(diǎn)、硅通孔(TSV)等,是一種典型的多尺度復(fù)雜結(jié)構(gòu),且集成度的不斷提高使SiP功率密度增大,導(dǎo)致封裝中熱管理問(wèn)題愈發(fā)突出,開發(fā)快速準(zhǔn)確的熱仿真技術(shù)、實(shí)現(xiàn)有效增進(jìn)SiP散熱效能是封裝設(shè)計(jì)中不可忽視的一部分[5]。衛(wèi)三娟[6]采用串并聯(lián)熱阻思路,利用能量守恒法將微凸點(diǎn)與底填料等效為等效塊,從而得出等效熱導(dǎo)率。戈長(zhǎng)麗[7]基于熱阻網(wǎng)絡(luò)的TSV單元等效,在等效單元面內(nèi)熱導(dǎo)率計(jì)算時(shí)采用并聯(lián)導(dǎo)熱通路,求得等效熱導(dǎo)率。文獻(xiàn)[8-9]采用等效熱導(dǎo)率研究方法,合理簡(jiǎn)化模型同時(shí)顯著降低計(jì)算資源消耗,大大提高了有限元仿真效率。

本文綜合文獻(xiàn)[6-7]的等效思路,將等效熱阻網(wǎng)絡(luò)運(yùn)用于微凸點(diǎn)單元,在等效單元面內(nèi)熱導(dǎo)率上采用串并聯(lián)思路,從而提取微凸點(diǎn)等效熱導(dǎo)率,合理簡(jiǎn)化SiP熱模型并進(jìn)行誤差分析,為后續(xù)SiP散熱優(yōu)化提供指導(dǎo)思路。

2 等效理論

針對(duì)微組件底部微凸點(diǎn)與底填料的多尺度情況,基于熱阻網(wǎng)絡(luò)的等效熱導(dǎo)率計(jì)算,采用各向異性的均勻立方塊代替大量微凸點(diǎn)和底填料,微凸點(diǎn)等效原理如圖1所示。該等效熱導(dǎo)率理論計(jì)算核心方法是:基于一維傅里葉導(dǎo)熱定律和串并聯(lián)電阻公式,得到單個(gè)周期單元等效熱阻網(wǎng)絡(luò),再反推得到整個(gè)結(jié)構(gòu)的等效熱導(dǎo)率。

圖1 微凸點(diǎn)等效原理

2.1 y方向等效熱導(dǎo)率計(jì)算

對(duì)于y方向,在微凸點(diǎn)單元上表面施加一個(gè)均勻熱流Qy(如圖2所示),單元四周為絕熱邊界,則熱流Qy全部沿著y方向傳導(dǎo),得到微凸點(diǎn)單元的并聯(lián)熱阻網(wǎng)絡(luò),熱阻等效模型如圖2(b)所示。

圖2 y方向等效熱導(dǎo)率計(jì)算模型

基于一維傅里葉導(dǎo)熱定律和并聯(lián)電阻公式,有:

將部件投影面積用參數(shù)p、d、h代替,因此等效單元y方向的熱導(dǎo)率ky為:

其中,Rs、Ru和Ry分別為微凸點(diǎn)熱阻、底填料熱阻和等效單元y方向熱阻,ks、ku為微凸點(diǎn)、底填料材料熱導(dǎo)率,As、Au和Ay為微凸點(diǎn)、底填料和等效單元在y方向的投影面積,d為微凸點(diǎn)直徑,p、h為微凸點(diǎn)節(jié)距、高度。

2.2 x-z方向等效熱導(dǎo)率計(jì)算

微凸點(diǎn)單元面內(nèi)熱導(dǎo)率相同,只需得到x方向的等效熱導(dǎo)率。根據(jù)微凸點(diǎn)單元的對(duì)稱性,取x方向單元的一半進(jìn)行分析,微凸點(diǎn)單元側(cè)視圖如圖3(a)所示。將模型分為A、B部分,其中A部分只含底填料,B部分含底填料和微凸點(diǎn),得到整體的串并聯(lián)熱阻網(wǎng)絡(luò),等效熱阻模型如圖3(b)所示。

圖3 x方向等效熱導(dǎo)率計(jì)算模型

同理,有方程:

因此等效單元x-z方向的熱導(dǎo)率kx為:

由式(3)、(5)可以得出,微凸點(diǎn)單元等效熱導(dǎo)率的變化取決于微凸點(diǎn)單元組成材料熱導(dǎo)率和微凸點(diǎn)節(jié)距與直徑。

3 有限元模擬

采用三維建模軟件ANSYS/SpaceClaim建立仿真模型,基于Workbench平臺(tái)中Icepak軟件進(jìn)行熱仿真,其中建模與熱仿真流程如圖4所示。

圖4 建模與熱仿真流程

3.1 熱建模

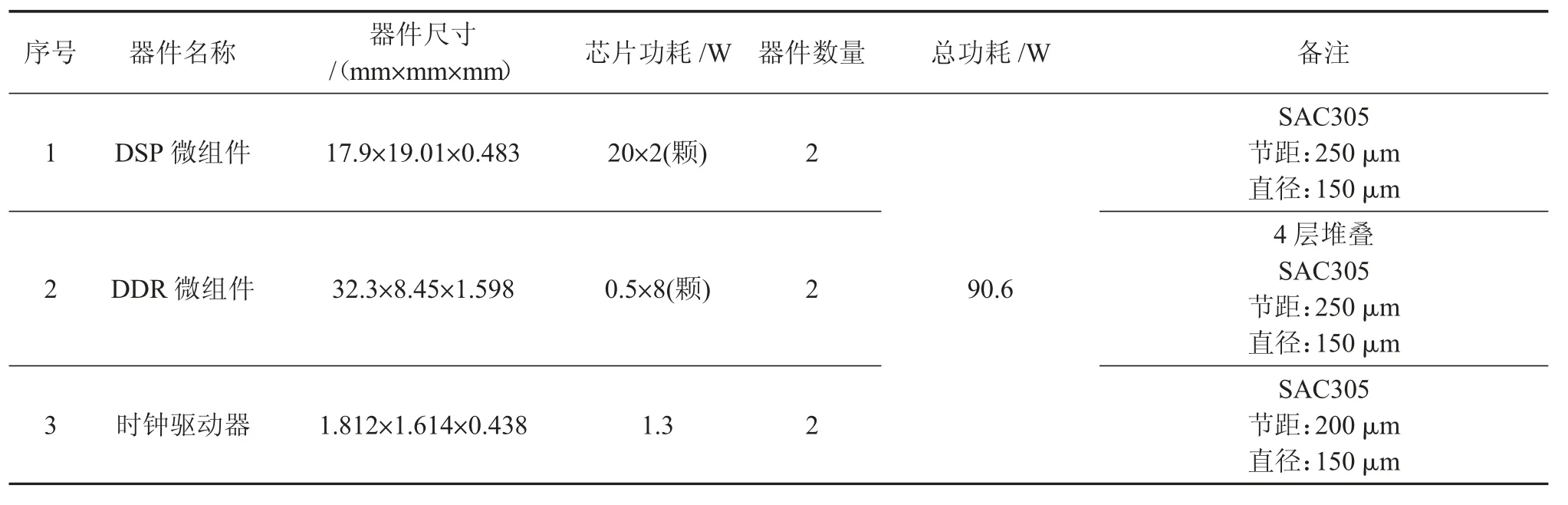

高功率SiP采用陶瓷雙腔封裝,內(nèi)部集成DDR微組件、DSP微組件、時(shí)鐘驅(qū)動(dòng)器和342顆阻容,主要器件尺寸參數(shù)如表1所示,其中DDR微組件為TSV互連的四層堆疊結(jié)構(gòu),DSP微組件為DSP裸芯片采用RDL互連,最終SiP封裝形式為CCGA1489,尺寸為45 mm×45 mm×9.59 mm。因DDR微組件和DSP微組件內(nèi)含有大量微米級(jí)尺度的微凸點(diǎn),建立熱模型時(shí)將微凸點(diǎn)與底填料簡(jiǎn)化成相同尺寸的等效塊,基于微凸點(diǎn)等效后的SiP三維模型如圖5所示。

圖5 SiP三維模型

表1 封裝主要器件尺寸、數(shù)量與功耗參數(shù)

3.2 布線層導(dǎo)入

將三維模型轉(zhuǎn)化為Icepak可識(shí)別對(duì)象,根據(jù)仿真精度和研究目的要求,需在熱模型內(nèi)導(dǎo)入基板、RDL層的布線過(guò)孔信息。利用Siwave軟件導(dǎo)出布線層文件,在Icepak內(nèi)將EDA模型文件導(dǎo)入至相應(yīng)位置,完成布線過(guò)孔導(dǎo)入的SiP模型如圖6所示。

圖6 SiP模型導(dǎo)入布線過(guò)孔

3.3 網(wǎng)格劃分

網(wǎng)格質(zhì)量好壞決定了求解計(jì)算精度及是否可以收斂,網(wǎng)格數(shù)量多少?zèng)Q定了計(jì)算資源與計(jì)算時(shí)間。因SiP模型復(fù)雜,網(wǎng)格劃分采用層次化分析方法,主要思路為:先局部后整體,先進(jìn)行微組件和單器件網(wǎng)格劃分,再進(jìn)行整體劃分。在JEDEC機(jī)箱內(nèi)采用非連續(xù)性、非結(jié)構(gòu)化網(wǎng)格對(duì)仿真模型進(jìn)行仿真劃分,計(jì)算得到整體網(wǎng)格單元數(shù)為3173463,節(jié)點(diǎn)數(shù)為3527406,最小面對(duì)齊率為0.53,滿足計(jì)算要求。

3.4 材料與方法

仿真中SiP總功耗為90.6 W,熱源芯片功耗參數(shù)見表1,Bump等效塊熱導(dǎo)率和其他封裝材料參數(shù)如表2所示。假設(shè)周圍環(huán)境溫度為25℃,仿真SiP在JEDEC機(jī)箱內(nèi)自然對(duì)流下的溫度分布,打開自然對(duì)流和輻射換熱,設(shè)置重力參數(shù)為-9.8 m/s2。

表2 CCGA封裝的材料參數(shù)

3.5 熱仿真結(jié)果與誤差分析

圖7 為常溫下基于Bump等效SiP自然散熱內(nèi)部主要組件的溫度云圖,由整體可以看出上腔DSP微組件功耗較大且為主要熱源區(qū),但最高溫度出現(xiàn)在下腔CLK芯片上,主要是CLK芯片熱流密度達(dá)44.5 W/cm2,散熱路徑為上蓋板通路,造成通路上的局部溫度集中;焊柱和基板溫度有所下降,遠(yuǎn)離基板中心位置的焊柱邊界區(qū)域溫度最低。圖8為常溫下精確SiP模型自然散熱切面溫度云圖,表3為等效SiP與精確SiP仿真計(jì)算時(shí)間,已知誤差λ和效率η計(jì)算公式為:

表3 等效模型與精確模型計(jì)算時(shí)間對(duì)比

圖8 精確SiP模型主要組件溫度云圖

其中T′max、Tmax為等效SiP、精確SiP溫度最高值,tequ、tacc為同溫度下等效SiP、精確SiP仿真計(jì)算時(shí)間。由式(6)、(7)定量分析可知,基于Bump等效SiP最高溫度值與精確模型最高溫度值誤差為7.6%,滿足熱仿真精度需求,同時(shí)使計(jì)算時(shí)間節(jié)約了58 %,大大提高了仿真效率。文獻(xiàn)[7]中求解TSV精確模型與等效模型時(shí),計(jì)算總效率提高了66.7 %,但其精確模型較為簡(jiǎn)單,本文SiP建模及求解復(fù)雜程度較高,為復(fù)雜SiP熱仿真提供更為全面的數(shù)據(jù)支撐。硅芯片失效溫度為175℃,考慮到仿真誤差,將芯片結(jié)溫控制在160℃以內(nèi),圖7結(jié)果顯示SiP整體發(fā)熱過(guò)高,因此需對(duì)SiP系統(tǒng)進(jìn)行輔助散熱設(shè)計(jì),將溫度控制在允許范圍內(nèi)。

圖7 基于Bump等效SiP主要組件溫度云圖

4 散熱優(yōu)化設(shè)計(jì)

按以下3種方案對(duì)基于Bump的高功率SiP進(jìn)行輔助散熱優(yōu)化:

①在SiP上蓋板添加叉翅散熱器(85.4 mm×85.4 mm×30.4 mm),主要是讓SiP產(chǎn)生的熱量通過(guò)散熱器快速傳導(dǎo)并釋放出去;

②在方案①的基礎(chǔ)上進(jìn)行強(qiáng)迫風(fēng)冷,假設(shè)風(fēng)速為3 m/s,通過(guò)流體與SiP器件進(jìn)行熱量交換,從而對(duì)SiP進(jìn)行散熱;

③在SiP上蓋板設(shè)計(jì)單相微通道熱管結(jié)構(gòu)(50 mm×50 mm×4 mm),單通道截面尺寸為0.5 mm×3 mm,微通道內(nèi)液冷水為環(huán)境溫度,流速為0.2 m/s。

圖9 (a)、(b)、(c)分別為SiP在方案①、②、③下的切面溫度云圖分布,可知方案①能使SiP最高溫度降低41.7%左右,方案②的散熱能力遠(yuǎn)超于方案①,方案③散熱能力略優(yōu)于方案②,主要原因是:(1)液冷表面?zhèn)鳠嵯禂?shù)高于強(qiáng)迫風(fēng)冷,自然對(duì)流表面?zhèn)鳠嵯禂?shù)小于強(qiáng)迫風(fēng)冷;(2)SiP下腔芯片主要散熱通道為上蓋板,易于下腔形成局部溫度集中。不同散熱方案下基于Bump等效SiP最高溫度如圖10所示,SiP內(nèi)最高溫度值隨著表面?zhèn)鳠嵯禂?shù)的增大而減小,方案②、③能使SiP最高溫度保持在160℃以內(nèi),此時(shí)SiP無(wú)溫度失效風(fēng)險(xiǎn)。

圖9 不同散熱方案下基于Bump等效SiP切面溫度云圖

圖10 不同散熱方案下基于Bump等效SiP最高溫度

5 結(jié)論

本文基于等效理論方法,將多尺度SiP封裝結(jié)構(gòu)簡(jiǎn)化成含等效熱導(dǎo)率塊的三維結(jié)構(gòu)熱模型,該方法有效簡(jiǎn)化SiP內(nèi)存在的大量微凸點(diǎn),快速獲得封裝結(jié)構(gòu)溫度場(chǎng)分布結(jié)果,與精確封裝結(jié)構(gòu)熱仿真相比效率提高了58%,同時(shí)仿真誤差為7.6%,保證了仿真精確度。在等效SiP熱模型進(jìn)行RDL、基板層導(dǎo)入布線過(guò)孔信息,是提高仿真精度的手段。對(duì)比SiP 3種散熱優(yōu)化設(shè)計(jì)方案,可知微通道液冷熱沉散熱效果最佳,后續(xù)可設(shè)計(jì)不同微通道結(jié)構(gòu),解決大功耗SiP散熱需求。本文的分析方法對(duì)今后多尺度大功耗SiP熱仿真及散熱優(yōu)化具有一定的指導(dǎo)意義。