基于差分傳輸管預充電邏輯的功耗恒定性電路改進設計

姚茂群 李聰輝

(杭州師范大學信息科學與工程學院 杭州 311121)

1 引言

功耗分析攻擊是當前眾多旁路攻擊中一種有效且易于操作的攻擊方法,其通過獲取電子元器件在運行時所產生的功耗,并利用該功耗與元器件中所運行密碼算法的某些運算結果之間的相關性來進行分析,進而獲得有價值的秘密信息[1–5]。而這一相關性是由當前流行的數字集成電路邏輯–CMOS邏輯單元所決定的,這種邏輯單元的功耗與其輸入輸出信號的翻轉狀態(“0→1”或“1→0”)有密切聯系,并且這兩種信號翻轉時的電流所對應產生的電路功耗是不同的。而當CMOS邏輯單元在連續的兩個時鐘周期都沒有發生信號的翻轉時,由于沒有產生動態電流,因此在這連續的時鐘周期里電路所產生的功耗較少,與有信號翻轉時的電路功耗有明顯的差異。因此,這種差異性就給攻擊者通過分析功耗來獲得秘密信息提供了理論依據[6–11]。

近年來,研究者逐漸重視對電路級抗旁路攻擊的研究,其中對功耗恒定性電路的研究是一個比較熱門的方向。在這之中就有學者提出了一種可以讓電路的功耗曲線不隨信號取值變化而變化的雙軌預充電邏輯結構(Dual Rail Precharge, DRP),其中最具代表性的是Tiri 等人[12]提出的 SABL(Sense Amplifier Based Logic)電路和WDDL(Wave Dynamic Differential Logic)電路[13]。因此也有眾多學者基于這些邏輯電路做了相關的研究[14–17],但是由于SABL, WDDL這些邏輯單元存在CMOS邏輯中固有的提前傳播效應[18],且電路中某一時刻的整體功耗是各個單元電路在這個時刻的疊加,因此跳變時間的不同就會造成整體功耗的差異。正是因為有了這種功耗差異,因此上述提到的DRP結構仍然存在被功耗攻擊的風險。針對這些不足之處,國內有學者受到了互補傳輸管邏輯(Complementary Pass-transistor Logic, CPL)的啟發,提出了一種基于 CPL 的新型雙軌預充電邏輯–差分傳輸管預充電邏輯(Differential Pass-transistor Precharge Logic, DP2L)[19],該邏輯電路不僅可以實現功耗恒定的性質,還可以消除以往DRP結構中存在的提前傳播效應問題,這極大地提升了電路在抗功耗攻擊方面的能力。

但是,利用Hspice軟件進行仿真實驗,實驗結果表明已提出的基于CPL結構的DP2L電路仍然存在一定程度的功耗信息泄露,依舊存在被功耗攻擊的可能性。對此,本文在分析了該電路邏輯結構的基礎之上,對該電路的結構進行了改進,使其更加滿足功耗恒定的特性。并通過與改進前的電路進行比較,驗證了改進后電路在功耗恒定上的優勢。

2 DP2L雙軌預充電邏輯電路

CMOS邏輯單元在輸出端信號發生“0→1”翻轉或“1→0”翻轉時消耗能量。除此之外,電路不消耗能量。因此眾多研究者基于這種相關性進行了較多的研究,并已經提出了多種可以消除這種相關性的功耗恒定性電路邏輯,例如SABL, WDDL,LBDL[20]以及DP2L邏輯等等,這些電路邏輯都屬于不同結構的雙軌預充電邏輯。

雙軌預充電邏輯的特點如下:

(1) 一個雙軌預充電邏輯電路是由兩個單軌預充電邏輯電路組合而成的;

(2) 雙軌(單軌)預充電邏輯電路的一個時鐘周期分為預充電和求值兩個階段;

(3) 預充電階段時,雙軌(單軌)預充電邏輯電路的所有互補輸入信號端都輸入預充電值低電平“0”。求值階段時,所有互補輸入信號端都輸入互補值;

(4) 預充電階段時,雙軌(單軌)預充電邏輯電路的輸出端都輸出低電平“0”信號。求值階段時,雙軌預充電邏輯門采用了差分互補的雙端輸出形式,即若一個輸出信號為高電平“1”,則另一個輸出信號必為低電平“0”。

這樣設計的目的就是使得雙軌預充電邏輯電路從預充電階段進入求值階段時,不管輸入信號取何互補值,兩個互補輸出端都是僅有一個會發生“0→1”的翻轉。當從求值階段進入預充電階段時,互補輸出端也是僅有一個發生“1→0”的翻轉。這就保證了固定的信號翻轉率和功耗恒定性,消除了輸入信號與功耗的相關性。

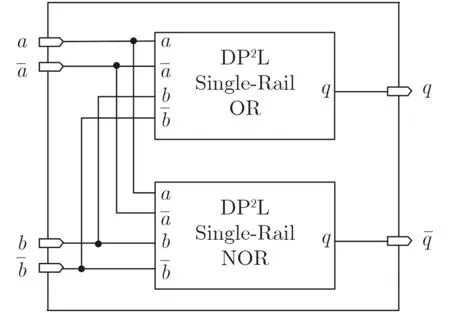

圖1和圖2分別為DP2L單軌和雙軌輸出“或”邏輯門,通過這兩個電路結構來詳細闡述其預充電和求值過程。圖1中P1~P6 的6個PMOS管用來實現電路的預充電功能;NMOS管N5和N6用來實現該電路的具體邏輯。即當輸入端輸入互補信號值時,電路進入求值階段,此時這兩個NMOS管中的一個會被導通,從而形成一條從輸入端到反相器的通路;余下的NMOS管N1~N4的主要作用是消除提前傳播效應[19];反相器是作為輸出負載的驅動單元。例如,在預充電階段,(a,b)接收到輸入信號(0, 0),()也接收到輸入信號(0, 0),這時該邏輯單元的所有PMOS管都被導通,電源VDD經過反相器之后輸出低電平“0”;當進入求值階段時,若(a,b)接收到輸入信號(1, 1),則(a,b)接收到輸入信號(0, 0),此時N2, N4, N5分別打開,N1, N3,N6保持關閉狀態,此時就只有N2, N5和反相器構成一條唯一通路,該條通路將連接N2的b信號值輸送到反相器,經過反相器后輸出端q的值為高電平“1”,滿足“或門”的電路邏輯。

圖1 DP2L單軌輸出“或”邏輯

圖2 DP2L雙軌輸出“或”邏輯的構成

而其他邏輯功能單元只需要替換電路最左側一列的兩個輸入信號就可以利用類似的電路結構來實現[19]。

將單軌預充電邏輯結構的正邏輯與其對應的負邏輯相組合,就形成了DP2L雙軌預充電邏輯結構。圖2以“或門”為例給出了DP2L雙軌輸出“或”邏輯的構成方式,它由“或”和“或非”單軌預充電邏輯結構組合而成,其中“或”邏輯門的輸出端與DP2L雙軌輸出端q直接相連,“或非”邏輯門的輸出端與DP2L 雙軌輸出端q直接相連。因此,根據該電路的設計特點,若要實現DP2L雙軌輸出“或非”邏輯,則只需要將q和q交叉換線即可。該電路的具體工作步驟為:預充電階段時,所有輸入信號端都輸入低電平預充電值“0”,根據之前對單軌邏輯的分析,這時雙軌邏輯的輸出端q和q的值也分別為“0”;求值階段時,所有互補輸入信號端均輸入互補信號值,則雙軌邏輯的輸出端q和q也輸出互補值。因此當電路從預充電階段進入求值階段后,不管輸入信號端取何互補值,其兩個輸出端僅有一個會產生“0→1”的跳變,而另一個輸出端的值則保持“0”不變;而當電路的求值階段結束進入預充電階段時,DP2L邏輯電路的輸入信號端則都輸入低電平預充電值“0”,此時邏輯電路的兩個輸出端中也僅有一個會產生“1→0”的跳變。

3 DP2L邏輯電路的功耗分析

通過對圖1中DP2L單軌輸出“或”邏輯的仔細分析,發現該電路邏輯在求值階段晶體管充放電的數量并不相同。也就是說,電路功耗與輸入信號的取值并不完全獨立,仍然存在相關性。例如,當電路進入求值階段,如果輸入信號的值(a,a)為(1,0), (b,b)的值也為(1, 0),則NMOS管N2, N5導通,PMOS管P2, P6導通,由于P1, P5斷開,則電路將僅對N2, N5兩個晶體管放電。而當輸入端信號的值(a,a)為(0, 1), (b,b)的值也為(0, 1)時,NMOS管N3, N6導通,PMOS管P3, P5導通,電路將對這4個管子放電。這樣當輸入信號不同時,電路所消耗的功耗就會因為晶體管放電數目不同而造成差異,使得電路不能達到完全的功耗平衡。

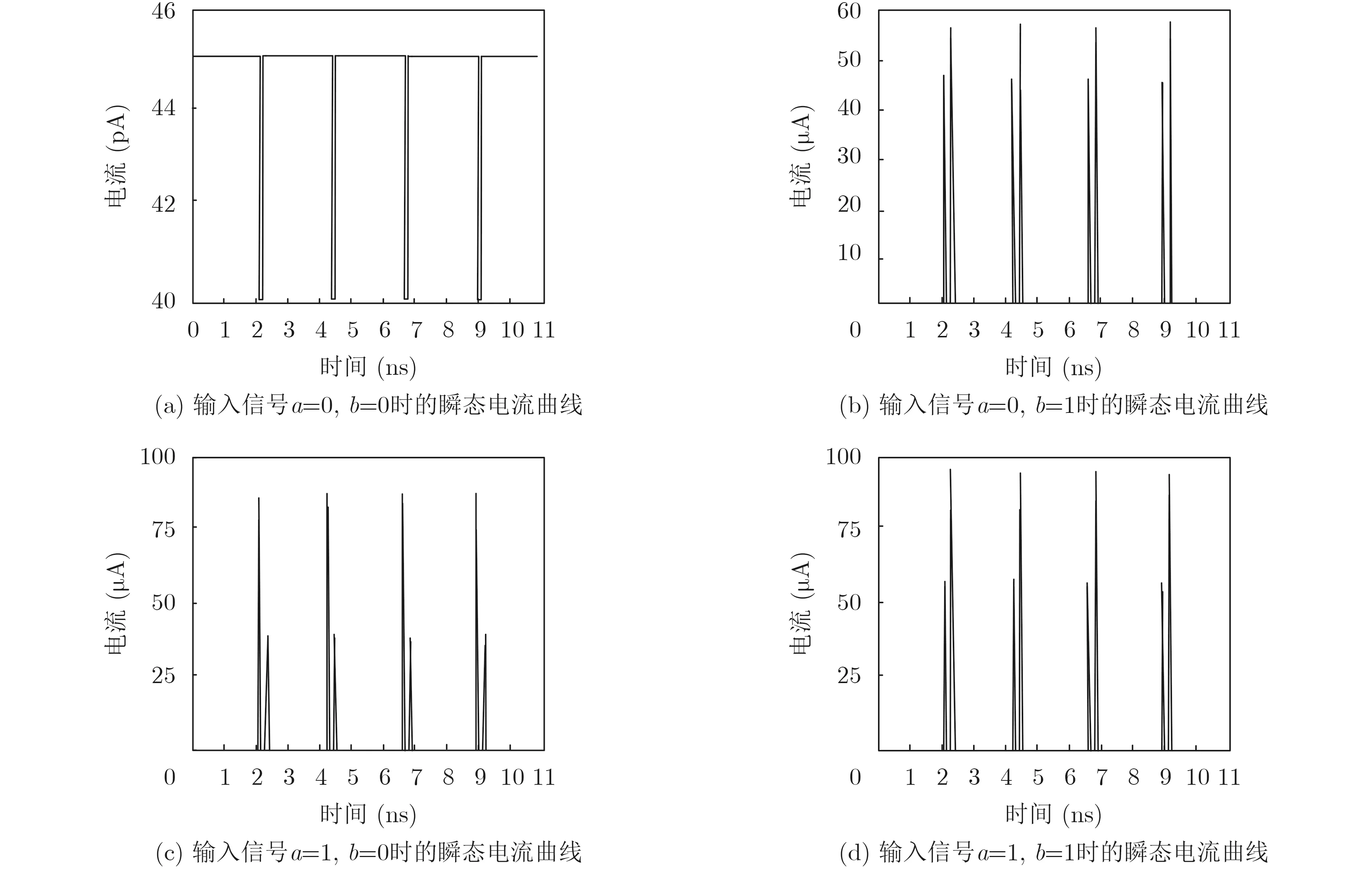

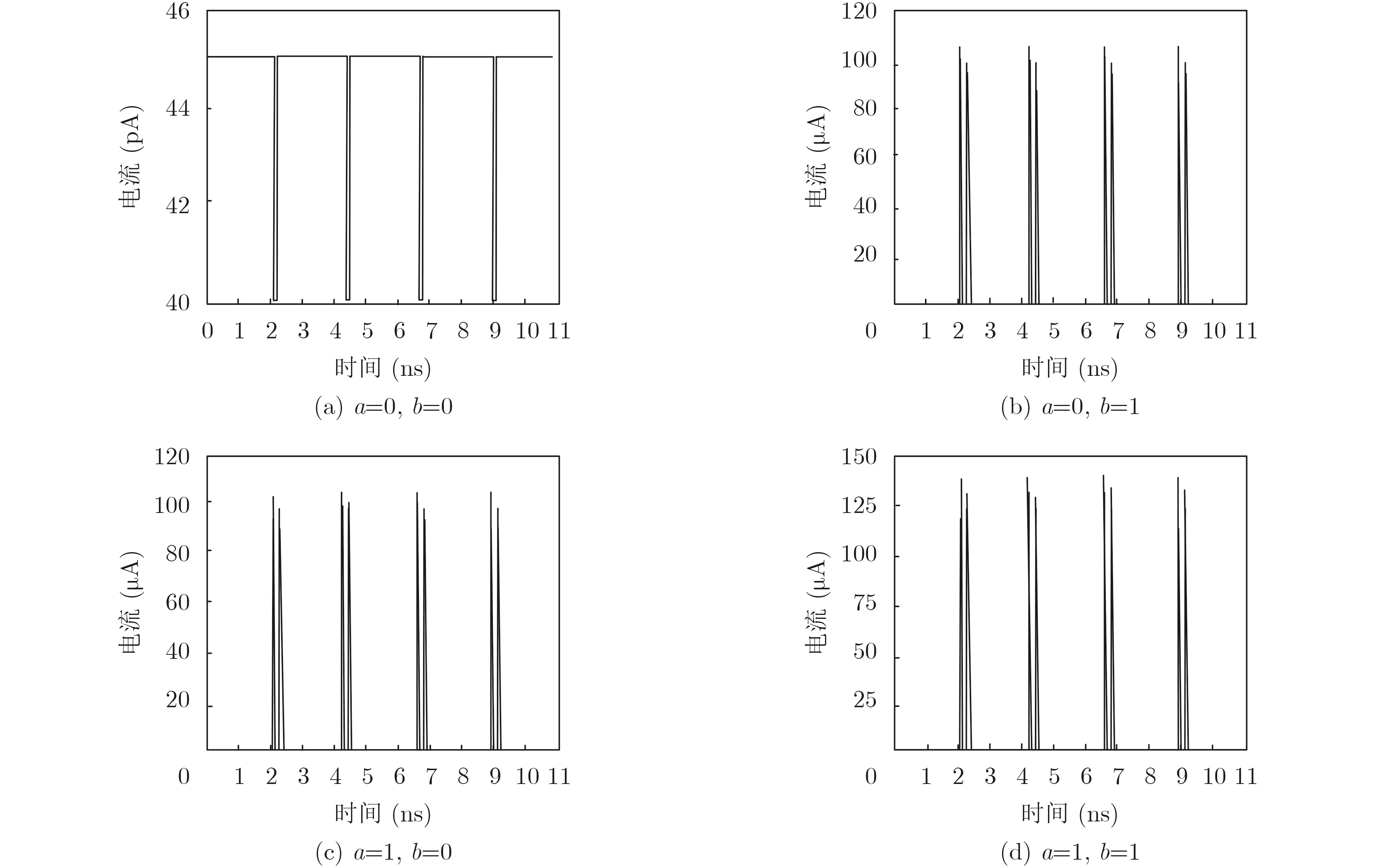

為了驗證此分析,利用Hspice軟件對DP2L單軌輸出“或”邏輯進行模擬實驗,圖3中有明顯電流峰值的部分為電路進入求值階段后輸入信號(a,b)的值分別為(0, 0), (0, 1), (1, 0), (1, 1)時的電源端瞬態電流曲線,即可以表示為運行時的邏輯電路功耗變化。圖中橫坐標表示運行時間,縱坐標表示電源端瞬態電流,將相同的輸入信號運行4個周期以保證數據的準確性。圖中以2.3 ns為一個周期,一個周期中包含預充電和求值兩個階段,其中有明顯電流峰值的時段為求值階段,其余皆為預充電階段。圖中可看出一個周期中包含兩個相鄰的電流峰值,先產生的電流峰值表示輸出信號發生“0→1”翻轉時產生的電流,后產生的電流峰值表示輸出信號發生“1→0”翻轉時產生的電流。

圖3(a)由于輸入信號(a,b)的值為(0,0)時,“或”邏輯輸出并沒有發生翻轉,因此產生的動態功耗即電源端電流非常小;而輸入其他信號時,由于發生了輸出信號的翻轉,即產生了充放電過程。并且可明顯看出同一周期中電流曲線的相鄰兩個峰值具有明顯差異,這個差異是由輸出信號發生“0→1”,“1→0”翻轉時所產生的不同功耗所造成的。因此,攻擊者仍然可以利用這個差異進行有效的攻擊。

圖3 4種輸入信號下的DP2L單軌輸出“或”邏輯瞬態電流曲線

4 DP2L邏輯電路的改進

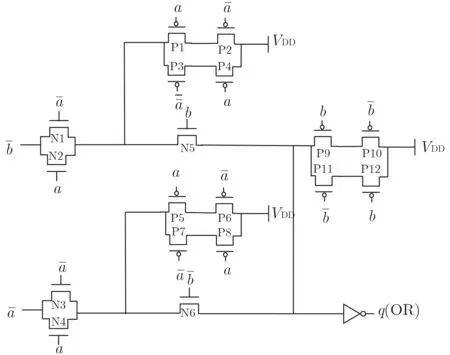

經過以上對DP2L邏輯的分析,圖4所示為改進后的DP2L單軌輸出“或”邏輯。分析如下:在求值階段時,當輸入端(a,a)的值為(1, 0), (b,b)的值也為(1, 0)時,NMOS管N2, N5導通,PMOS管P3,P11導通,則電路將僅對N2, N5, P3, P11這4個晶體管放電。而當輸入端信號(a,a)的值為(0, 1), (b,b)的值也為(0,1)時,NMOS管N3, N6導通,PMOS管P5, P9導通,則電路也將對4個管子放電。因此,在求值階段不管輸入信號為何值,晶體管的翻轉數量都是恒定的;而預充電階段時,輸入信號都為低電平“0”,此時由于PMOS管全部都被導通,因此晶體管的放電數量亦恒定。因此只要保證邏輯電路中所使用的PMOS管的規格參數全部相同,NMOS管的規格參數也全部相同,則經過改進后的DP2L邏輯在不同階段的功耗都是由相同參數和數量的晶體管充放電產生的,這就保證了功耗恒定的性質。其他的基于DP2L的邏輯門電路根據相同的改進方法即可達到相同的效果。

圖4 改進后DP2L單軌輸出“或”邏輯

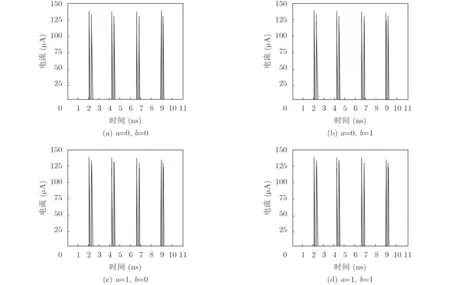

為了驗證此分析,通過Hspice軟件對改進后的DP2L單軌輸出“或”邏輯進行模擬,圖5中有明顯電流峰值的部分為求值階段時輸入信號(a,b)的值分別為(0, 0), (0, 1), (1, 0), (1, 1)時的電源端電流曲線。所使用的模擬實驗方法與圖3中所使用的完全相同。

圖5 4種輸入信號下的改進后DP2L單軌輸出“或”邏輯瞬態電流曲線

由以上模擬結果可知,經過改進后的DP2L單軌輸出“或”邏輯在不同輸入信號取值的情況下,一個周期中相鄰兩個電流峰值的差異較小,與改進前相比有較大的改善。這就保證了電路在輸出信號發生“0→1”,“1→0”翻轉時具有近乎相等的功耗,從而改善了功耗恒定的特性。

將改進后的DP2L單軌輸出“或”邏輯和改進后的DP2L單軌輸出“或非”邏輯相組合就構成了如圖2所示的DP2L雙軌輸出“或”邏輯。利用Hspice對該DP2L雙軌輸出“或”邏輯進行模擬,圖6中有明顯電流峰值的部分為求值階段時輸入信號(a,b)的值分別為(0, 0), (0, 1), (1, 0), (1, 1)時的電源端電流曲線。所使用的模擬實驗方法與圖3中所使用的完全相同。分析可得:不管輸入端的信號取何值,該邏輯門電路所表現出的功耗都是完全恒定的,并且當輸出信號產生“0→1”和“1→0”翻轉時電路所產生的功耗也是近似相同的。

圖6 4種輸入信號下改進后DP2L雙軌輸出“或”邏輯瞬態電流曲線

5 功耗恒定性分析

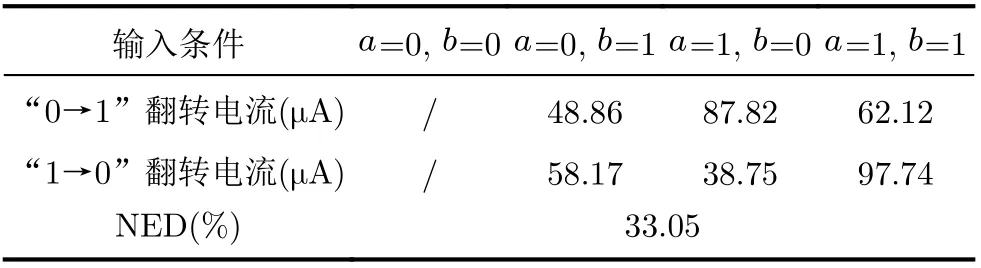

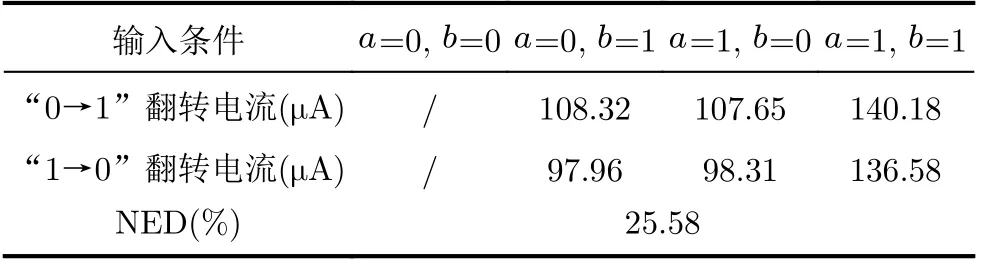

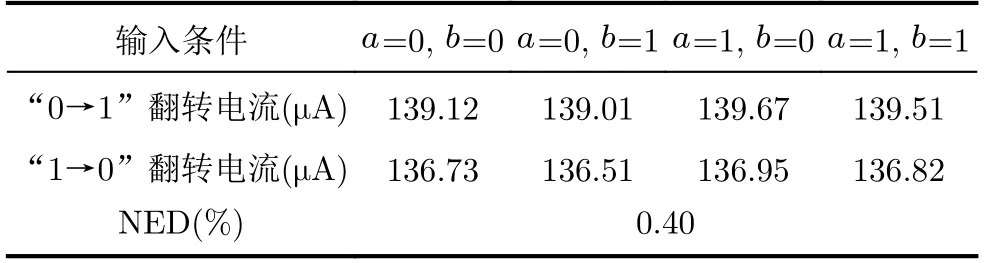

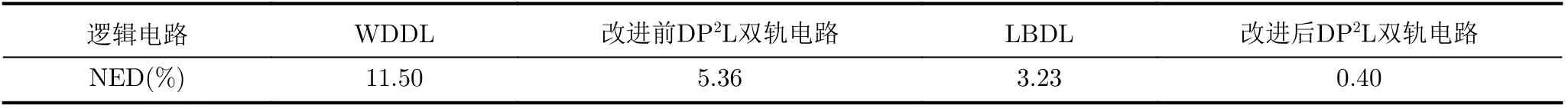

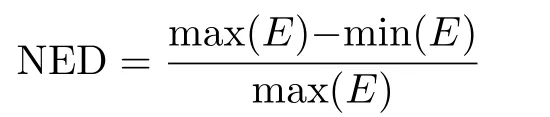

為驗證改進后DP2L電路的功耗恒定特性,將圖3、圖5、圖6中的數據進行分析和整理,如表1–表3所示,表4為國際上同類型邏輯電路的功耗恒定性能比較。表中分別列出了電路改進前后在不同輸入條件下發生“0→1”和“1→0”翻轉時電流數據的平均值,以及衡量功耗恒定特性的評價指標:標準化能量偏差(Normalized Energy Deviation,NED)[13]。其定義為

表1 改進前DP2L單軌電路相關參數

表2 改進后DP2L單軌電路相關參數

表3 改進后DP2L雙軌電路相關參數

表4 同類型邏輯實現的“或”門標準化能量偏差對比

式中,E是電路在一個運算周期所產生的功耗值的集合。NED的取值范圍在[0,1],且數值越小表明該電路的功耗恒定性能越好。

由表4可得,改進后的DP2L電路在功耗恒定特性上明顯優于其他邏輯電路,前者較高的NED值就表現出了一定程度的數據與功耗的相關性,更容易遭受到功耗攻擊。而改進后的電路以其較低的NED值就體現出了較高的抗功耗攻擊性能。

6 結束語

通過分析DP2L電路的功耗恒定特性并經過Hspice軟件的模擬驗證,發現該電路無法完全滿足功耗恒定特性。因此本文對DP2L電路進行改進,并對改進后電路進行仿真測試和NED值的比較,結果表明改進后的DP2L電路在功耗恒定的特性上有了明顯的提升,從而進一步為密碼功能模塊的可靠性和安全性提供有力支撐。