應用于MEMS基頻率源的CMOS溫度傳感器

黃繼偉, 陳星, 王科平

(1. 福州大學物理與信息工程學院, 福建 福州 350108; 2. 天津大學微電子學院, 天津 300072)

0 引言

隨著人類社會信息化、 網絡化、 智能化進程, 越來越多的電子產品進入了人們的生產生活中, 而幾乎所有的電子系統都需要基準頻率源. 近年來基于MEMS( micro-electro-mechanical system)的頻率源由于其體積小, 諧振頻率高等原因, 成為替代石英晶體的一大熱門研究[1-4]. 但是MEMS基的頻率源本身溫漂系數較大, 如BAW(bulk acoustic wave resonator )器件的溫漂系數為5.00 × 10-4[1], DETF(double-ended-tuning fork )器件的溫漂系數也超過了4.80 × 10-4[2], 截面Lame模式諧振器的溫度系數達到了1.45 × 10-3[3], 而目前研究最為熱門的FBAR(film bulk acoustic resonator)器件未經溫度補償之前的溫度系數甚至超過2.00 × 10-3[4]. 為使這些基于MEMS的頻率源能在-55~125 ℃溫度范圍內提供穩定的基準頻率, 就必須測量片上溫度, 再根據溫度信息進行相應的頻率補償, 實現較小的溫漂.

傳統溫度傳感器, 如熱敏電阻、 鉑電阻等因為體積大, 需要額外讀取電路, 無法與CMOS工藝兼容實現片上集成, 并不適于當前需求. 而CMOS溫度傳感器則容易實現在片測溫. 本研究以雙極型晶體管(bipolar junction transistor, BJT)作為測溫核心器件, 設計了一種測溫范圍為-55~125 ℃, 精度為± 0.5 ℃的片上CMOS溫度傳感器. 該溫度傳感器在片內集成了控制時鐘電路, 只需輸入一個基本時鐘信號即可正常驅動, 大大降低了應用的復雜程度, 降低了與MEMS基頻率源電路一起實現片上集成的難度.

1 BJT基溫度傳感器的基本原理

溫度傳感器的工作機制是將溫度信號轉換為數字信號輸出, 因此需要獲取與溫度相關的信號, 通過ADC轉換為數字信號, 并通過數學換算得到溫度讀數.

1.1 BJT基極-發射極電壓與溫度之間的關系

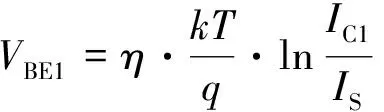

兩個相同的PNP 晶體管QL和QR以1∶p的電流比率進行偏置, 如圖1所示. QL的基極-發射極電壓VBE1具有與絕對溫度負相關的特性(complementary to absolute temperature, CTAT ), 該電壓可以表示為:

圖1 雙極型晶體管測溫基本原理Fig.1 Basic operation of a BJT-basd temperature sensor

(1)

其中:η是一個與工藝參數相關的非理想因子(通常情況下,η≈1);k是玻爾茲曼常數(k=1.38×10-23);T是熱力學絕對溫度;q為電子電量;IC1是晶體管的集電極電流;IS則是晶體管的飽和電流.

類似地, 可得到QR的基極-發射極電壓VBE2,VBE1和VBE2之間的差值為ΔVBE:

(2)

(3)

可以看出, 在電流密度比例p保持恒定的情況下, ΔVBE與絕對溫度成正比例(proportional to absolute temperature, PTAT ).

1.2 溫度傳感器測溫基本原理

由CTAT電壓和PTAT電壓線性組合, 可得到與溫度無關的帶隙基準電壓:

VREF=Vbandgap=VBE+α·ΔVBE

(4)

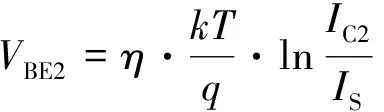

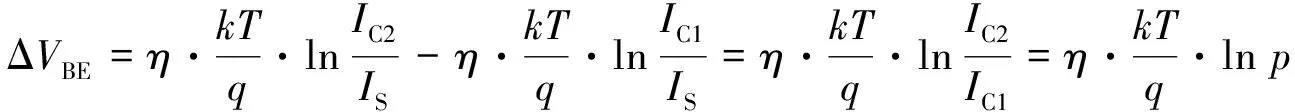

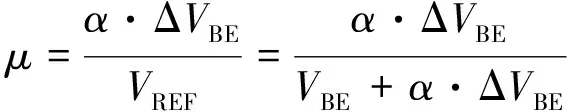

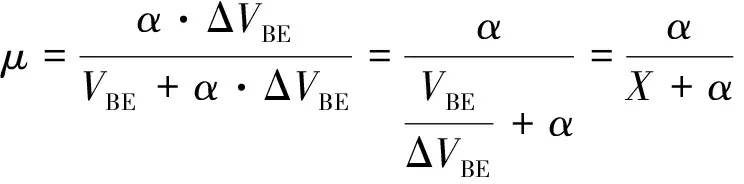

其中:α是增益因子, 在晶體管的電流密度比例確定之后將保持不變. 通過模數轉換器(analog-to-digital converter, ADC)可求出放大后的PTAT電壓α·ΔVBE與基準電壓VREF的比值μ:

(5)

由于α·ΔVBE與絕對溫度成正比例, 而基準電壓VREF與溫度無關, 因此比值μ將是與絕對溫度成正比例的線性函數, 可以將該比值進行線性縮放, 得到攝氏溫度讀數DOUT:

DOUT=A·μ+B

(6)

其中:A和B均為常數, 通常情況下,A≈600,B≈-273.

設計產生與溫度無關的帶隙基準電壓VREF需要設計精確的帶隙基準電路, 而實際上與溫度相關的兩個量是VBE和ΔVBE, 對式(5)分子分母同時除以ΔVBE, 可得:

(7)

食用油是人們制作佳肴時的必備品。中糧集團旗下食用油品牌福臨門已形成嚴格的可追溯體系,以確保油質安全。食用油的保質期一般為18個月,福臨門產品每批次在出廠前都會留足18箱,作為每個月實時檢驗與追蹤的樣本,一旦發現問題,可根據每桶油的編碼及追溯體系找到市場上留存的所有產品;反之,如果福臨門產品在市場上被反饋有問題,也可根據編碼查找到該產品的生產日期、生產線等一系列基礎信息,以及市場中同一批次產品的流向。無論是正向追溯還是反向追溯,2小時內即可實現。

(8)

因此, 只需要求出式(7)中X=VBE/ΔVBE的值, 再通過式(8)進行數學換算即可得到攝氏溫度[5].

2 溫度傳感器電路設計實現

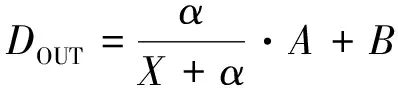

根據前文所述, 可設計如圖2所示的系統. 由圖2可見, 測溫前端電路產生與溫度相關的電壓VBE和ΔVBE, Zoom ADC則實現對二者比值X的量化并輸出, 通過片外或者片內MCU則對X進行數學計算, 即可求得溫度.

圖2 溫度傳感器的系統框圖Fig.2 Block diagram of the temperature sensor

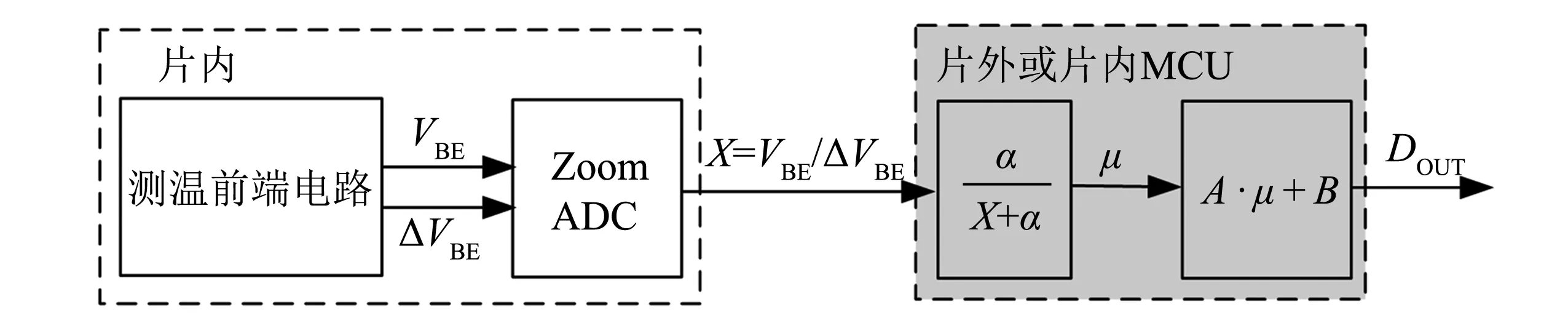

2.1 測溫前端電路

設計的測溫前端電路如圖3所示. 圖中左側為啟動電路. 當電路處在不正常工作點時, 運放輸出節點電位為高電位, PMOS電流源不導通. 此時,A、B點的電位為零, 使MN1截止,C點電位由MP1、 MP2提升到VDD, 使得MN2導通, 從而將運放輸出節點的電位拉低, 共源共柵電流源導通. 當電路進入正常工作狀態時,A、B點電位升高, 使MN1導通, 進而拉低C點電位使得MN2截止, 啟動電路與偏置電路斷開連接, 啟動電路不再影響其他部分.

圖3 測溫前端電路Fig.3 Circuit diagram of the sensor front-end

實際上, BJT的VBE與溫度之間并非完全一階線性關系, 而是存在一定曲率. 通過使用PTAT偏置電流, 可以在一定程度上減弱曲率帶來的影響[5], 使VBE與溫度關系更加準確, 適應大量程測溫需求. 因此, 可通過偏置電路產生PTAT電流來偏置核心電路的晶體管. 通過運放的負反饋鉗位, 圖3中A、B節點的電位相等, 而通過兩支路BJT的電流密度不同, 因此將以式(3)的方式產生電壓差ΔVBE, 該電壓差加在電阻Rb兩端, 產生PTAT電流. 同時為了降低運放失調帶來的影響, 使用了斬波運放.

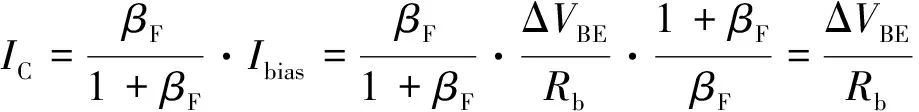

伴隨現代CMOS工藝的發展, 特征尺寸不斷縮小, BJT的電流增益系數βF不斷減小, 使集電極電流出現誤差進而帶來VBE的誤差[6]. 在偏置電路中引入補償電阻Rβ, 由于A、B節點的電位相等, 則可通過下式求得偏置電流:

將式(9)求得的偏置電流代入BJT的集電極、 發射極電流關系, 可得:

(10)

由式(10)可知, 集電極電流已經和電流增益系數βF無關, 從而從理論上消除了這個誤差.

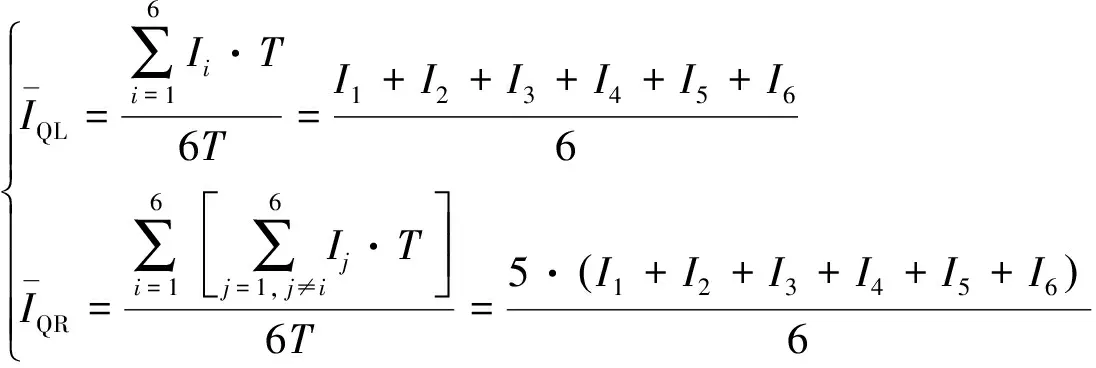

通過偏置電路產生的PTAT電流后, 通過電流鏡復制到溫度核心電路, 再通過動態匹配(dynamically element matched, DEM )電路來控制電流選擇開關, 使6個鏡像電流源的電流輪流單獨偏置QL, 其余電流則偏置QR[7]. 即一個動態匹配周期內流過晶體管的平均電流為:

(11)

最后, 通過右側的單位增益緩沖電路, 將溫度核心電路所產生的VBE1和VBE2電壓輸出至后端電路, 不僅提高了對后端電路驅動能力, 也避免了對后端電路充放電導致的核心晶體管偏置電流發生變化, 進一步提高了系統的穩定性和精度.

2.2 縮放式模數轉換器

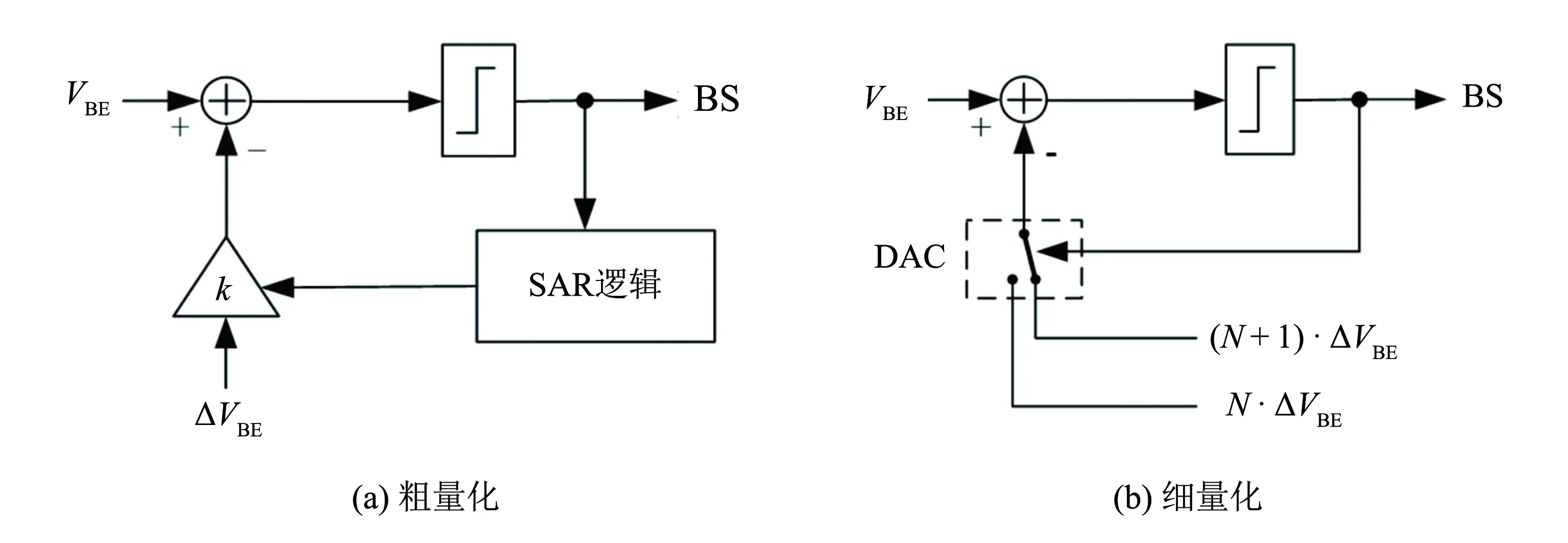

設計的溫度前端電路產生VBE1/ΔVBE的比值X在 -55~125 ℃范圍內的取值為25.510至7.405, 可將該比值分為整數部分和小數部分, 即X=N+n, 其中整數部分N通過較為粗略的SAR階段來量化, 小數部分n則通過較為精細的Sigma-Delta階段來量化.

ADC在粗量化階段, 通過SAR邏輯確定整數部分N, 如圖4(a)所示, 細量化階段如圖4(b)所示. 以粗量化階段得到結果作為細量化的基準, 將量化范圍縮小至N和(N+ 1)之間, 從而可以使用Sigma-Delta ADC以更高的分辨率確定小數部分n. 通過粗量化階段, 縮小了細量化階段的量化范圍, 降低了對Sigma-Delta ADC的分辨率的要求, 因此只需使用一階Sigma-Delta電路.

圖4 縮放式ADC的量化過程示意圖Fig.4 Block diagram of the quantification process of Zoom ADC

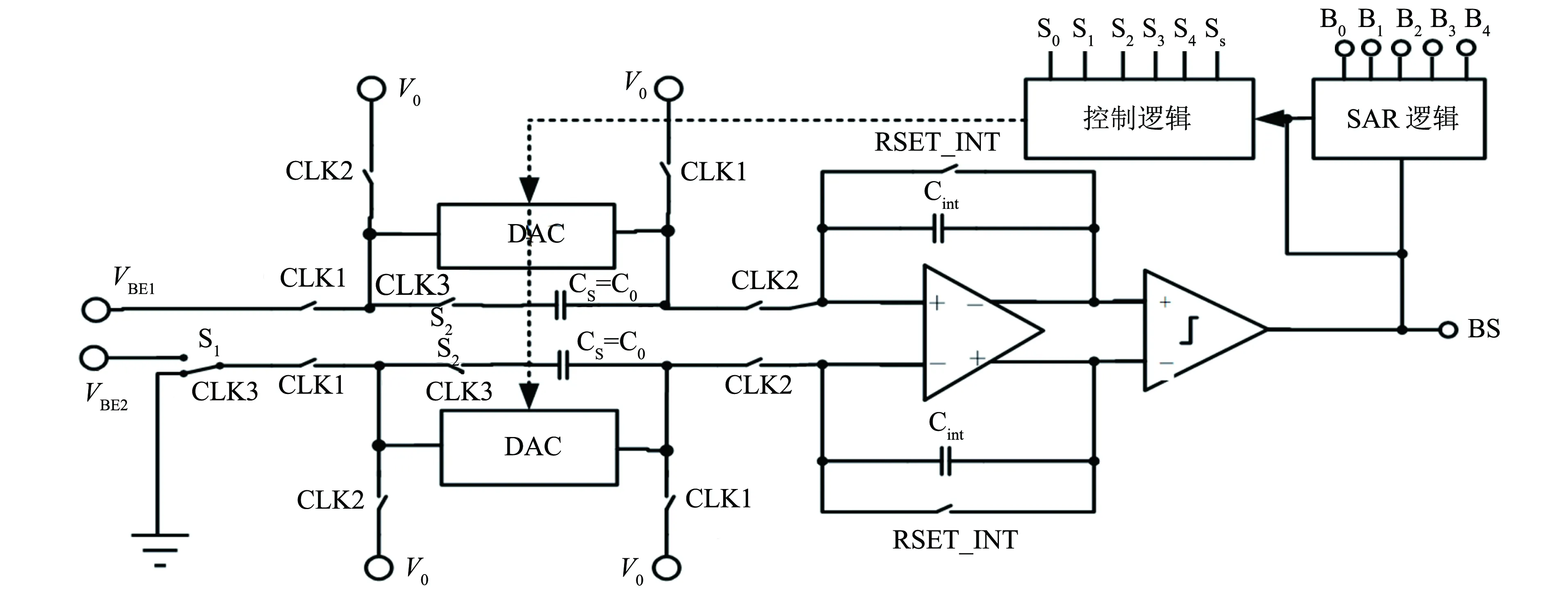

設計的縮放式ADC電路結構如圖5所示, 整個ADC分為采樣保持電路、 積分電路、 比較器和邏輯電路, 通過共用一個積分電路將SAR、 Sigma-Delta ADC兩部分結合在一起, 降低了系統的復雜度和電路的功耗.

圖5 ZOOM ADC的電路結構Fig.5 Circuit diagram of the ZOOM ADC

高溫條件下, 開關的泄漏電荷會變得更嚴重. 特別考慮所采用的CMOS互補開關尺寸, 利用PMOS、 NMOS的泄漏正負電荷相互抵消以降低對積分電路的影響. 同時設計高靈敏度的比較器, 使其在低溫下仍可以分辨很小的電壓差以獲取正確比較結果, 由此提高在高低溫下的量化精度.

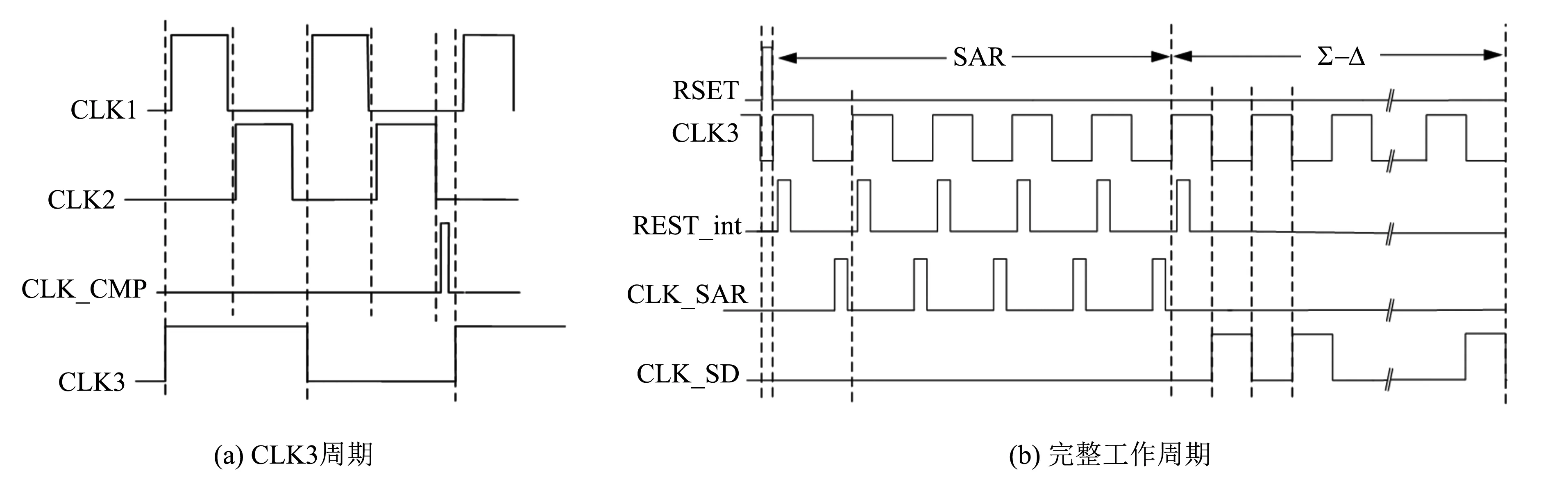

Zoom ADC在相關的控制時鐘信號驅動下對輸入信號進行量化. 如圖6(a)所示, CLK1、 CLK2是一對非交疊時鐘信號, 當CLK1=1, CLK2=0時, CLK1開關導通, CLK2開關斷開, ADC 工作在采樣模式, 采樣電容CS(或電容陣列)對輸入信號進行采樣. 當CLK1=0, CLK2=1時, 電路工作在積分模式, CS(或電容陣列)上的電荷將轉移至積分電容Cint上. 當CLK3=1時, 開關S1接到地, 此時的輸入信號為VBE1, 開關S2接通, 通過采樣電容CS進行采樣和積分. 而當CLK3=0時, 開關S1接至輸入端, 此時的輸入信號為(VBE1-VBE2= -ΔVBE), 開關S2斷開, 電容陣列在邏輯控制電路下接入電路的電容值如下式所示, 并以這些電容對-ΔVBE進行采樣積分, 在對兩個信號進行積分采樣后, 比較器將進行一次比較操作, 得到VBE1與k·ΔVBE的大小比較結果.

圖6 縮放式ADC的時序圖 Fig.6 Timing diagram of zoom ADC

(S4×24+S3×23+S2×22+S1×21+S0×20+SS)C0

(12)

ADC完整工作周期包括了SAR階段和Σ-Δ階段, 如圖6(b)所示. 其中, SAR階段為5個CLK3周期. 在每個CLK3周期開始時, 積分電容都要進行復位清零, 再開始采樣和積分, 并在積分電路完成積分和比較后, CLK_SAR時鐘將驅動SAR邏輯獲取比較器的輸出, 從而確定SAR邏輯的輸出B4~B0. 此階段CLK_SD保持為零, 令SS保持斷開, 以公式(12)所示方式控制電容陣列中接入對應個數的采樣電容. 在此后的256個CLK3周期則是Σ-Δ階段. 僅在一開始對積分電容進行一次復位清零, 由于SAR邏輯不再變化, 因此S4-S0開關狀態也將保持不變. 而開關SS將根據前一周期的比較結果BS變化, 對-ΔVBE采樣的電容個數為N(BS=0)或N+1(BS=1), 如果此階段比較器的輸出占空比為φ. 根據Σ-Δ基本原理, 有:

由公式(13)可知, 通過求得Σ-Δ階段的比較器輸出BS的占空比φ, 即可求得VBE與ΔVBE比值的小數部分. ADC的出量化值X為:

X=B4×24+B3×23+B2×22+B1×21+B0×20+φ

(14)

3 芯片版圖設計與電路仿真結果

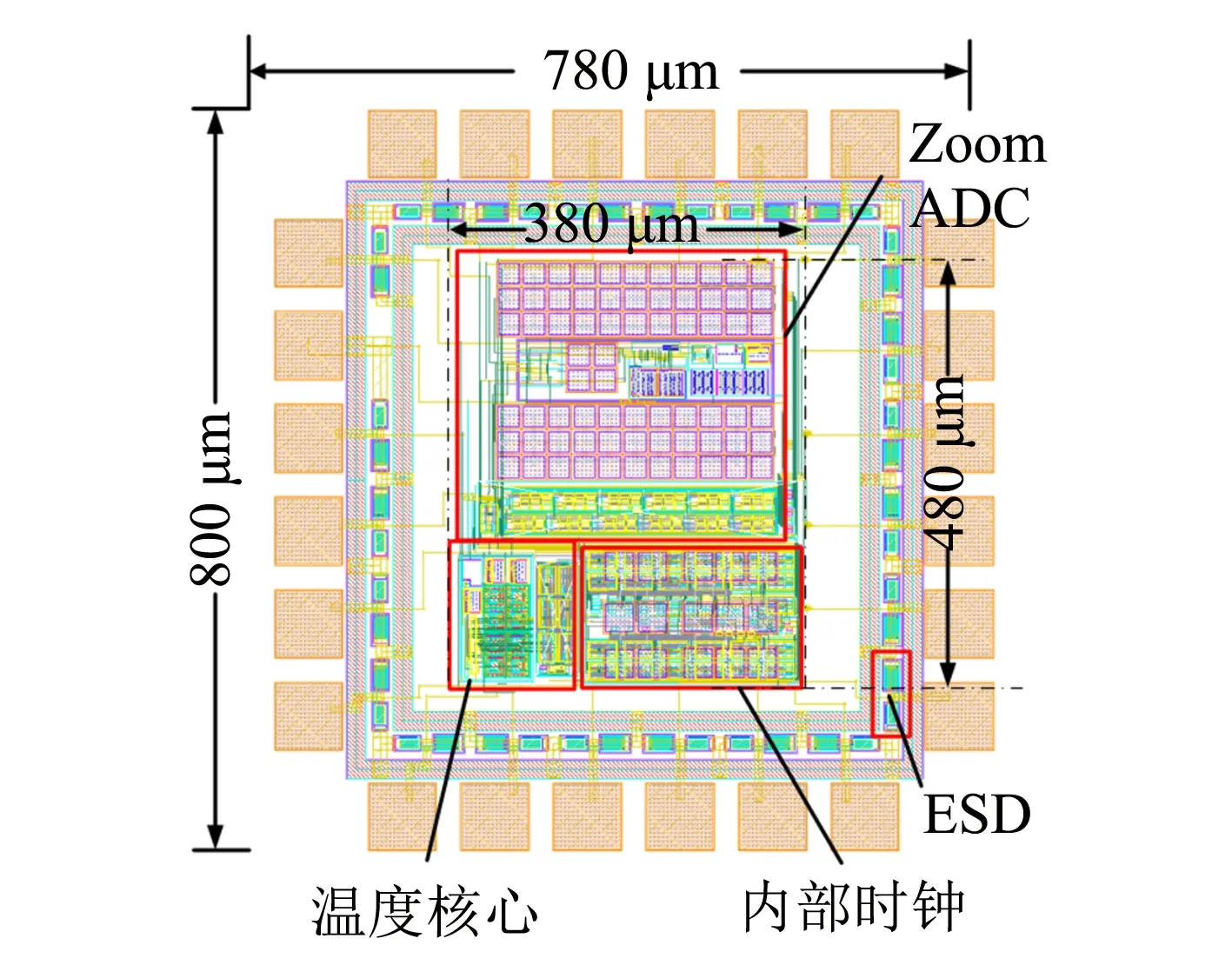

芯片的完整版圖如圖7所示, 總面積780 μm × 800 μm, 其中核心面積為380 μm × 480 μm, 小面積有利于與頻率源等電路實現片上集成.

圖7 電路版圖Fig.7 Layout of the circuit

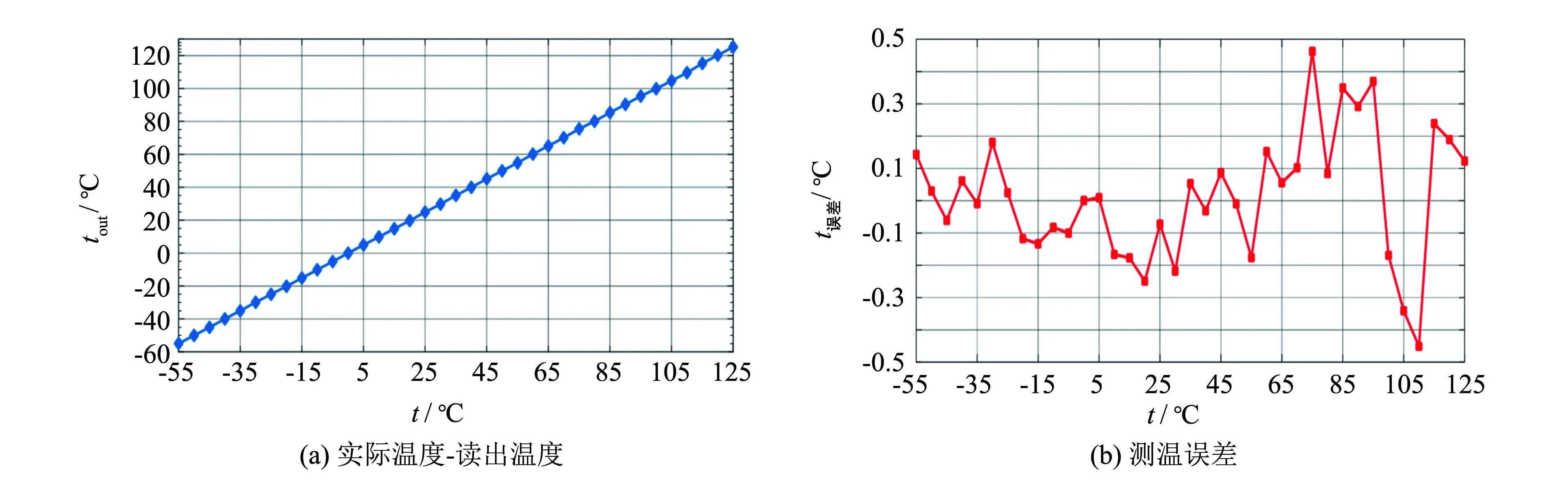

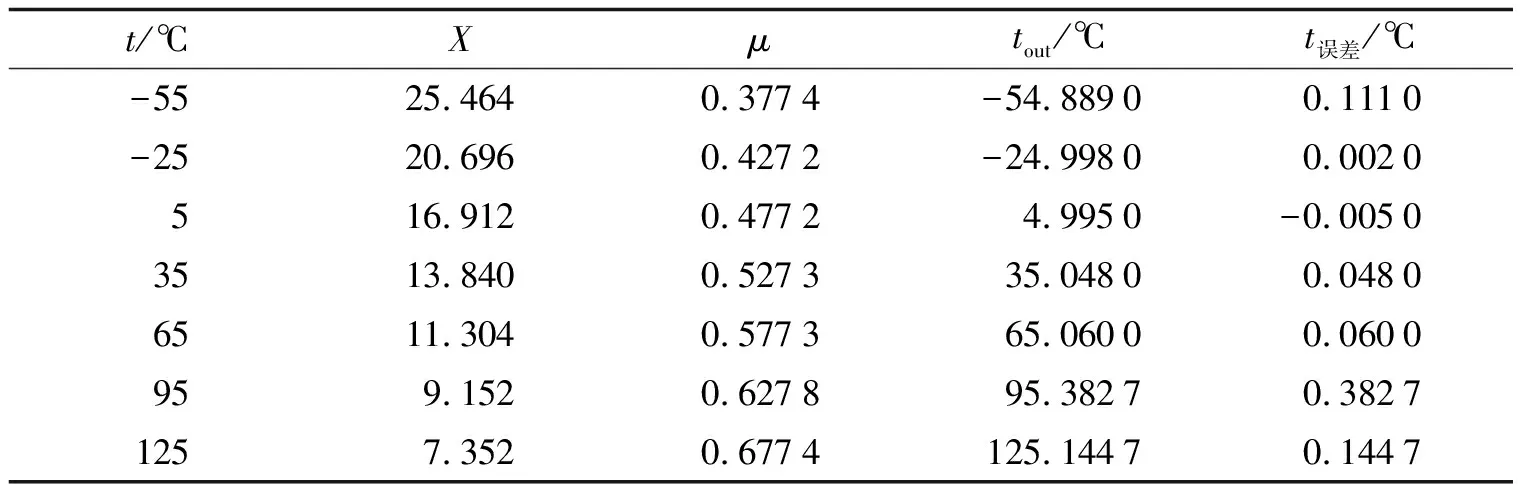

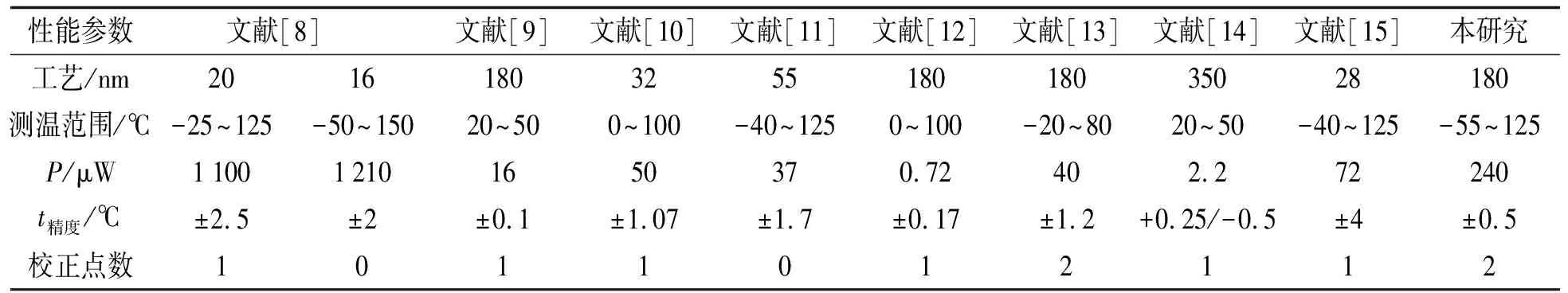

在不同溫度點下對設計的溫度傳感器進行仿真, 根據式(14)計算得不同溫度下的X值, 通過公式(7)計算得到相對應的μ, 并將在-55和125 ℃ 兩個溫度點獲取的μ代入式(8)求得換算系數A、B, 再將A、B代入-55~125 ℃范圍的其他溫度點的數據計算, 得到讀出tout和t誤差如圖8所示, 部分溫度點下測量和計算的數據如表1所示, 而與部分BJT基CMOS溫度傳感器的性能對比如表2所示.

圖8 測量結果 Fig.8 Measure results

表1 不同溫度點下的測溫數據及誤差

表2 CMOS溫度傳感器性能比較

4 結語

基于雙極型晶體管的溫度特性, 采用TSMC 0.18 μm CMOS工藝設計了一種BJT基的片上CMOS溫度傳感器. 仿真結果表明, 在1.8 V的電源電壓下, 電路的平均功耗為240 μW, 在-55~125 ℃的測溫范圍內, 經兩點擬合校正后的溫度測量誤差小于±0.5 ℃, 能夠與頻率源電路實現片上集成并提供較為精確的溫度信號.