以雙斜積分控制器為例談EDA教學實例設計

陳李勝 孔文浩 黃文勇 胡去峰 陳 卉

(電子科技大學中山學院 廣東中山 528402)

一、雙斜積分式ADC

雙斜積分式ADC的工作原理是將輸入信號轉換成時間(脈沖寬度信號),輸出值正比于輸入信號在采樣時間內的平均值,然后由計數器獲得數字值。其優點是雙斜式積分器對積分元件以及時鐘頻率的精度要求不高,具有很強的串模干擾能力。但缺點是轉換精度依賴于積分時間,因此轉換速率較低。雙斜積分式ADC是積分式ADC的一種,圖1給出了中雙斜積分式ADC原理圖。

圖1 雙斜積分式ADC原理圖

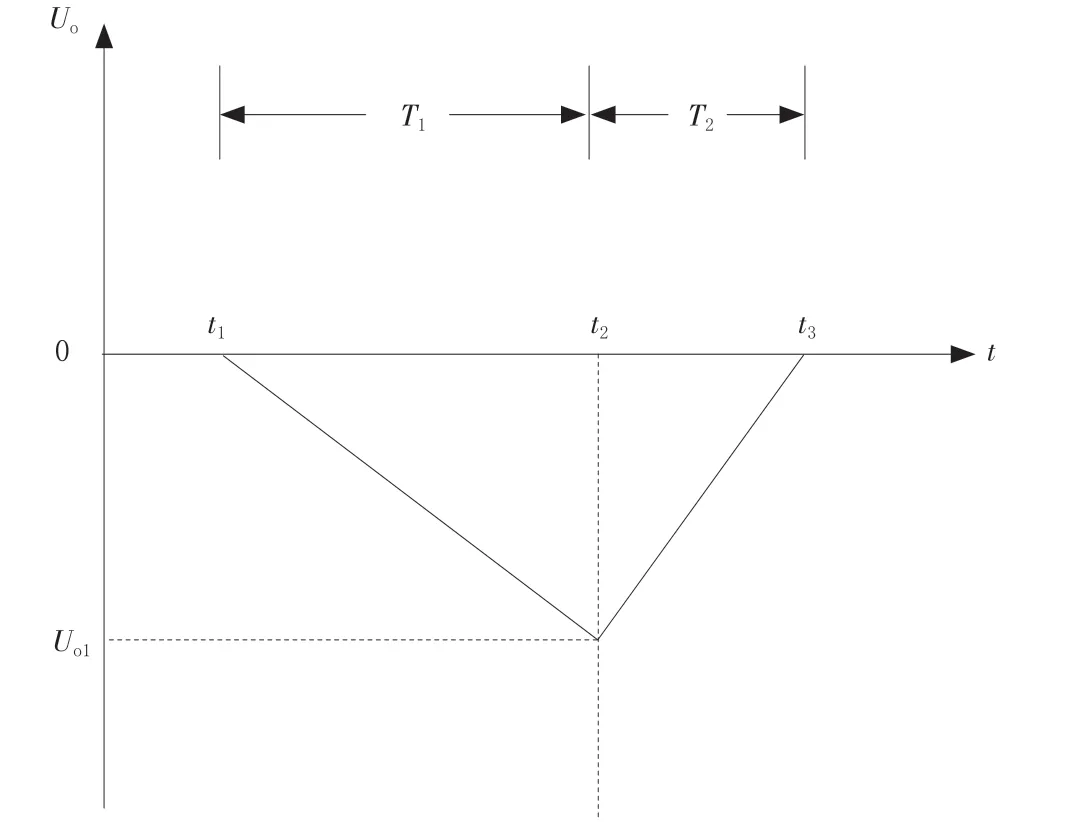

當進行AD轉換前,計數器未使能計數,并接通S2使電容完全放電,此時積分器的輸出波形如圖2的0-t1時間段。轉換開始后,斷開S2,此時整個轉換過程分為兩個階段進行。

圖2 雙斜積分式ADC輸出波形

(一)第一階段,對待測電壓做固定時間的積分U1

令開關S1置于待測電壓V1端,積分器對待測電壓V1進行固定時間T1的積分,積分器的輸出波形如圖2的t1-t2時間段。積分結束時積分器輸出電壓為:

從上式可以看出,積分器的輸出Uo1與U1成正比。這個過程是轉換電路對輸入信號的采樣過程。在采樣開始的時候,CPLD控制使能計數,當計數器到達N1時,這個時間正好是固定的積分時間T1。此時CPLD狀態機跳轉到下一狀態,令開關S1切換至-VREF端,同時計數器清零,采樣階段結束。

(二)第二階段,對參考電壓固定速率積分

采樣一段結束后,因為參考電壓-VREFEF的極性與U1相反,積分器反向積分,積分器的輸出波形如圖2的t2-t3時間段。此時CPLD使能計數器,經過T2時間,積分器輸出電壓為0,過零比較器輸出高電平,CPLD關閉計數器,此時的計數器的計數值為N2。

同時通過CPLD的狀態機控制電路使開關S1與V1相接,重復第一步。雙斜式積分型ADC輸出波形如圖2所示。

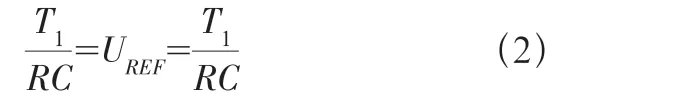

分析雙斜積分ADC的工作原理以及波形可以得到:

根據N1、N2與T1、T2的關系,最終可以得到:

雙積分式ADC的輸出正比于輸入信號的平均值,所以它的優點是工作性能穩定且抗干擾能力強。由公式分析可以看出,積分器的積分過程的時間常數相等,計數器的計數結果與RC無關,所以,該電路對RC精度的要求不高,而且電路結構簡單。

二、雙積分式AD轉換器的EDA實現

(一)狀態機實現控制雙斜積分ADC

有限狀態機(Finite-State Machine,FSM)是表示有限個狀態以及在這些狀態之間的轉移和動作等行為的數學模型。反映從系統開始到現在時刻的輸入變化的狀態。本實例使用VerilogHDL實現狀態機來控制雙斜積分ADC的不同工作狀態。

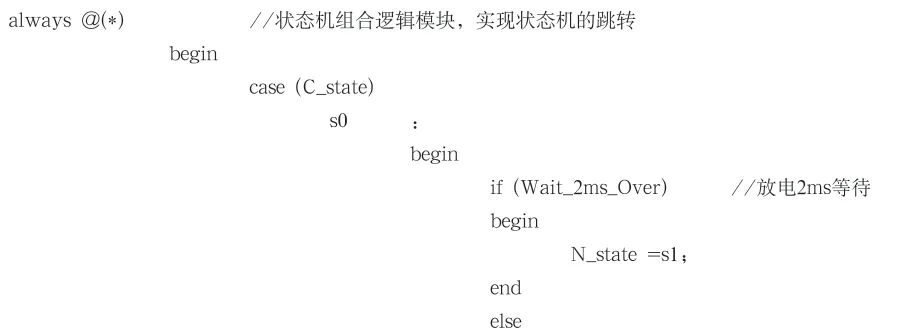

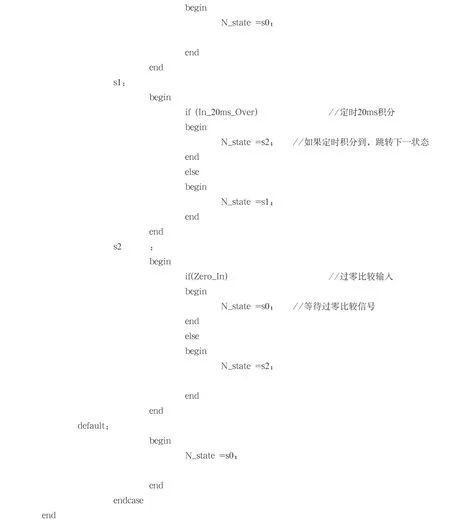

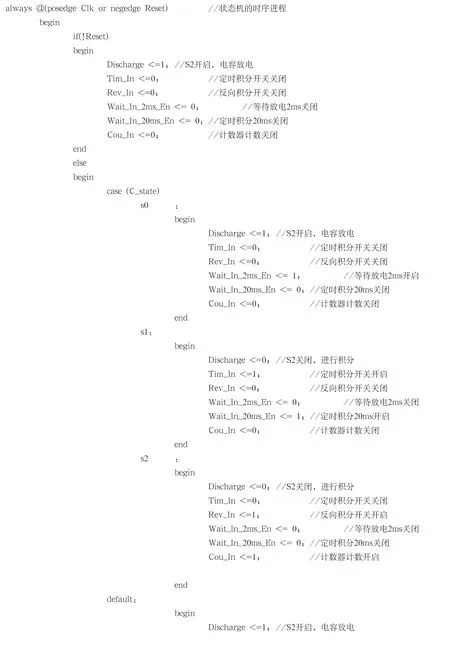

狀態機采用三段式狀態機來進行編寫,第一段用時序邏輯描述C_state(現態)和N_state(次態),第二段用組合邏輯描述狀態轉移,第三段用時序邏輯描述輸出。

第一段用時序邏輯描述C_state(現態)和N_state(次態):

第二段用組合邏輯描述狀態轉移,該模塊主要用來實現三個狀態在什么時候實現狀態轉移。

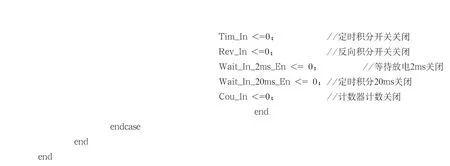

第三段用時序邏輯描述輸出,對應各個狀態時各個控制信號組合邏輯的輸出。

(二)Verilog HDL實現定時器和計數器

本實例所用的主控芯片EPM570T100C5N的工作時鐘是16MHz,經過時鐘分頻產生1KHz的時鐘用于定時器模塊的工作頻率。整個雙斜積分式ADC的定時分為還未進行積分階段的放電階段以及積分階段的定時積分,分別是2ms和20ms。這些定時值通過分頻器的方式產生。

整個雙斜積分式ADC的定時分為還未進行積分階段的放電階段以及積分階段的定時積分,分別是2ms和20ms。為了計數得到反向積分的值,這個時候通過經過分頻產生1MHz的工作頻率,這個頻率用于計數器模塊,求出式3中的N1,N2進而計算出ADC的轉換值。

在進行測試的時候,對每組電壓值都進行多次測量取平均的方式來提高測量精度。

三、結論

狀態機是數字邏輯設計中的重要內容,本身相對復雜。本教學實例結合積分式模數轉換器的控制方法,引入三段式狀態機,更利于學生理解狀態機的寫法和應用。本實例在加深學生理解如何使用狀態機的同時,也能讓學生進一步掌握積分式模數轉換器的控制方法。從教學實踐的結果來看,有較好的效果。如何豐富此教學實例的外圍,讓學生在學習狀態機的同時也學習使用Verilog HDL代碼實現常用外設的控制是下一步豐富教學實例的重點。讓EDA的學習不僅僅是代碼的練習,更是結合實際硬件的綜合訓練。這樣才能培養出更具有工程應用能力的學生。