基于Verilog-A的陀螺儀接口電路模型及行為仿真

范藝暉,孟真,張興成,韓世鵬,吳健文

(中科院微電子所,北京,100029)

關(guān)鍵字:陀螺儀接口電路;環(huán)形二極管解調(diào);Verilog-A;行為級仿真

0 引言

MEMS陀螺儀接口電路起著將傳感器連續(xù)輸出信號讀出的作用。MEMS工藝使傳感器的設(shè)計與制造的小型化成為可能,是構(gòu)建物聯(lián)網(wǎng)的系統(tǒng)的關(guān)鍵技術(shù),極大程度的提高了電子系統(tǒng)的集成度,感知能力以及信息處理能力,一直是各個研究機構(gòu)的研究熱點[1]。尤其是以MEMS陀螺儀為代表的新型傳感器具備的高精度低功耗優(yōu)勢,正以前所未有的速度走進人們的生活[2,3,4],因此設(shè)計出高性能的陀螺儀接口電路具有實際意義和社會價值。然而之前的研究是基于Matlab/Simulink級的數(shù)學(xué)建模[5],且MEMS工藝通常不能與芯片設(shè)計CMOS工藝兼容,陀螺儀與接口電路的設(shè)計過程幾乎是獨立的,不能直接將陀螺儀的機械特性直接帶入到Cadence電路設(shè)計環(huán)境中,這為接口電路的設(shè)計仿真帶來了極大的困難。而當(dāng)前模擬電路設(shè)計過程依舊沿襲著器件子模塊調(diào)用的為基礎(chǔ)的設(shè)計思路。但是在實際硬件設(shè)計調(diào)試時往往需要相應(yīng)的模型數(shù)據(jù)作參照,因此對陀螺儀接口電路的Verilog-A建模與行為級仿真是必要的。

本文主要研究了應(yīng)用于MEMS陀螺儀的接口電路,以Verilog-A硬件描述語言為基礎(chǔ),在Cadence平臺上設(shè)計建立了陀螺儀接口電路的行為級模型,并進行了仿真實驗。文中采用開環(huán)調(diào)制結(jié)構(gòu)將陀螺儀的微小電容變量轉(zhuǎn)化為電壓變化,再經(jīng)后級系統(tǒng)處理,實現(xiàn)了陀螺儀接口系統(tǒng)的整體行為級仿真。系統(tǒng)中包括如陀螺儀可變電容模型,環(huán)形二極管解調(diào)結(jié)構(gòu),增益放大,以及低通濾波電路。并研究了在不同載波頻率,增益,電容變化量情況下,系統(tǒng)的輸出精度和穩(wěn)定性。電路輸出電壓的幅值,線性度,建立時間也被納入實驗設(shè)計中。通過研究這些在模擬前端中的實驗現(xiàn)象,為進一步探明陀螺儀接口模擬前端中的性能折中關(guān)系提供了參考和設(shè)計指導(dǎo)。

1 MEMS陀螺儀信號讀出原理及Verilog-A行為級模型設(shè)計

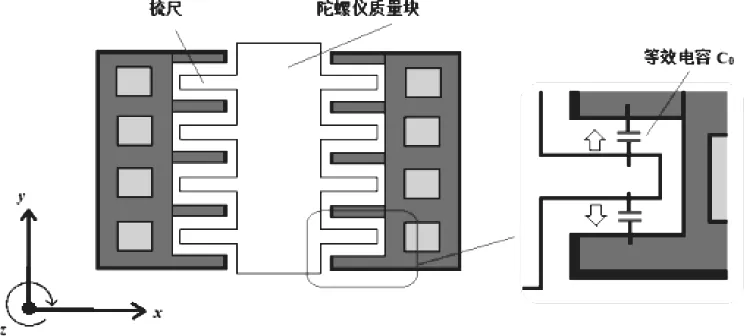

陀螺儀是一種測量物體運動變化量的傳感器,它將物體的空間方位變化量轉(zhuǎn)化為電信號,實現(xiàn)對物體的姿態(tài)控制,空間定位,軌跡追蹤的目的[6,7]。常見的陀螺儀功能有陀螺方向儀,陀螺羅盤,陀螺垂直儀,陀螺穩(wěn)定器,速率陀螺儀。由于MEMS電容式陀螺儀原理簡單且應(yīng)用范圍最廣,本文的研究也是基于此展開。經(jīng)典的電容式MEMS的結(jié)構(gòu)如圖1所示,由梳齒,質(zhì)量塊,以及相應(yīng)形成的電容上級板,下級板組成。

圖1 MEMS陀螺儀微結(jié)構(gòu)簡化圖

MEMS陀螺儀微結(jié)構(gòu)在X方向振動時,若Z方向有角速度輸入,則Y方向由于哥氏力效應(yīng)產(chǎn)生加速度,引起傳感器梳齒沿著Y方向振動,等效電容也隨之發(fā)生改變[8]。因此陀螺儀的行為級仿真可簡化為對電容變化量的檢測。而物體受外力運動狀態(tài)發(fā)生改變,陀螺儀檢測電容量發(fā)生變化的物理量在Cadence電路仿真環(huán)境中無法模擬,所以本文中對陀螺儀變化電容量的行為級描述均是以Verilog-A語言來來構(gòu)建的,類似的研究也可以在文獻[9]中找到對加速度計Verilog-A建模方式。由于MEMS結(jié)構(gòu)的微小尺度能夠產(chǎn)生的電容變化量十分有限,本文中對陀螺儀模型定義的主要參數(shù)是靜態(tài)電容,動態(tài)電容,以及電壓控制量。該模型中陀螺儀靜態(tài)電容為C0,動態(tài)電容為△C,則在實際仿真中兩路電路實際檢測電容為

圖2是文中Verilog-A建模的陀螺儀接口電路所采用的實際結(jié)構(gòu)包括電容電壓轉(zhuǎn)換,解調(diào),低通濾波這幾個部分。陀螺儀接口電路模型采用開環(huán)調(diào)制結(jié)構(gòu)實現(xiàn)。因為環(huán)形二極管結(jié)構(gòu)在接口電路中可同時完成對陀螺儀信號的C-V轉(zhuǎn)換以及解調(diào)的功能。其原理為陀螺儀檢測電容由高頻載波進行調(diào)制后,再通過環(huán)形二極管解調(diào)和C-V轉(zhuǎn)換實現(xiàn)對與電容變化量呈正比關(guān)系的直流電壓的讀出,將差分電容量轉(zhuǎn)換成輸出電壓,便可以檢測出角速度[10]。

圖2 開環(huán)調(diào)制結(jié)構(gòu)陀螺儀接口電路原理圖

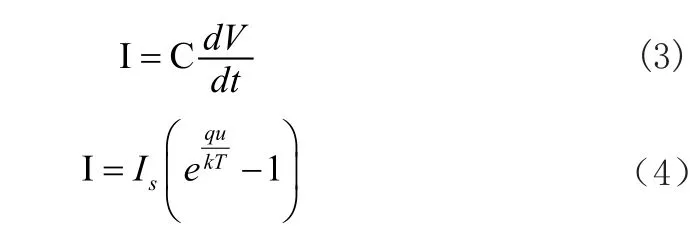

本模型中對可變電容的定義是-電容電流電壓方程(3)實現(xiàn)。在環(huán)形二極管解調(diào)模塊中,二極管行為級模型在Verilog-A中采用肖克萊方程(4)定義,其參數(shù)包括二極管反向電流常數(shù)及開啟電壓等。環(huán)形二極管以及負載CLRL在空間上是對稱的。調(diào)制信號通過環(huán)形二極管,使調(diào)制信號正反相導(dǎo)通,充放電的過程中完成了對信號的解調(diào)以及C-V轉(zhuǎn)換。

放大器模塊的在本模型中有兩處,第一處為二極管解調(diào)后對差動信號進行放大,第二處驅(qū)動有源低通濾波電路,兩者僅在增益倍數(shù)不同。前者的增益直接決定接口電路的電容電壓增益,又處于開環(huán)工作狀態(tài)設(shè)置數(shù)值較小;后者增益較高,可提高模擬低通濾波器的動態(tài)范圍。

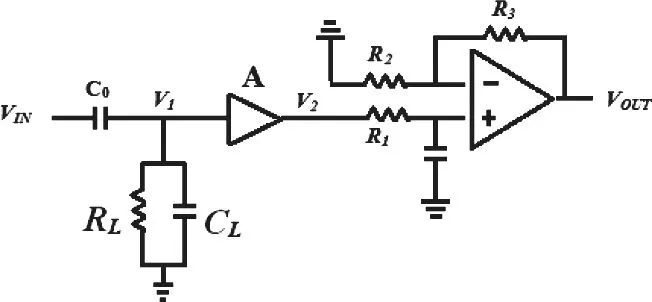

接口電路的簡化模型如圖3所示。由于系統(tǒng)在差分放大器前屬全差分對稱結(jié)構(gòu),故采取半邊電路法分析。在此處對環(huán)形二極管的功能進行了簡化處理,僅考慮其開關(guān)作用。信號通過環(huán)形二極管模塊,依序正反向?qū)ǎ瑢崿F(xiàn)對載波信號的解調(diào)效果。經(jīng)推導(dǎo)系統(tǒng)中CV轉(zhuǎn)換部分的傳輸函數(shù)為

圖3 開環(huán)調(diào)制結(jié)構(gòu)陀螺儀接口電路的簡化模型

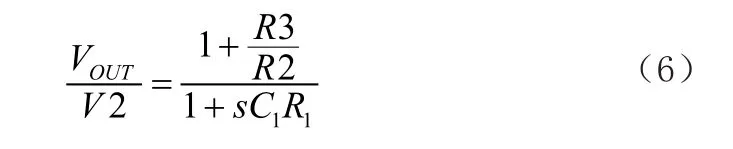

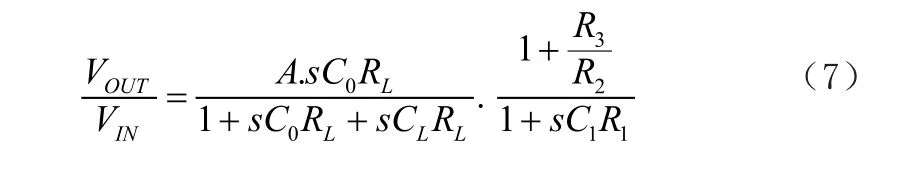

系統(tǒng)中的低通濾波器采用有源RC結(jié)構(gòu)。由于陀螺儀諧振頻率與載波頻率通常相差較大,且經(jīng)過環(huán)形二極管解調(diào)的波形包絡(luò)已經(jīng)可以較為明顯的反應(yīng)出檢測電容的變化趨勢。因此采用簡單的一階濾波器就可以較好的實現(xiàn)系統(tǒng)功能。在模型中采用的低通濾波器截止頻率為32Hz,通帶增益設(shè)定為20dB的增益,傳輸表達式為

為提高該模型的電容電壓增益,在CV模塊與低通濾波器模塊間還增加了增益級A,因此整個模型的傳輸函數(shù)可以表示為

2 實驗與仿真

在搭建好陀螺儀接口電路模型后,本文還進行了相關(guān)實驗來研究驗證陀螺儀接口電路模型的功能,以及電路參數(shù)的變化對輸出結(jié)果精度的影響。

(1)電容量與電壓量變化曲線

實驗為模擬真實條件下陀螺儀接口電路的工作狀態(tài),設(shè)定調(diào)制信號為1MHz的方波,驅(qū)動檢測電容左極板。檢測電容中靜態(tài)電容為1pF,動態(tài)電容為0.1pF,以20Hz的頻率作正弦變化。圖4是檢測電容在仿真中的電壓輸出量,從圖中可以看出受到載波調(diào)制的電容變化信息。經(jīng)過環(huán)形二極管解調(diào)和低通濾波處理后,系統(tǒng)輸出電壓的波形如圖5所示,完整的反應(yīng)出電容的變化趨勢。對圖5的系統(tǒng)輸出電壓信號進行頻域分析,得出該該模型輸出信噪比為88.09dB,說明Verilog-A定義的陀螺儀口電路的行為級模型有著較好的噪聲特性。

圖4 陀螺儀輸出信號

圖5 系統(tǒng)輸出信號

(2)陀螺儀接口電路線性度的測量

在本文設(shè)計的陀螺儀接口電路中,電容的變化量與電路輸出電壓變化量在理想狀態(tài)下呈線性關(guān)系。而這種相關(guān)系受到電路參數(shù)的影響從而會呈現(xiàn)出一定的變化關(guān)系。在本文的行為級仿真中,在未加入電路噪聲,器件非理想因素的情況下,僅從行為級模型入手,研究環(huán)形二極管解調(diào)的陀螺儀接口電路在1Mhz調(diào)制,20倍增益,2pF靜態(tài)電容和0.1pF動態(tài)電容的條件下進行。仿真最終得出電容變化量與輸出電壓變化量的線性關(guān)系如圖6所示。實驗結(jié)果說明Verilog-A定義的電路行為級模型在較廣的電容變化范圍內(nèi),輸出電壓基本與電容變化量呈正比,并測得電路的非線性為-0.0075。所有的實驗結(jié)果均是在電路在行為級仿真中得出的。

圖6 電容變化量與系統(tǒng)電壓輸出

(3)載波頻率與輸出電壓幅值,建立時間的關(guān)系

根據(jù)文獻[11]陀螺儀接口電路電容電壓增益與載波頻率呈相關(guān)系,本文作出了更進一步的實驗,在20倍增益級,2pF靜態(tài)電容,0.05pF固定容差的實驗條件下,在多參數(shù)掃描實驗中將載波頻率由10K提高到1G,得出接口輸出的電壓的幅值并不是與載波頻率單調(diào)提升。實驗結(jié)果如圖7所示。當(dāng)載波頻率達到10MHz輸出電壓幅值達到峰值164mV后,隨著載波頻率的提升輸出電壓的幅值反而下降了。實驗說明載波頻率提高在一定的范圍內(nèi)確實可以增大輸出電壓的幅值。然而在模擬前端中的更高的頻率通常是以更高的功耗和更差的線性度為代價的,這也反映出模擬電路設(shè)計中的折中關(guān)系。

圖7 載波頻率與輸出電壓幅值

然而在模擬前端中的更高的頻率通常是以更高的功耗和更差的線性度為代價的,這也反映出模擬電路設(shè)計中的折中關(guān)系。

載波頻率還與接口電路的建立時間有關(guān)。接口電路對電容量的讀取并轉(zhuǎn)換為電壓是一個動態(tài)的過程,對特定的電容差,輸出電壓需要一定時間才能達到穩(wěn)定。實驗在20倍增益級,2pF靜態(tài)電容,0.05pF容差的實驗條件下,將載波頻率由100K提高到1G測試系統(tǒng)的建立時間。該模型輸出電壓的穩(wěn)定時間通常為3ms,定義在系統(tǒng)輸出電壓達到4ms輸出電壓99%的時長為接口電路的建立時間。因為仿真4ms時輸出電壓已經(jīng)完全穩(wěn)定,且4-10ms的仿真時間內(nèi)輸出電壓的變化范圍小于10ms電壓的十萬分之一。仿真的結(jié)構(gòu)如圖8所示,隨著載波頻率的提升,系統(tǒng)的建立時間不斷下降。但是在這個過程中,載波頻率已經(jīng)提升了1E4量級,而系統(tǒng)建立時間卻僅下降了1E-5s。

圖8 載波頻率與建立時間的關(guān)系

3 結(jié)論

本文對開環(huán)調(diào)制結(jié)構(gòu)的陀螺儀接口電路進行了分析和理論推導(dǎo),利用Verilog-A硬件描述建立了陀螺儀接口電路模型,系統(tǒng)采用環(huán)形二極管解調(diào),放大,濾波的形式,對陀螺儀接口電路進行了行為級仿真。并利用該模型研究了電路增益,載波頻率等參數(shù)對接口電路輸出精度,建立時間,電容電壓增益的影響,實驗證明Verilog-A語言描述的陀螺儀接口電路模型具有良好的噪聲特性及線性度,為硬件電路設(shè)計提供了參考。