基于FPGA和Nios II軟核的紙張測量裝置

張國亮,劉恒,李建勛,董千恒,路家琪

(南京信息工程大學電子信息與工程學院,江蘇南京,210044)

0 引言

隨著時代的發展,紙張已經廣泛應用于人類生活的各個領域。但隨著紙張的廣泛應用,紙張測量計數問題亟需解決方案,目前常見的紙張測量的方案:一是用FDC2214電容傳感器測量紙張電容,通過數據擬合來獲得紙張數量[1]。雖然該方法案傳感器得到的數據快速準確,但是振蕩范圍較小,若超出上限,則無法測量。二是利用多諧振蕩器再通過單片機測頻率[2],此類方法雖然對測量電容大小沒有限制,但是測量頻率的方法通常為測周法和測頻法,這兩種測量頻率的方法極易引入誤差,測量的精度不如第一種方案。結合上述背景,本文以FPGA為控制核心,Nios II軟核為運算核心,從NE555振蕩電路電容與的頻率對應關系,通過等精度頻率測量和數字濾波等算法,精確測量紙張數量并實時顯示和語音播報當前紙張數量,提高了測量的量程、精度以及魯棒性。

1 原理分析及計算

1.1 紙平行板電容器的理論分析

平行板電容器由兩塊相互平行的導體極板,中間夾以電介質構成,結構如下圖1所示。平行板電容器的電容量與兩導體極板之間的相對面積s和電介質材料的相對介電常數εr成正比,與兩極板間距離d成反比。平板電容器電容的計算公式如下:

圖1 平行板電容器模型

式(1)中:s為兩導體極板的相對面積;ε0為真空介電常數;εr為相對介電常數(取決于電介質特性);d為兩導體極板的絕對距離。

假如將紙張(此處使用得力70g的A4紙)填入兩導體極板作為電解質,則該平行板電容器,則變為紙電容器,同理式(1)中的d即為紙張厚度,εr為紙張的相對介電常數,當填入不同紙張數量時式(1)中的相對面積s,真空介電常數ε0,相對介電常數εr均為固定值,則該電容器的電容值僅取決于紙張的厚度,即紙張的數量。

1.2 多諧振蕩器理論分析

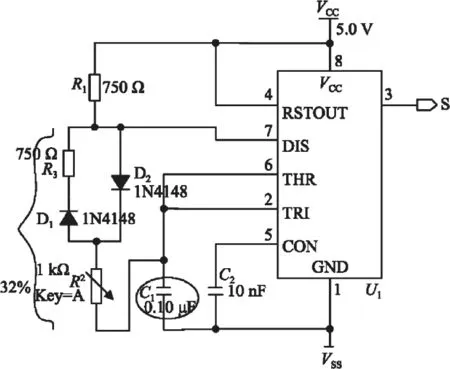

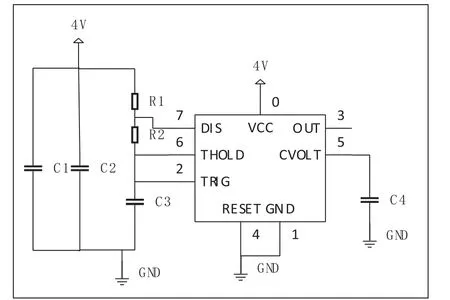

多諧振蕩器電路包括固定電阻R1、R3,電容C1、C2,二極管D1、D2,可變電阻R2及NE555芯片,電源為+5V,電路如圖2所示。

圖2 多諧振蕩器電路圖

圖2中,電阻R2、R3及二極管D1、D2構成等效電阻R。調節可變電阻R2和電容C1即可改變輸出方波的頻率,其中電路輸出的方波高、低電平時間為T1和T2,周期為f,有:

根據上述原理只需改變電容C1的值就可改變輸出方波的頻率,方波高電平為+5V,低電平為0V,方波從S端輸出[3]。

1.3 等精度頻率測量理論分析

現有測頻式紙張測量裝置,測量頻率的方法為測頻法和測周法,當待測信號頻率較低時采用測周法,當待測信號頻率較高時采用測頻法。測周法的誤差主要來源于基準時鐘信號和計數值,其次在閘門開始時,計數器不一定開始工作。測頻法的誤差主要來源于閘門時間,并且測量頻率越低相對誤差越大,實際工程中常將兩種方法結合來使用,但精度依舊不能滿足該類裝置的要求。

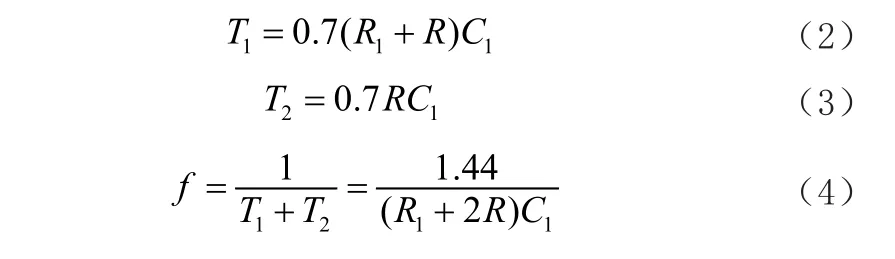

相較于上述兩種測量頻率的方法,等精度頻率測量的最大特點是門控信號不唯一,門控信號是隨著被測信號頻率改變而改變的,該方法不僅測量精度高,而且在所有頻率測量精度都一樣,滿足本裝置的要求。在實際測量時,只需要將待測信號接入FPGA,利用D觸發器將待測信號打兩拍,異步信號轉為同步信號,然后FPGA兩個計數器開始計時工作,計數器1采集待測信號的上升沿數,計數器2采集此時的時鐘信號的上升沿數。當計數器1計數到NX時,計數器1、2同時停止工作,此時計數器2的計數值為NCLK,假設FPGA的時鐘頻率為F,則待測信號的頻率計算:

2 系統方案

將兩塊金屬極板分別粘貼在兩塊亞克力板上,并保持金屬板上下對齊,將一定數量的A4紙放入兩極板并夾緊,FPGA對當前多諧振蕩器頻率的輸出信號進行采集運算,計算出的諧振頻率通過串口通信,送給FPGA內部的Nios II軟核進行數據的處理和分析,最終能夠計算出當前的電容值和紙張數量以及判斷當前電容是否短路,并將結果顯示在TFT屏幕上,同時將分析所得結果傳輸給FPGA,通過FPGA驅動語音播報模塊,進行實時語音播報。測量裝置如圖3所示。

圖3 測量裝置總體框圖

3 系統設計

3.1 系統實物結構

將兩金屬極板粘在兩塊亞克力板的相同位置上,再將兩塊亞克力板對齊,再亞克力板的四角鉆孔,利用銅柱固定兩塊亞克力板的相對位置,使得每次測量時極板的相對位置不發生改變,同時將亞克力板墊高,遠離桌面避免噪音以及電磁干擾。兩金屬極板通過SMA射頻頭連接屏蔽線接入圖7的NE555多諧振蕩器中,多諧振蕩器中R1=R2= 2 00K?,TFTLCD通過排母接入FPGA,語音播報模塊通過杜邦線與FPGA相連,最終構成了整個系統。

3.2 硬件設計

3.2.1 FPGA

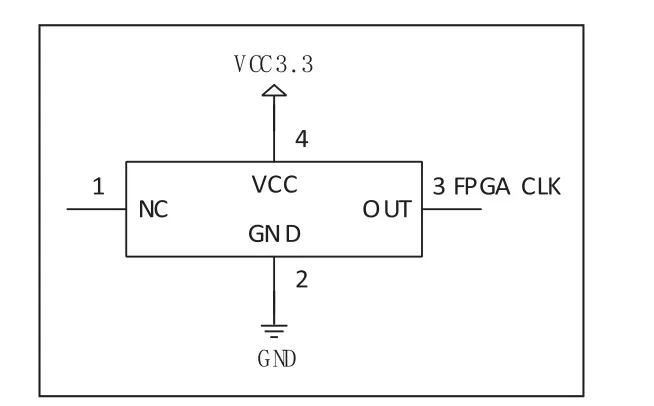

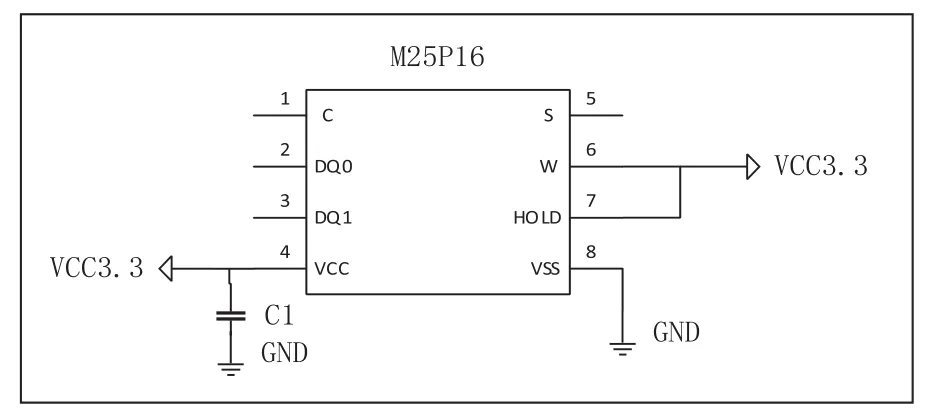

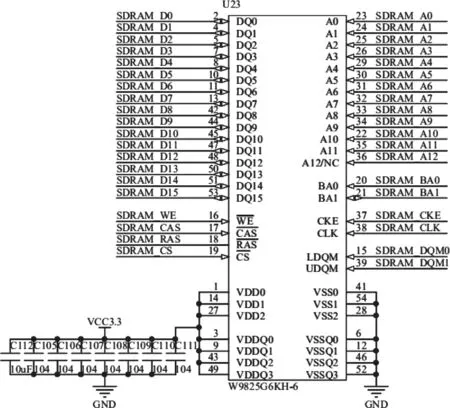

本裝置選用ALTERA公司的Cyclone IV系列FPGA,具體芯片型號為EP4CE10F17C8,如圖4所示FPGA的時鐘為50MHz,搭載了FLASH、SDRAM等豐富的外設資源。如圖5和圖6所示,FPGA外接了M25P16芯片和W9825G6KH芯片,M25P16芯片是一款帶有先進寫保護機制和高速SPI總線訪問的2M字節串行Flash存儲器,W9825G6KH芯片是一款256M字節的DDR存儲芯片,以上兩個芯片為FPGA運行Nios II軟核奠定了基礎。

圖4 FPGA時鐘

圖5 FLASH原理圖

圖6 SDRAM原理圖

3.2.2 多諧振蕩器

本文裝置多諧振蕩器原理圖如圖7所示,該電路以NE555為核心,包括電阻R1、R2及電容C1、Cx,其中中Cx為待測的紙電容器。紙電容器兩端通過射頻線接入電路中。圖7電路在圖2的基礎上進行了簡化,并在電源與地之間增加了105電容和104電容,通過兩個電容對電源進行濾波,濾掉電源的高頻雜波,消除了輸出方波上升沿時的毛刺,便于后續FPGA對輸出波形頻率的計算。

圖7 多諧振蕩器原理圖

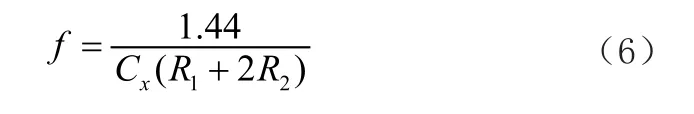

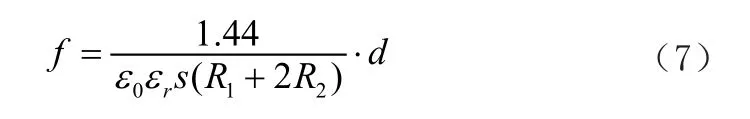

由于R1,R2為定值,則可由式(6)得出,多諧振蕩器的振蕩頻率僅由紙電容器電容值所決定。由式(1)、(6)式得:

由式(7)得:多諧振蕩器的振蕩頻率與紙張數成正比。已知一張A4紙的厚度約為,在理想條件下,忽略紙張之間空隙的影響,可求得電容器每怎加一張紙,其電容上升2.77× 10-9F,振蕩器頻率約增加866Hz 。

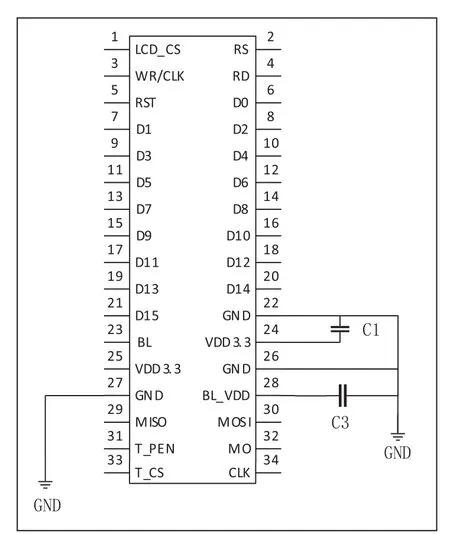

3.2.3 TFTLCD屏

本裝置選用4.3寸TFTLCD電容屏其接線方式如圖8所示,通過FPGA的Nios II軟核驅動該屏幕,在屏幕上顯示當前諧振頻率和紙張數量,當兩極板短接時會顯示報警信息。

圖8 TFTLCD接線方式

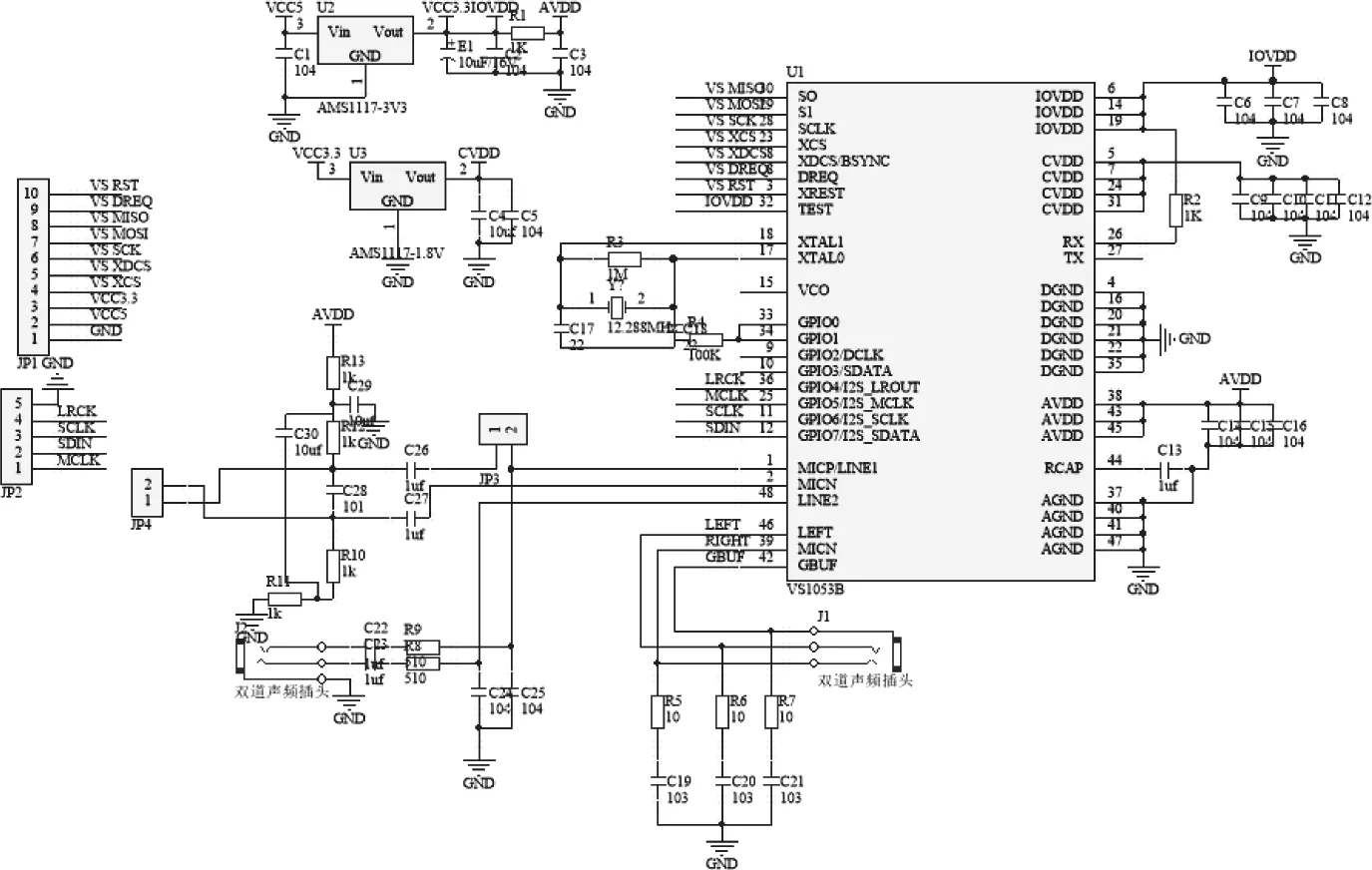

3.2.4 語音播報模塊

本裝置選用了以VS1053B芯片為核心的語音播報模塊,該模塊的電路如圖9所示。當Nios II軟核將數據傳輸給FPGA后,FPGA可以驅動該模塊播報當前諧振頻率和紙張數量,當兩極板短接時,會發出相應的語音提示。

圖9 語音播報模塊電路原理圖

3.3 軟件設計

3.3.1 系統軟件設計

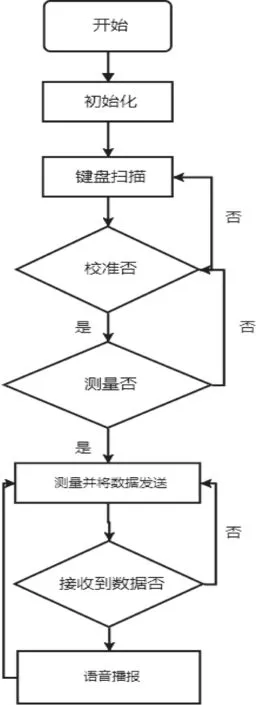

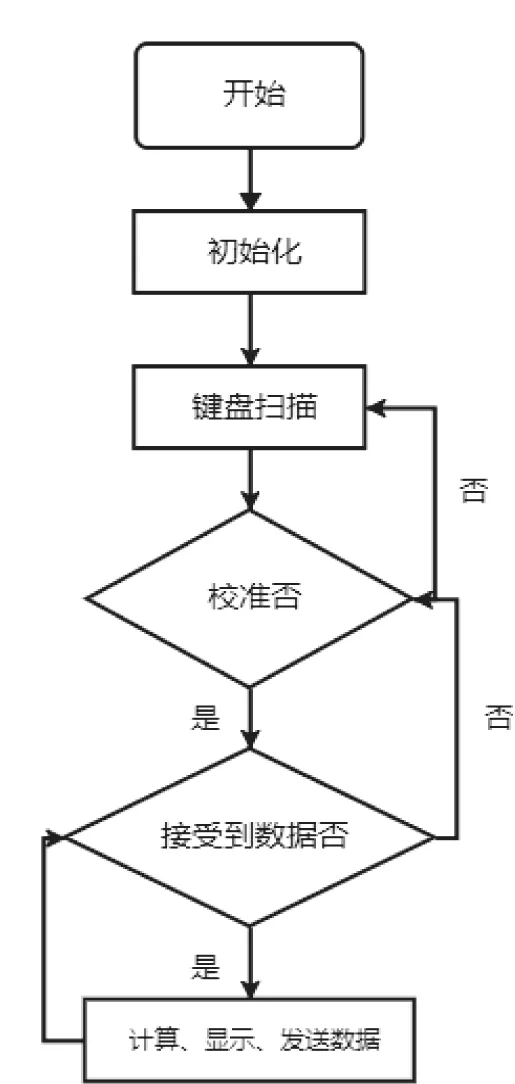

本軟件設計是在quartus II環境下,用Verilog和C語言進行編寫的,FPGA工作流程如圖10所示,Nios II軟核工作流程如圖11所示。

圖10 FPGA工作流程圖

圖11 Nios II軟核工作流程圖

軟件的工作流程:系統上電后,所有功能模塊初始化,當功能初始化結束,接著通過按鍵進行自檢驗校準,防止不同環境溫濕度對紙張測量結果的影響。校準完成后,將校準數據進行存儲,并以校準數據制作查找表用以判斷相同規格的紙張的數量。正式測量時,將某一數量的紙張放入兩極板內壓緊,之后FPGA將進行等精度頻率測量,測量結束后將測量所得的頻率值傳輸給Nios II軟核進行浮點數計算,Nios II計算完后將直接驅動TFT顯示當前紙張數量,同時將數據傳輸給FPGA用以驅動語音播報模塊進行紙張數量播報或發出報警。

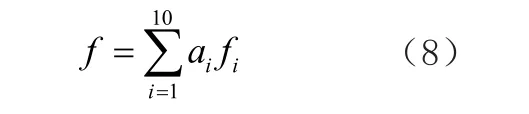

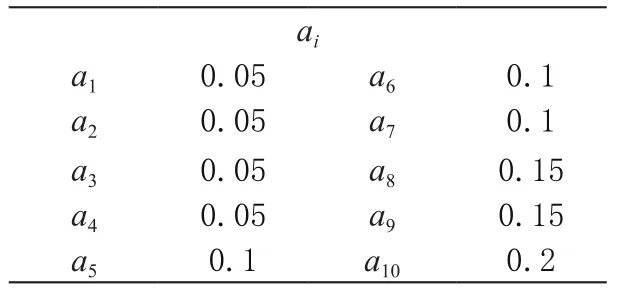

3.3.2 卡爾曼數字濾波

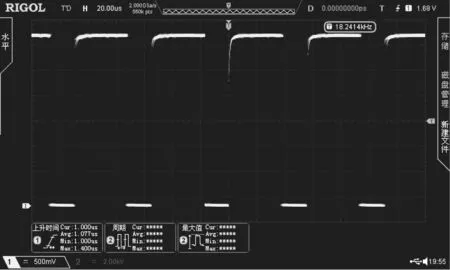

由于實際制作的紙電容器具有邊緣效應等情況,Cx的值是一個波動的值,則多諧振蕩器的諧振頻率也是一個不穩定的值,其波形如圖12所示。頻率不穩定,則會影響校準和測量的結果,為了避免這一現象對數據的影響,在數據計算時采用了卡爾曼數字濾波算法,利用FPGA采集10次諧振頻率,頻率值用f(ii為采集次數)來表示,fi對應權重為ai,ai取值見表1。處理后的諧振頻率表示如下:

表1 權重ai的取值

圖12 多諧振蕩器實際輸出波形

4 測試

4.1 正常環境測試

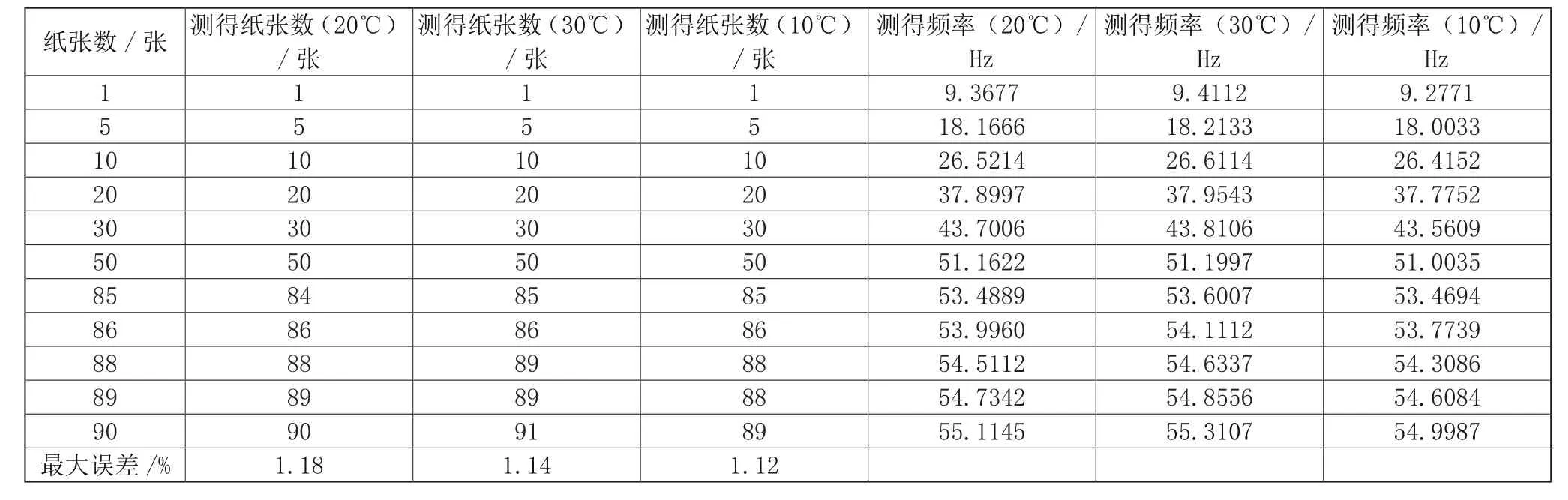

在室溫條件下,將一定數量的A4紙放入兩極板中并夾緊,測量區間為1-90張紙,讀取TFT屏幕上的數值或者記錄語音播報的數值,同時讀取示波器上的頻率,將1-90張紙的部分數據以及誤差分析依次計入到表2中,經過測試本裝置在1-90張紙內最大測量誤差為1.18%,在91-150張紙的最大測量誤差為4.02%。

表2 室溫下測量結果及誤差分析

測試結果分析:當紙張數逐漸增加時,多諧振蕩器的諧振頻率也逐漸增加,但當紙張數量超過一點程度時,雖然依舊呈現上升趨勢,但是線性分布以及不夠明顯。由式(3)可得,頻率應該與紙張數量成正比,但是由于紙張的邊緣效應等客觀因素,實際測試結果并非線性,但通過上述的卡爾曼數字濾波算法以及自檢驗的過程,測量1~90張紙的誤差可以控制在1.18%以內。

4.2 裝置抗干擾測試

由于熱漲冷縮原理,紙張的厚度在不同的溫度下是不同的,所以裝置的魯棒性極為重要,于是將本文裝置在恒溫實驗環境中測試,并將測試結果以及誤差分析記錄在表3中。

表3 不同環境測量結果及誤差分析

由表3可得,本實驗裝置在不同環境下,相同紙張數測量的頻率也略有不同。當環境溫度高時,紙張由于受熱膨脹,每張紙的厚度略有上升,FPGA測得的頻率也相對偏高;當環境溫度低時,紙張厚度略微降低,FPGA測得的頻率也相對偏低。但最后實際計算出來的紙張數量誤差依舊能夠控制在1.18%,故本系統在90張紙的量程內,具有非常好的魯棒性。

5 總結

基于FPGA和Nios II軟核的紙張測量裝置可以完成在一定規格的紙張測量任務,具有成本低,速度快,誤差小,量程廣,魯棒性高的優點。但由于紙張的邊緣效應等導致紙張數量到達一定程度時,線性度不明顯,這一問題對后續紙張測量精度影響較大。這個問題我們會在后續的研究中進一步改進。