基于負反饋技術的嵌套式直流失調消除電路*

張芳玲 ,雷倩倩 ,張旭東 ,李 弦 ,李連碧

(1.西安工程大學 理學院,陜西 西安 710000;2.深圳市紐瑞芯科技有限公司,廣東 深圳 518000)

0 引言

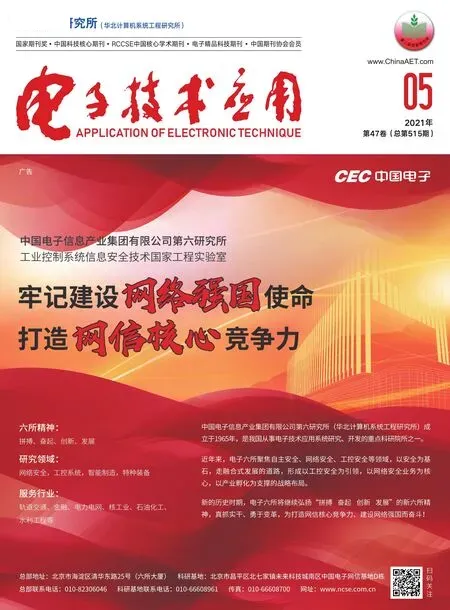

隨著可編程增益放大器(Programmable Gain Amplifier,PGA)放大倍數的增大,尤其在給接收鏈路提供較大增益時[1-3],直流失調的問題就越來越嚴重,使得下一級電路處于飽和狀態。因此,必須使用直流失調消除電路來解決這一問題。常見的直流失調消除技術有四種,一是交流耦合法[4-5],為了得到低的高通截止頻率,需要很大的電阻電容,占用面積大,不易集成;二是數字消除技術[6-8]具有極低的高通截止頻率,分辨率低,需要額外的量化器和數模轉換器,電路實現較復雜;三是前饋消除技術[9-10],由于器件的不匹配等因素,兩路的增益不完全相同且這種方法功耗較大;四是直流負反饋消除方法[11-15],這種方法解決了交流耦合所需要的大電容和數字消除電路的復雜性以及前饋消除方法存在的問題。直流負反饋消除技術如圖1所示,電阻R、電容C和放大器B組成反饋通路,將輸出端out檢測到的直流失調信號轉換成電壓或電流反饋到輸入端in,從而消除直流失調。

圖1 直流負反饋環路

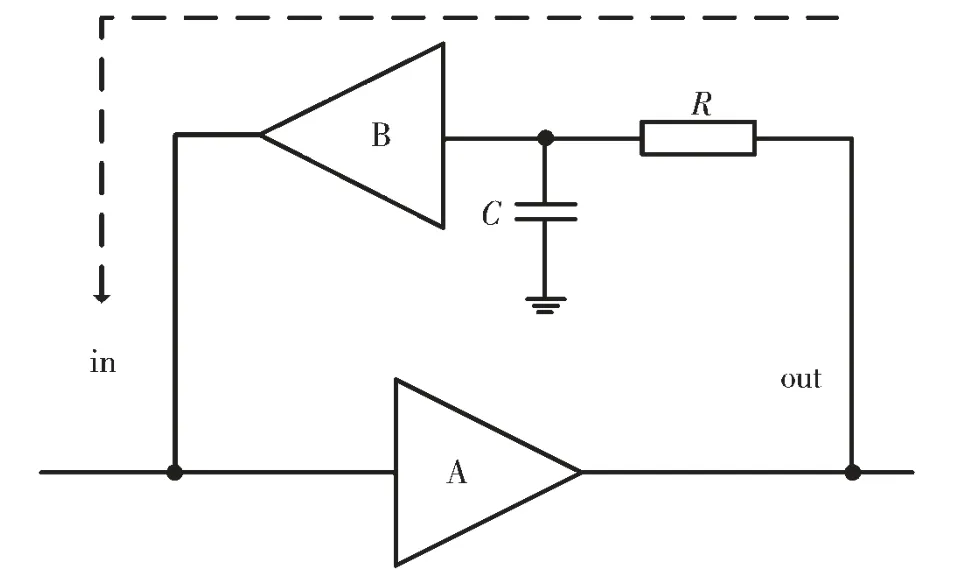

在PGA鏈路中,通常采用多級級聯的方式實現大的可調增益范圍。對于多級級聯的PGA鏈路,采用直流負反饋技術消除直流失調的連接方式有兩種,如圖2所示,圖2(a)中的每一級PGA電路都有一個DCOC環路,而圖2(b)圖中采用多級共用一個DCOC環路的連接方式。圖2(a)中每一級DCOC都有一個反饋運放OP,增大了電路的功耗[14],圖2(b)中單級DCOC可以簡化電路設計和功耗[10],但為了達到與圖2(a)相同的直流失調消除效果,需要更大的面積。針對以上兩種連接方式存在的不足之處,本文提出一種改進的直流失調消除方法,采用了一種嵌套式電路連接方式,將多個獨立的反饋環路通過共用RC組成的低通濾波器和運放OP,再分別通過反饋電阻反饋到每級PGA中,從而減小電路功耗和面積。

圖2 采用直流負反饋技術消除直流失調連接方式

1 基于負反饋的嵌套式直流失調電路

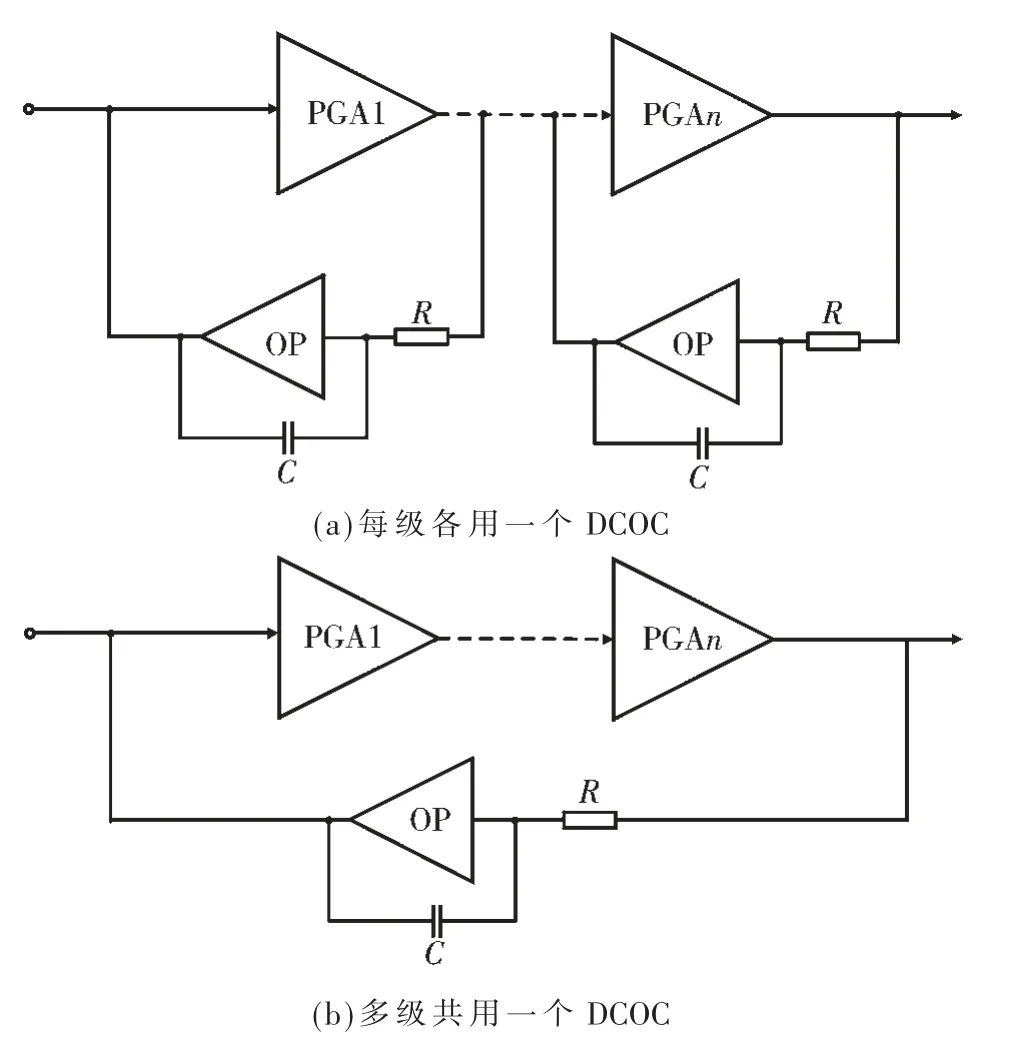

嵌套式DCOC反饋方式的PGA鏈路如圖3所示,PGA電路由兩級PGA1、PGA2構成,每級PGA均采用開關電阻反饋網絡的結構,PGA1增益變化為0~26 dB,第二級增益從26 dB變化到52 dB,增益步長為2 dB,兩級級聯實現52 dB的增益變化范圍。圖3中下方虛線部分為DCOC環路,采用嵌套式反饋的連接方式,將輸出節點Vo2的失調電壓通過電阻R3和密勒等效電容C1組成的低通濾波器檢測,再由運放β 進行放大,一部分通過反饋環路1(FL1),即通過電阻R5轉換為反饋電流,注入到第二級的輸入端;另外一部分通過反饋環路2(FL2)反饋到第一級PGA的輸入端。兩級共用R3、C0和運算放大器β,可變電阻R3實現不同高通截止頻率的切換。C1為密勒等效電容,等效電容C1近似為密勒補償電容C0和運放增益β 的乘積。

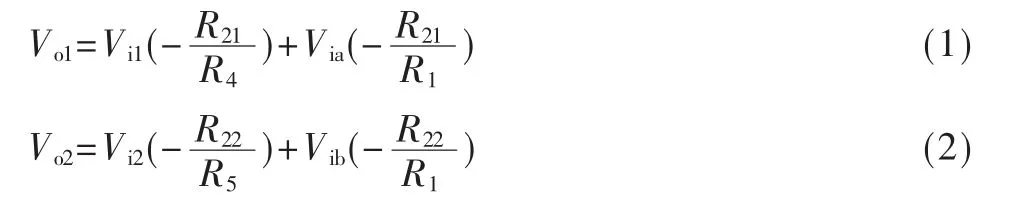

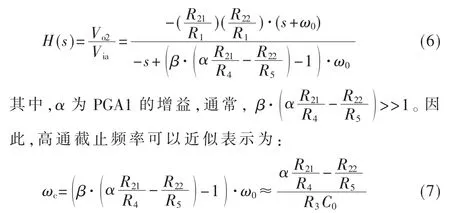

圖3中Via、Vib分別為第一級和第二級的輸入信號,Vi1、Vi2是第一級和第二級的反饋信號,Vo1、Vo2為第一級和第二級的輸出信號,環路FL2和FL1的電壓關系式可分別表示為:

圖3 新型嵌套式DCOC環路

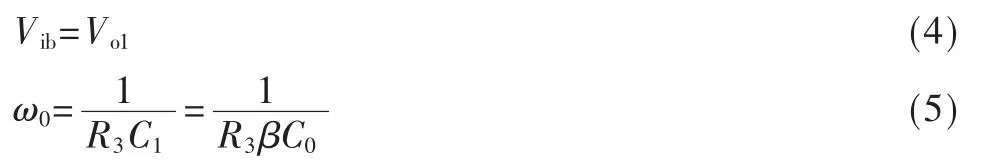

假設反饋運放β 是單級點系統,則:

由圖可知:

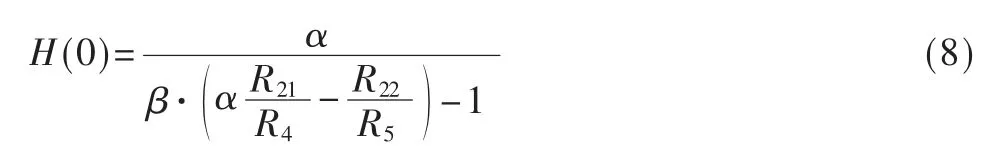

β 為DCOC中運放的增益,ω0為低通濾波器的截止頻率。PGA和DCOC環路的傳輸函數為:

由式(7)可知,高通截止頻率ωc的高低與電阻R21(R22)、R3、R4,R5和電容C0的大小有關。對于PGA1,高通截止頻率與α 和R21/R4的值有關;PGA2的高通截止頻率與R22/R5的值有關,保持α(R21/R4)和R22/R5電阻比值一定時,高通截止頻率保持恒定,即高通截止頻率不隨PGA增益的變化而變化。

由傳輸函數可知,PGA的直流抑制度可表示為:

2 仿真結果

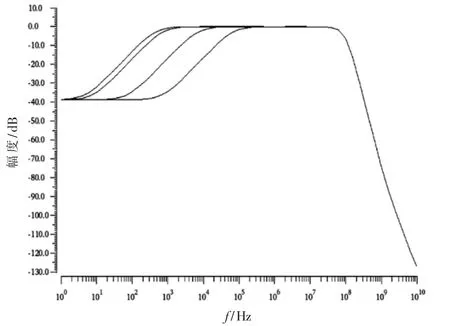

基于UMC 40 nm CMOS工藝,對帶有嵌套式DCOC反饋方法的PGA鏈路進行仿真驗證。圖4為DCOC的高通截止頻率為10 kHz時,PGA不同增益值的頻率響應曲線圖,PGA增益調節范圍為0 dB~52 dB,步長為2 dB,增益誤差小于0.2 dB,1 dB帶寬大于20 MHz。此時α(R21/R4)和R22/R5電阻比值一定,即高通截止頻率恒定,不隨PGA增益的變化而變化,恒為10 kHz,DCOC環路的相對抑制度也是恒定的,大于50 dB。

圖4 PGA頻率響應曲線

圖5為增益在0 dB時,調節電阻R3,反饋環路的高通截止頻率分別為0.5 kHz、1 kHz、10 kHz、100 kHz時的頻率響應曲線。高通截止頻率隨信號變化可以進行切換,這樣可以同時滿足信號完整性和直流失調穩定時間的要求。

圖5 相同增益下不同高通截止頻率

圖6為PGA增益為0 dB時,輸入端加110 mV失調電壓的矯正過程,可以看出,經過DCOC環路矯正后,輸出端的直流失調電壓小于1 mV。

圖6 0 dB時失調矯正過程

表1為DCOC的高通截止頻率為10 kHz,相對抑制度為50 dB時,采用負反饋結構,三種DCOC環路連接方式的比較。從表可以看出,對于兩級級聯的PGA鏈路來說,本文所提出的嵌套式反饋方法與文獻[6]、[9]中的方法相比,在優化功耗的同時,可使DCOC環路的面積減小近一半。

表1 DCOC電路中參數的比較

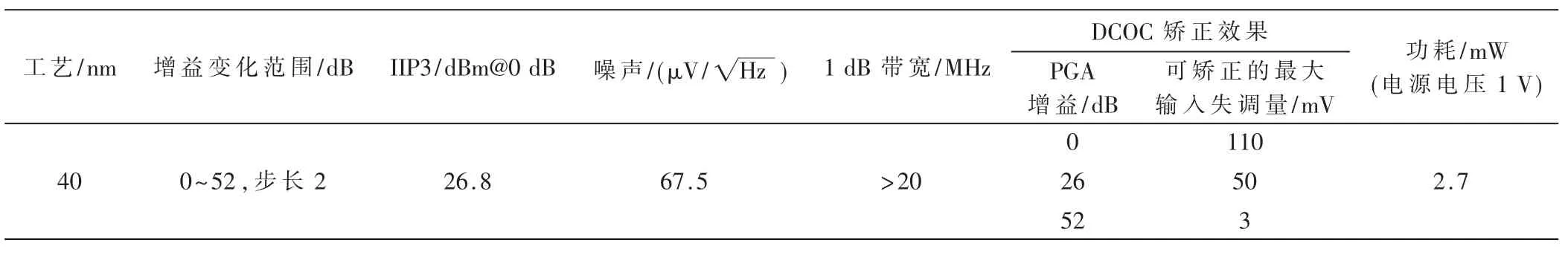

表2 PGA電路性能指標

3 結論

本文在UMC 40 nm CMOS工藝下設計了一種帶有DCOC電路的PGA,DCOC環路采用一種嵌套式電路連接方式,可減小電路功耗和面積。仿真結果表明,PGA的增益變化范圍為0~52 dB,步長2 dB,增益誤差小于0.2 dB,1 dB帶寬大于20 MHz,0 dB下IIP3的值為26.8 dBm,噪聲為67.5 μV/√Hz。加入DCOC環路后,直流失調能夠很好地被抑制,整個電路在1 V電源電壓下功耗為2.7 mW。