基于SystemC語言實現UHF RFID系統自頂向下設計

戚皖青,卜 剛,李姝萱

(南京航空航天大學 電子信息工程學院,江蘇 南京 211106)

0 引言

隨著科技的發展,集成電路的規模變得龐大和復雜,電子系統設計(Electronic System Level,ESL)流程是目前最先進片上系統設計流程方法。

SystemC和Verilog/SystemC Verilog相互結合的方法學為越來越復雜的片上系統設計提供了一套從系統級(system)到RTL級設計的可行性方案。相比于傳統的設計流程,首先采用高級語言來對系統進行設計,之后再采用硬件描述語言對寄存器傳輸級進行設計。應用以上的方法學,使得片上系統的設計過程變得簡單和高效。

射頻識別技術RFID的原理為閱讀器(reader)與標簽(tager)之間以進行非接觸式的數據通信的方式來起到標簽識別目標的作用。

UHF RFID的工作頻率為860 MHz~960 MHz,而UHF RFID空中接口協議ISO/IEC18000-6C是相關標準化組織制定的最新版本[1]。

UHF RFID技術憑借其識別距離遠、傳輸可靠且安全、數據傳輸速率高等優勢,在業界得到廣泛關注[2]。

1 電子系統設計(ESL)方法學

在整個的電子系統設計流程中,首先以電子系統級設計為起點,其中包括的項目分別是選擇體系架構、制定產品規范以及虛擬軟件執行平臺的開發。電子系統設計流程的益處是硬件和軟件能夠并行開發,既繼承已有邏輯設計模塊,又為待設計的新邏輯模塊提供詳細的規格,并提供事物處理級的虛擬模型,為軟件開發任務提供執行平臺原型,而邏輯模塊也可以基于此原型進行驗證[3-5]。在完成電子系統級的設計之后,可以進行RTL的設計和驗證工作,與此同時軟件開發任務也可以同時進行。在上述設計流程中,可以采用高層次綜合工具CatapultC或者Vivado HLS等產生的硬件模型進行RTL級的設計。在此過程中,CatapultC或者Vivado HLS可以直接將高層次設計綜合成RTL級代碼。

2 SystemC介紹

SystemC是以通過采用系統級設計的思想,在結合了軟件算法和硬件實現的優勢之后,對項目工程進行系統級設計,使得系統設計的效率和準確性得到有效提高。SystemC類庫添加進C++之后,對系統級模型開發的實現提供了充分的代碼設計基礎,同時可以快速實現設計的仿真和驗證[6-7]。

SystemC語言包括端口、信號、模塊和進程等,而這些都是硬件描述語言應該具備的基本條件。同時由于特殊庫函數對于時鐘信號的描述,SystemC語言簡化了對時鐘信號的定義[8-9]。

3 系統模型以及標簽不同層次的設計

3.1 系統模型

基于已有的設計理念,一個SoC系統的設計可以劃分為硬件設計模塊和軟件設計模塊。本文根據UHF RFID協議,針對物理層的數據傳遞以及標簽識別層的信息交互,結合ESL軟硬件協同設計的理念以及SoC的設計方法,設計了整個UHF RFID系統模型[10-11]。

基帶通信鏈路設計模塊則是實現物理層相關功能的實現,鑒于SystemC的自頂向下的設計優勢,采用SystemC語言設計實現閱讀器的識別層與標簽的識別層的信息交互,以及閱讀器和標簽的之間的通信鏈路的設計。

3.2 標簽的不同層次的設計

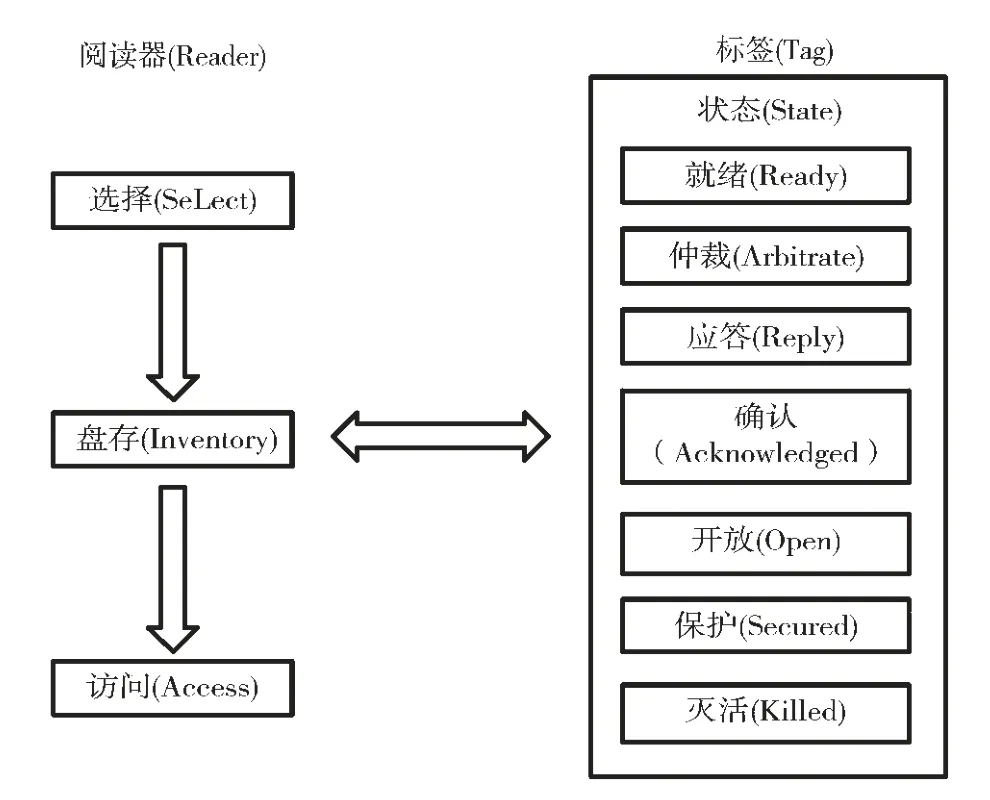

根據UHF RFID的協議標準,對于協議的設計可以分為物理層結構設計和標簽識別層結構設計。在物理層結構的設計過程中,首先實現基帶編碼,生成符合UHF RFID的協議標準的數據包,并且規定數據包格式、數據校驗及編解碼方式、射頻調制方法、射頻包絡參數設定、數據傳輸速率等問題;而主要處理閱讀器與標簽信息交互的各種命令,則是在標簽識別層結構的設計中完成,以函數調用的方式實現命令傳遞,并且通過選擇、盤存和訪問來進行管理標簽群。在協議標簽識別層結構的設計中主要是處理UHF RFID協議的命令體系,標簽相應的狀態轉化[12-13]。協議中不僅對規定的命令和規范做了介紹,還可以保證用戶在預留的空間內,進行自定義相關命令和規范[14]。閱讀器與標簽之間的對應的基本管理操作如圖1所示。

圖1 閱讀器與標簽之間的基本管理操作

3.2.1 標簽識別層設計

根據已有的UHF RFID的協議標準,標簽識別層設計的思路首先是遵循閱讀器的命令,標簽調整到相應的狀態,同時對閱讀器作出應答。在兩者通信過程中,閱讀器處于主動地位,閱讀器主要實現鏈路時序控制部分。在實現標簽識別層的過程中,可以采用設計狀態機的方式進行狀態之間的轉換,具體標簽狀態之間的轉換圖如圖2所示。

圖2 標簽狀態轉換圖

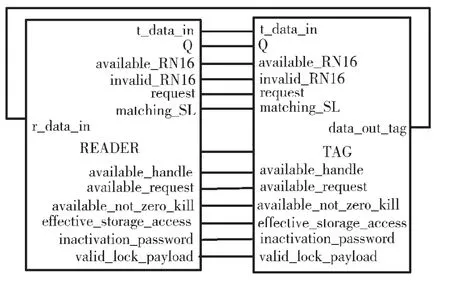

按照狀態圖的轉換過程進行SystemC建模仿真,分別編寫reader.cpp以及tag.cpp文件,在頂層文件里面進行例化和調用,標簽識別層狀態轉換模型圖如圖3所示,實現標簽的不同的狀態之間的轉換,標簽識別層狀態轉換仿真圖如圖4所示。

圖3 標簽識別層狀態轉換模型圖

圖4 標簽識別層狀態轉換仿真圖

3.2.2 標簽鏈路層設計

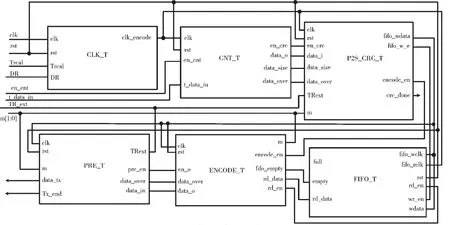

標簽數字基帶發送鏈路,主要實現的是標簽發送信息,閱讀器接收并處理。按照標準協議,標簽的數字基帶部分將處理器要發送的信息編碼為特定的格式傳輸到射頻端。同樣在發送信息的過程中,處理器在數字基帶模塊的寄存器寫進將要發送的數據,數字基帶模塊接收數據和使能信號后按照協議處理數據。發送鏈路需要產生標簽反向散射頻率、數據格式轉化、生成CRC校驗碼、FIFO緩存、FM0編碼和Miller編碼、添加同步碼等模型功能。鑒于以上的設計思路,標簽的數字基帶發送鏈路模型設計如圖5所示。

圖5 標簽基帶發送鏈路

閱讀器數字基帶發送鏈路將數據發送到射頻端后,由射頻模塊發送出去,標簽數字基帶接收鏈路實現射頻信號接收并處理。接收鏈路需要對接收到數據實現檢測、PIE解碼、校驗、格式轉化等操作[15]。

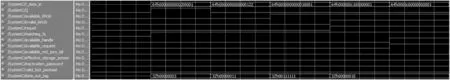

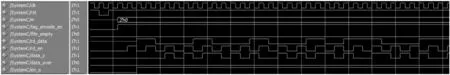

圖6為標簽基帶鏈路ENCODE_T模塊,在Microsoft Visual C++6.0中對數據“1001001001011001”進行fm0miller編碼仿真之后,在Modelsim中查看的仿真波形圖。

圖6 標簽基帶鏈路ENCODE_T模塊波形仿真圖

4 高層次Vivado HLS綜合

Vivado工具為Xilinx公司推出的一款設計套件,主要任務是針對于FPGA開發板的集成化一體式設計。Vivado工具包含了所有產品系列的開發環境,例如芯片級IP核、交叉編譯工具等,開發人員的工作量得到極大的減少,項目開發效率也得到提升[16]。

Vivado HLS是一款高層次綜合工具,可以將C、C++以及SystemC等高級語言綜合成Verilog HDL(HardDescription Language)或VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)等語言,軟件描述的系統模型綜合成RTL(Register Transfer Level)級的代碼。與此同時也大大降低了開發人員的開發設計難度,并且有效地縮短設計周期[17]。

Vivado HLS設計流程如圖7所示,第一步設計具有預期功能的C測試平臺和源代碼。第二步使用C仿真器,例如Microsoft Visual C++6.0來驗證程序實現的函數是否滿足預期的要求。如果C仿真器仿真出的結果滿足當初的設計要求,Vivado HLS工具可以將C生成的算法轉換為相應的RTL級模塊。具體Vivado HLS綜合流程如圖7所示。

圖7 Vivado HLS綜合流程圖

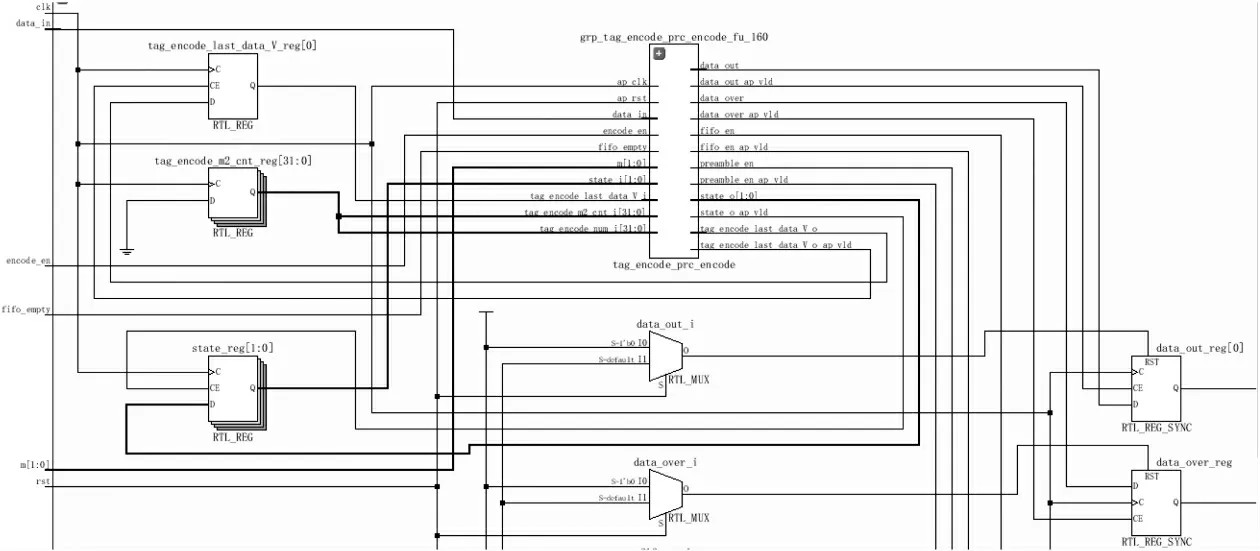

根據程序對算法的編譯生成的RTL_Schematic如圖8所示。

圖8 ENCODE_T模塊Vivado HLS仿真圖

5 結論

ESL設計方法學為規模越來越龐大的集成電路設計提供了有效設計思路和解決方法,具有建模層次高、仿真速度快等優點。采用高層次建模,對UHF RFID標準協議進行從識別層到鏈路層的設計。首先對識別層和鏈路層采用SystemC語言建模,并通過Microsoft Visual C++6.0中對數據“1001001001011001”進行fm0miller編碼仿真之后,在Modelsim中查看的仿真波形,如圖5所示,結果滿足編碼設計要求。完成SystemC設計之后將ENCODE_T模塊導入到Vivado HLS中轉換成RTL電路,實現從高層建模、逐步細化的工作要求。