多通道實(shí)時(shí)偽碼發(fā)生器的設(shè)計(jì)與實(shí)現(xiàn)*

張瀚青,王彥革,李上彥,彭一文,郭銀春,石云墀

(上海航天電子技術(shù)研究所,上海 201109)

0 引言

在直接序列擴(kuò)頻系統(tǒng)中,偽碼具有非常重要的作用。偽碼全稱為偽隨機(jī)噪聲(Pseudo-Random Noise,PRN)碼,又稱為擴(kuò)頻碼。在發(fā)射端,數(shù)據(jù)通過調(diào)制速率遠(yuǎn)高于數(shù)據(jù)速率的擴(kuò)頻碼,達(dá)到擴(kuò)寬頻譜的作用,利于信號的播發(fā),提高抗干擾性能。在接收端,利用擴(kuò)頻碼良好的相關(guān)性能對接收信號進(jìn)行解擴(kuò)。解擴(kuò)需要在本地生成與信號相對應(yīng)的偽碼,因此本地碼生成器是擴(kuò)頻接收機(jī)必不可少的組成部分。

目前,接收機(jī)中偽碼發(fā)生器多采用在只讀存儲器(Read Only Memory,ROM)中存儲的方式。這種碼發(fā)生器裝置占用資源少,但是在惡劣太空環(huán)境下發(fā)生單粒子翻轉(zhuǎn)[1]難以修復(fù),可靠性不足。根據(jù)奈奎斯特定理,系統(tǒng)時(shí)鐘至少是碼速率的2 倍。一些碼發(fā)生器采用分頻時(shí)鐘來實(shí)現(xiàn)碼速率的降頻[2-3],會對接收系統(tǒng)的時(shí)鐘同步性造成了影響。

本文設(shè)計(jì)了一種基于現(xiàn)場可編程門陣列(Field-Programmable Gate Array,F(xiàn)PGA)的實(shí)時(shí)生成的碼發(fā)生器結(jié)構(gòu),利用雙端口RAM 兩個(gè)獨(dú)立的讀寫裝置和偽碼的周期性特點(diǎn)來對偽碼進(jìn)行同時(shí)不間斷的寫入和讀出。寫數(shù)據(jù)基于系統(tǒng)時(shí)鐘計(jì)數(shù),讀數(shù)據(jù)利用NCO 技術(shù)輸出讀地址。在每個(gè)碼周期結(jié)束時(shí)對碼初相重新置位,減少了惡劣太空環(huán)境下碼翻轉(zhuǎn)對捕獲系統(tǒng)造成的影響,實(shí)現(xiàn)了全局時(shí)鐘下碼頻率的變頻處理,避免了FPGA 使用分頻時(shí)鐘造成的不穩(wěn)定性,同時(shí)通過控制讀地址和NCO 累加器的初值來控制輸出碼的相位,實(shí)現(xiàn)了高精度的可控相位輸出。該碼發(fā)生器可廣泛應(yīng)用于偽碼滑動(dòng)相關(guān)的擴(kuò)頻終端同步系統(tǒng)。

1 工作原理

1.1 Gold 碼生成原理

Gold 碼是直擴(kuò)序列擴(kuò)頻系統(tǒng)中常用的一種偽碼,具有生成容易和相關(guān)性能好的優(yōu)點(diǎn)[3]。Gold 碼由兩個(gè)相同級數(shù)的線性反饋移位寄存器所產(chǎn)生的相同長度的m序列經(jīng)異或相加實(shí)現(xiàn)[4]。

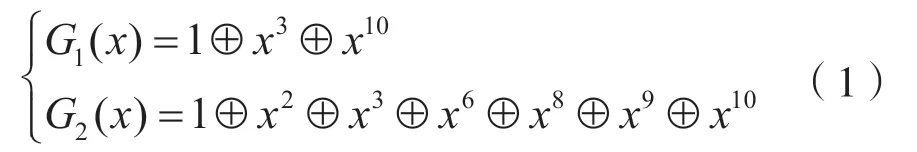

設(shè)Gold 碼特征多項(xiàng)式為:

式中,⊕為異或符號。

Gold 碼為周期性序列,其周期為2n-1,n為移位寄存器的階數(shù)。文中采用10 位的移位寄存器,則對應(yīng)碼周期為1 023。

對兩個(gè)寄存器設(shè)定相應(yīng)的初相,兩個(gè)寄存器的初相分別取:

則碼生成的原理如圖1 所示。

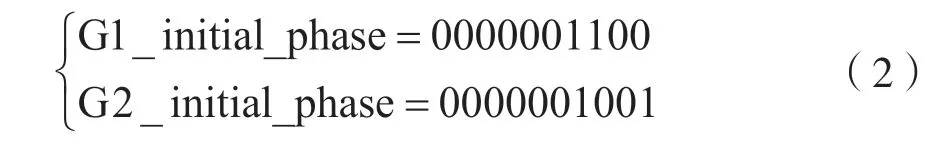

1.2 數(shù)控振蕩器原理

數(shù)控振蕩器(Numerical Controlled Oscillator,NCO)的作用是產(chǎn)生正交的正弦樣本和余弦樣本,通過查表法將事先根據(jù)各個(gè)正余弦波相位計(jì)算好相位的正余弦值[5]按照相位角度作為地址,存儲該相位的正余弦值,從而構(gòu)成一個(gè)幅度-相位轉(zhuǎn)換電路。圖2 為NCO 的一種電路設(shè)計(jì),在系統(tǒng)時(shí)鐘控制下由相位累加器對輸入頻率控制字不斷累加,得到以該頻率控制字為步進(jìn)的數(shù)字相位,再通過相位相加模塊進(jìn)行初始相位偏移得到要輸出的當(dāng)前相位。利用NCO 對數(shù)據(jù)變頻處理,具有頻率分辨率高、變化率快以及相位可連續(xù)線性變化等優(yōu)點(diǎn)。

圖2 NCO 原理

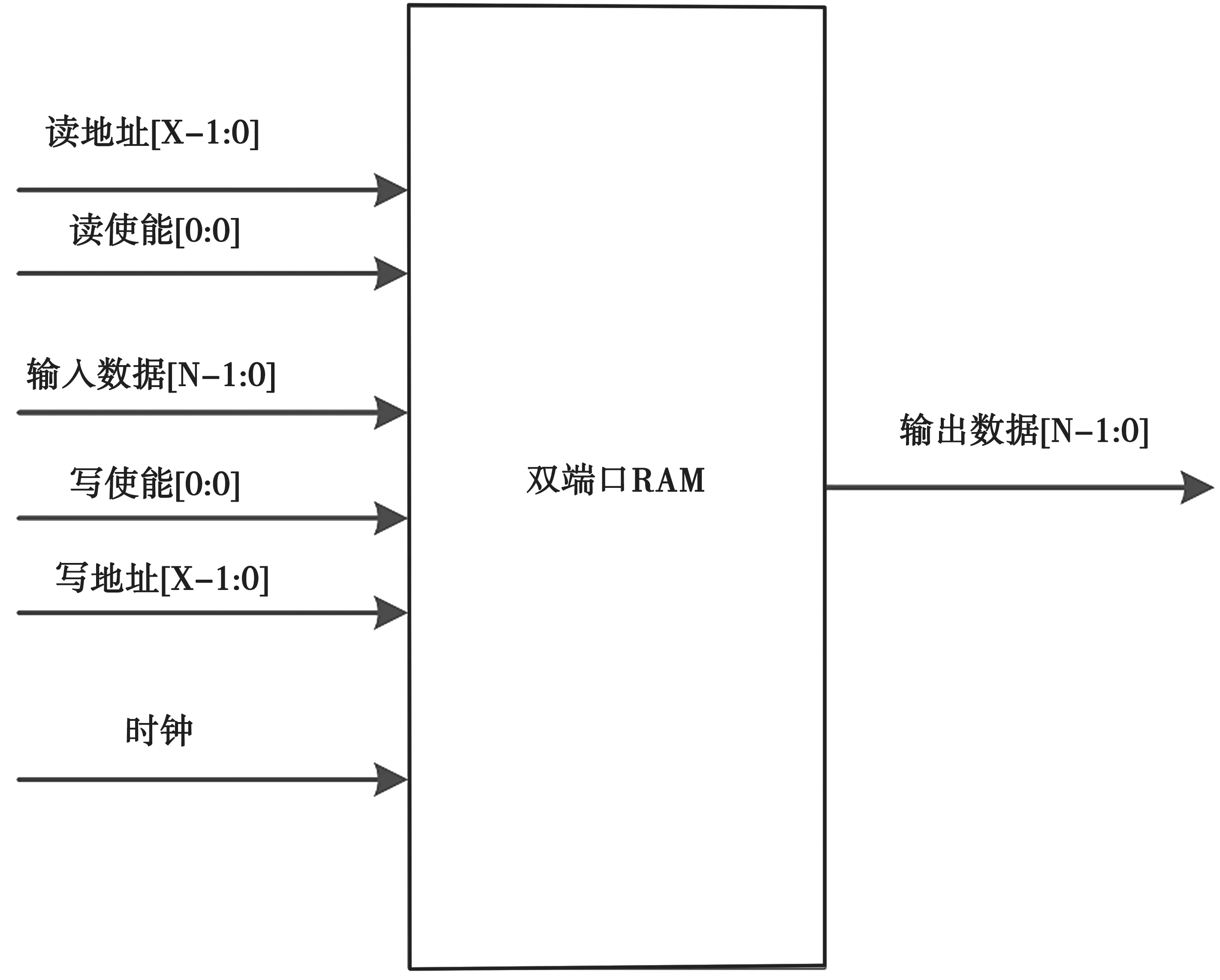

1.3 雙端口RAM 原理

雙端口RAM 是在一個(gè)靜態(tài)隨機(jī)存儲器(Static Random Access Memory,SRAM)上同時(shí)具有兩套完全獨(dú)立的數(shù)據(jù)線、地址線和讀寫控制線,并允許兩個(gè)獨(dú)立的系統(tǒng)同時(shí)對該存儲器進(jìn)行隨機(jī)性訪問,即共享式多端口存儲器。雙端口RAM 最大的特點(diǎn)是存儲數(shù)據(jù)共享。

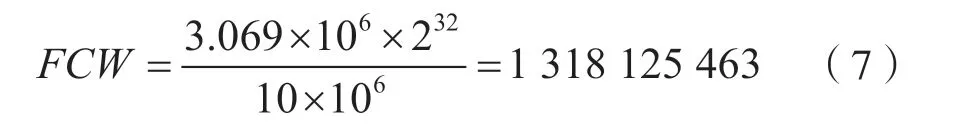

本文采用Xilinx 公司的ISE 開發(fā)工具中的雙端口RAM 的IP(Intellectual Property)核。IP 核的接口如圖3 所示。可以看出,一個(gè)存儲器上配備兩套獨(dú)立的地址——數(shù)據(jù)和使能,允許兩個(gè)獨(dú)立的CPU或控制器同時(shí)異步訪問存儲單元。因?yàn)閿?shù)據(jù)共享,所以必須存在訪問仲裁控制。內(nèi)部仲裁邏輯控制提供對同一地址單元訪問的時(shí)序控制、存儲單元數(shù)據(jù)塊的訪問權(quán)限分配以及信令交換邏輯等功能。在讀寫地址不沖突的情況下,可以通過兩套獨(dú)立的讀寫地址和使能對數(shù)據(jù)進(jìn)行讀寫操作。

2 實(shí)時(shí)生成方案

碼生成器硬件生成方案如圖4 所示。在開始信號脈沖給出后,寫使能置為“1”,此后寫使能一直處于高電平,同時(shí)給出在一個(gè)碼周期長度循環(huán)累加的計(jì)數(shù)器作為寫地址。每次周期結(jié)束給出一個(gè)置位脈沖,對兩個(gè)移位寄存器的初相進(jìn)行重新賦值。如果要對碼進(jìn)行截短,則可以將置位脈沖設(shè)置到需要截位的碼相位上。

圖3 雙端口RAM 接口原理

由于雙端口RAM 可以同時(shí)進(jìn)行讀操作和寫操作,設(shè)置碼NCO累加器的頻率控制字來控制讀地址,進(jìn)而改變輸出碼的頻率。此時(shí),輸出的碼速率為:

圖4 碼生成器原理

式中,fclk為系統(tǒng)時(shí)鐘,F(xiàn)CW為頻率控制字,L為累加器位寬。

設(shè)置兩個(gè)累加器cnt1和cnt2來進(jìn)行累加器的進(jìn)位檢測。cnt1的位寬為L,每次讀數(shù)開始脈沖給出后,對累加器賦相位初值。每個(gè)時(shí)鐘累加值為相位控制字FCW,對累加器cnt1延時(shí)一個(gè)時(shí)鐘得到cnt2。對cnt1和cnt2的最高位進(jìn)行進(jìn)位檢測,若兩個(gè)計(jì)數(shù)器發(fā)生進(jìn)位,即當(dāng)cnt2的最高位為“1”而cnt1的最高位變?yōu)椤?”時(shí),認(rèn)定cnt1發(fā)生進(jìn)位,對讀地址加1。

碼初相的設(shè)置分為整數(shù)位和小數(shù)位兩部分,分別設(shè)定為參數(shù)int_phase 和deci_phase。整數(shù)位int_phase范圍為0~1 022,小數(shù)位x范圍為0~1,換算到累加器的位寬中則小數(shù)位初相deci_phase 可以表示為:

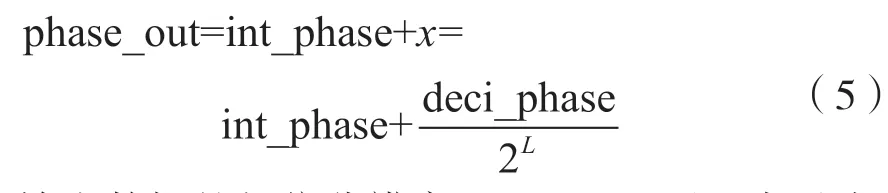

此時(shí)的輸出碼相位phase_out 為:

輸出數(shù)據(jù)的相位分辨率reso_phase 可以表示為:

具體的工作流程:在開始給出脈沖后,對寫地址賦高電平,寫地址開始累加,此后碼開始源源不斷地進(jìn)行寫入;每個(gè)碼周期結(jié)束時(shí)給出置位脈沖,對移位寄存器的初相重新賦值,確保偽碼不因太空中的單粒子翻轉(zhuǎn)發(fā)生錯(cuò)誤;對兩個(gè)移位寄存器的相位賦初值,動(dòng)態(tài)刷新存儲器中的碼;讀數(shù)開始信號需要在一個(gè)完整碼周期的偽碼寫入存儲器之后給出,以確保讀寫操作不發(fā)生沖突;讀書開始脈沖給出后,讀使能賦高電平,對讀地址和累加器相位賦初值,此后變頻后的偽碼開始不間斷輸出。其中,雙端口RAM 的輸入位寬決定了可以同時(shí)寫入的偽碼通道數(shù)量;碼NCO 的累加器位寬、相位控制字和系統(tǒng)時(shí)鐘決定了輸出碼速率。

3 結(jié)果仿真

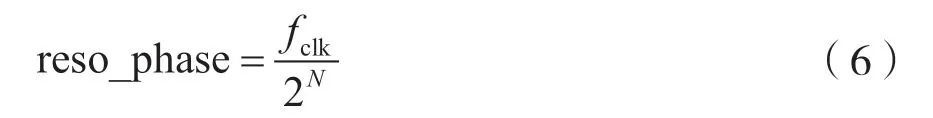

在Modelsim 上進(jìn)行仿真,系統(tǒng)時(shí)鐘為10 MHz,碼速率為3.069 MHz,累加器位寬為32,帶入式(3)可得頻率控制字FCW為:

輸出碼初相取5.8,則可知個(gè)位數(shù)地址int_phase為5。小數(shù)位地址deci_phase 帶入式(4),可得:

deci_phase=0.8×232=3 435 973 837 (8)

由式(6)可得此時(shí)的碼相位分辨率reso_phase為:

仿真結(jié)果如圖5 所示,可以看出寫地址和讀地址有著不同的位寬,輸出碼速率已經(jīng)進(jìn)行了降速處理,輸出碼相位也對應(yīng)了5.8 的設(shè)置值。

圖5 仿真結(jié)果

4 結(jié)語

本文設(shè)計(jì)了一種實(shí)時(shí)生成的碼發(fā)生器結(jié)構(gòu),利用雙端口RAM 和偽碼的周期性特點(diǎn)來進(jìn)行源源不斷地進(jìn)行刷新存儲,減少了惡劣太空環(huán)境下碼翻轉(zhuǎn)對捕獲系統(tǒng)造成的影響,同時(shí)利用碼NCO 來實(shí)現(xiàn)全局時(shí)鐘下碼頻率的變頻處理,減少了在FPGA 使用分頻時(shí)鐘造成的不穩(wěn)定性。通過設(shè)置整數(shù)位相位初值和小數(shù)位相位初值實(shí)現(xiàn)碼相位的輸出變化,具有相位分辨率高和易于相位調(diào)整的優(yōu)點(diǎn)。此外,對碼發(fā)生器進(jìn)行功能仿真,得到了設(shè)計(jì)預(yù)期的結(jié)果,可廣泛應(yīng)用于偽碼滑動(dòng)相關(guān)的擴(kuò)頻終端同步系統(tǒng)。