一種應用于RFID 感溫芯片的電磁取電電路*

李 嶠,徐 勇,李青龍

(陸軍工程大學,江蘇 南京 210007)

0 引言

隨著現代通信與計算機技術的快速發展,射頻識別技術也開始融入各個領域。在集成電路方面,隨著集成電路在國內的快速發展,集成電路因其體積小、重量輕、成本低和壽命長等優勢,與射頻識別技術的結合有著非常廣闊的應用前景。無線射頻識別(Radio Frequency Identification,RFID)技術,是一種自動識別技術,通過無線射頻方式進行雙向數據通信,天線發送無線射頻信號,對電子標簽或射頻卡進行讀寫,從而達到無接觸識別目標和數據交換的目的。

RFID 感溫芯片就是應用無線射頻識別技術的集成電路芯片,此芯片無需外部電源供電,從天線接收到的電磁功率信號能夠為芯片提供進行正常工作的所有能量。RFID 感溫芯片內部的電源電壓來自感溫芯片中的電磁取電電路,電磁取電電路基于無線射頻識別技術,接收天線發射出的射頻信號,從射頻信號中獲取能量轉換為整個標簽芯片的電源電壓。因此,電磁取電電路的性能對整個芯片的性能有著至關重要的影響。電磁取電電路通常是由整流電路、基準源電路和低壓差線性穩壓器(Low Dropout Regulator,LDO)穩壓電路組成。

1 電路設計

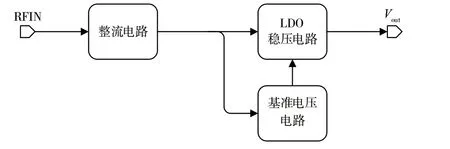

本文所設計的電磁取電電路框架如圖1 所示,整流電路接收由天線發送的ASK 調制的射頻信號(RF-Radio Frequency Signal,RFIN),得到一個有一定波紋系數的直流電壓,該直流信號經過基準電壓源電路得到一個參考電壓Vref,最后參考電壓與直流信號送入LDO 穩壓電路中生成一個穩定的直流電壓Vout為感溫芯片的其他電路供電。

圖1 電磁取電電路

1.1 整流電路

整流電路主要由兩部分構成,首先是由Dickson 電荷泵整流結構組成的倍壓整流部分,其次是由電壓限幅電路組成的保護電路部分。

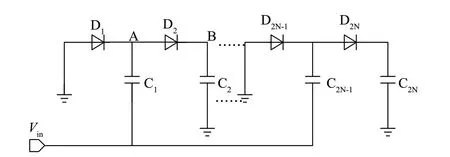

倍壓整流部分是由二極管、金屬氧化物半導體場效應晶體管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)和電容構成的Dickson電荷泵[1]組成。Dickson 電荷泵的結構原理如圖2所示。

圖2 Dickson 電荷泵原理

根據圖2 可知,電荷泵的第一級由電容C1、C2和二極管D1、D2組成,當輸入信號VIN在負半周期時D1導通,D2截止,電流經過二極管D1對電容C1進行充電。因為二極管D1的閾值電壓為VTH,因此電容C1的電壓為:

當輸入信號VIN在正半周期時,D2導通,D1截止。此時,根據電荷守恒定理,C1上的電壓不會發生變化,仍然為VIN-VTH,同時與輸入電壓的正半周相疊加。因此,A 點的電壓最高可以達到2VIN-VTH,由基爾霍夫定律可以得知,B 點加上D2上的導通閾值電壓,電容C2,即B 點上的電壓最高可以達到:

因為VC2作為第一級的輸出和第二級的輸入,根據電荷泵第一級的推導原理可以得出,第二級的輸出為:

根據數學歸納法,可以得出第N級的輸出為:

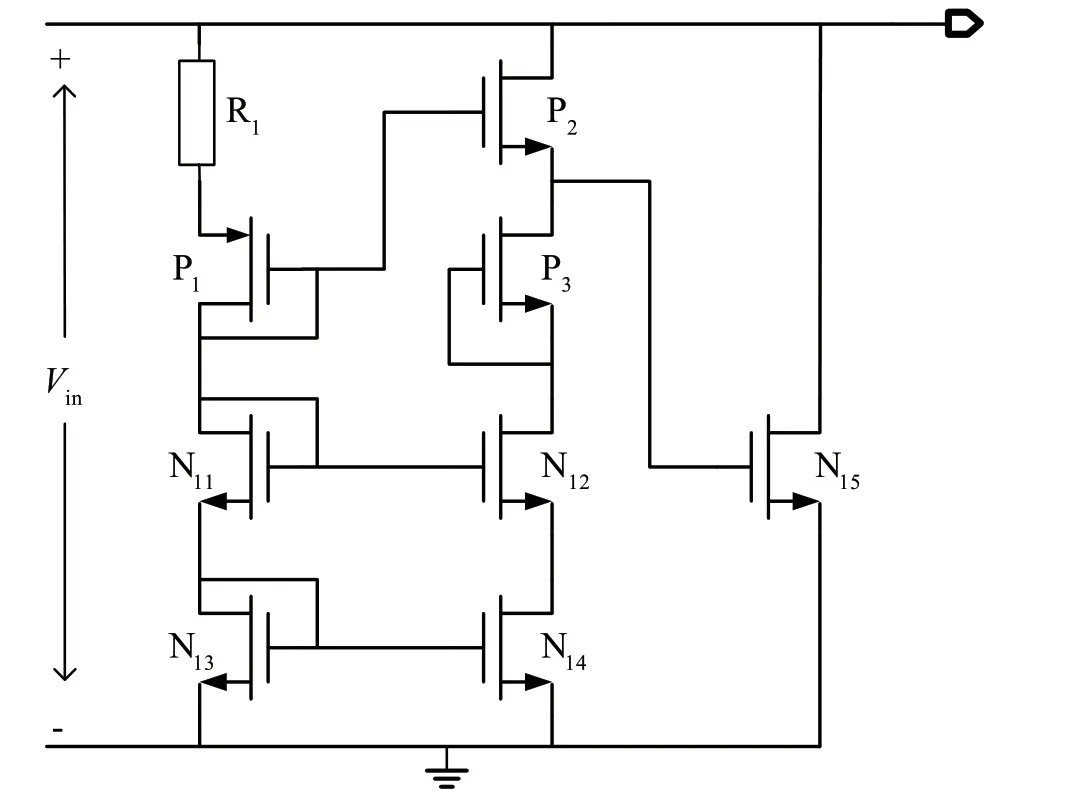

因為電磁取電電路各個子電路使用的均是普通的MOS 管,為了保護MOS 管不被過高的電壓擊穿,設計了一款電壓限幅電路如圖3 所示。

圖3 電壓限幅電路

電壓限幅電路工作原理主要分為兩個部分。

首先,當倍壓整流電路的輸出電壓VIN<VTHP+2VTHN時。此時,限幅電路的輸入電壓即整流電路的輸入電壓VIN小于P1的閾值電壓VTHP和N11、N13的閾值電壓VTHN之和,整流電路的輸出電壓較低,元件沒有被擊穿的危險,因此電壓限幅電路暫未開啟。

其次,隨著整流電路輸出的電壓VIN逐漸增大,一直增大到VIN>2VTN+VTP時,電壓限幅電路的輸入電壓VIN大于P1的閾值電壓VTHP和N11、N13的閾值電壓VTHN之和,因為P1、N11、N13導通,所以電路中開始有電流流經電阻R1。此時根據基爾霍夫定律,VGSP2=VGSP1+VR1,所以當VR1增加到VGSP2大于P2的閾值電壓VTHP2時,此時N15管導通,泄流保護。

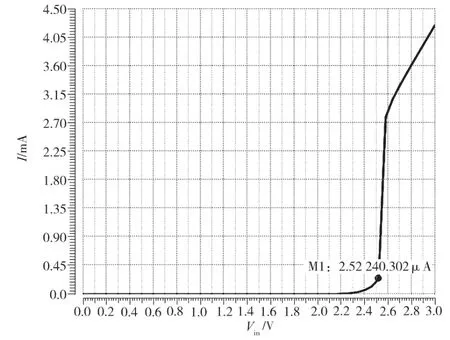

限幅電路輸入電壓與電流曲線如圖4 所示,當限幅電路輸入電壓達到約2.5 V 時,電路開始泄流。

圖4 限幅電路輸入電壓與電流曲線

整流電路由五級電荷泵整流結構和限幅電路組成。其仿真結果圖5 所示,可以看出,射頻信號經過整流之后,能夠輸出一個穩定在2.5 V 左右的單向脈動性直流電壓,較好地實現了整流。

圖5 整流電路仿真結果

1.2 基準電壓源

帶隙基準源[2]通常被用來產生參考電壓,帶隙基準電路通常是為了生成一個與輸入電源和工藝無關,且有明確溫度特性的直流電壓。其主要原理是利用正溫度系數電壓熱電壓VT和三極管發射結負溫度系數電壓VBE,分別乘以一定的系數后相加產生一個零溫度系數的電壓。

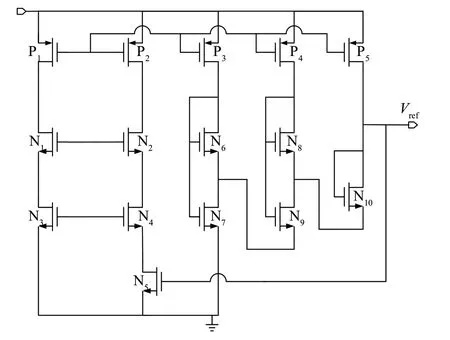

本文采用的亞閾值基準電壓電路[3]如圖6 所示,是一個常用的應用在低功耗場景中的基準電壓源的解決方案。工作在亞閾值區的MOS 管,雖然其柵源電壓VGS小于其閾值電壓VTH,但是此時MOS 管存在一個弱反型層,所以仍然有微弱的電流流過MOS 管,而當MOS 管處于亞閾值區時,漏源電壓為正溫度系數變量,柵源電壓為負溫度系數變量。

圖6 基準電壓源電路

由圖6 可知:

根據亞閾值電流的公式及電流鏡的比例可得:

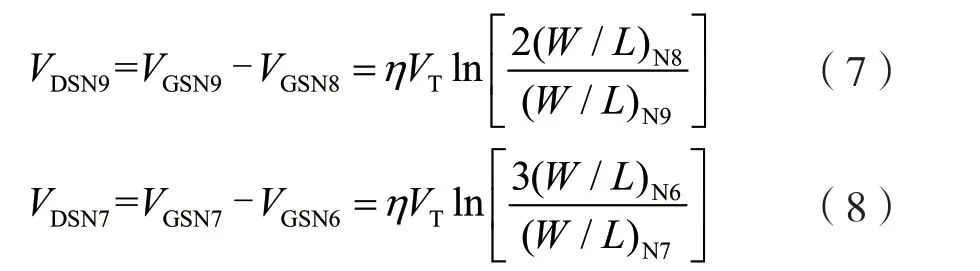

由式(6)可得到VDSN9和VDSN7的結果:

式中,VT是一個正溫度系數的變量,因此VDSN9與VDSN7的和具有正溫度系數。

對于MOS 管N10:

式中,VT=kT/q,IS為飽和電流,正比于μkTni2,μ為少數載流子遷移率,ni為硅的本征載流子濃度。

根據μ與ni溫度的關系可得到飽和電流IS與溫度的關系:

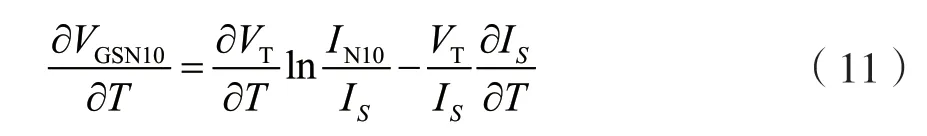

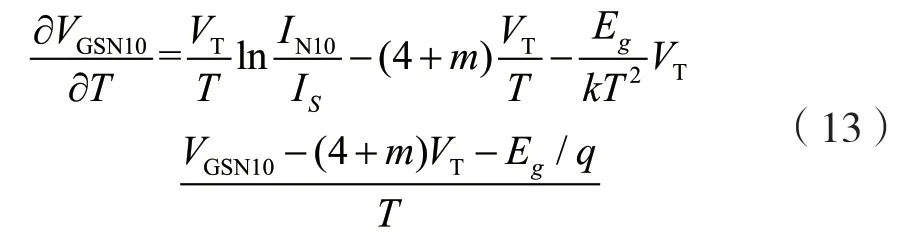

b是一個比例系數。在VGSN10對T取導數時,IN10也是溫度的函數。假設IN10不變,VGSN10對T求導可得:

根據IS與溫度的關系可得:

因此可得到VGSN10對T求導的結果:

由結果可以看出VGSN10是一個成負溫度系數的變量,與自身的大小和溫度有關。

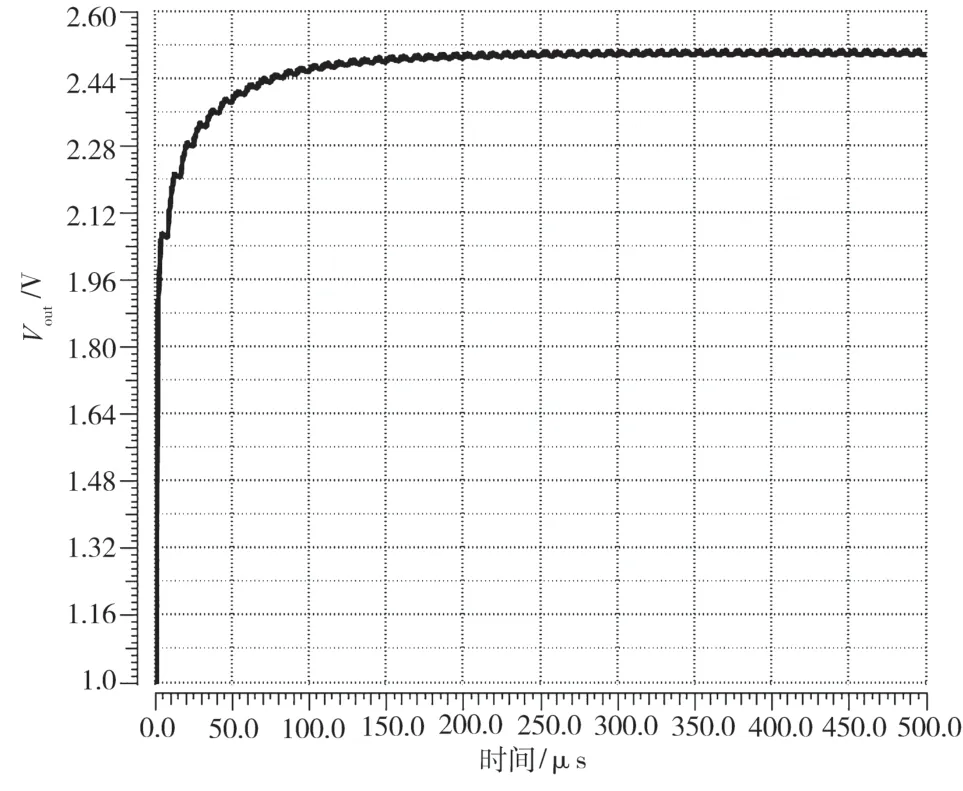

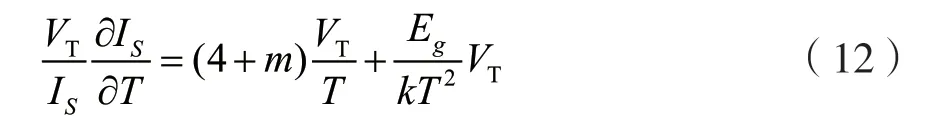

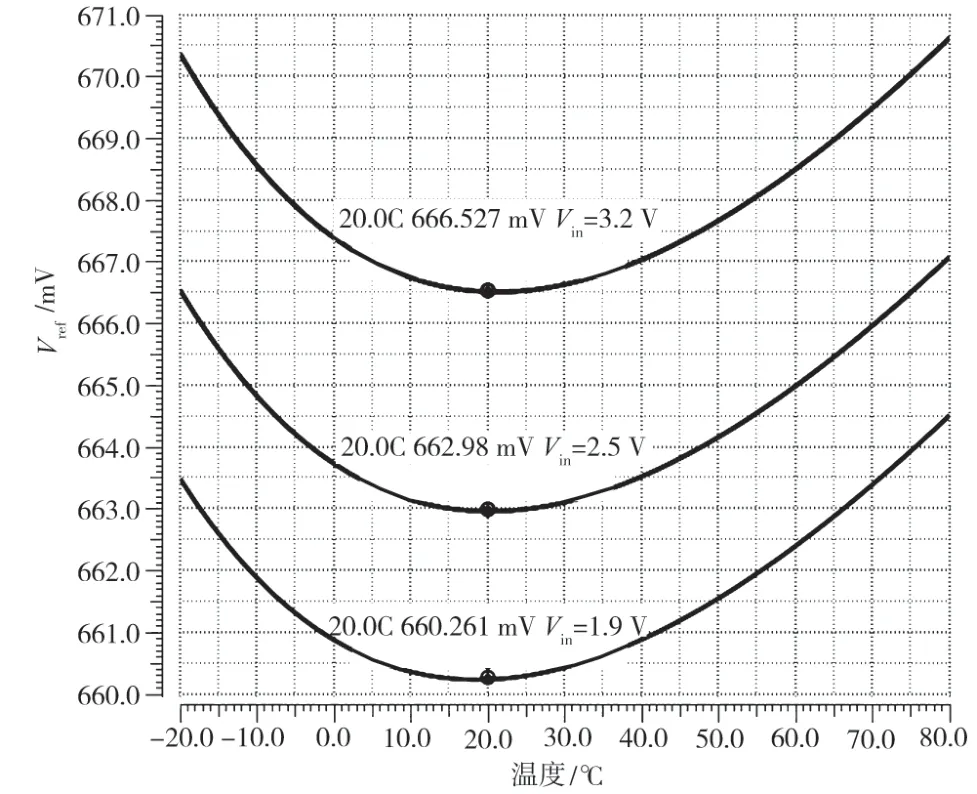

因此調節N6、N7、N8、N9的寬長比得到一個正溫度系數,調節N10的寬長比得到一個負溫度系數,經過計算,最終得到一個與溫度和輸入電壓無關的基準電壓Vref。帶隙基準電壓源電路的仿真結果如圖7 所示。

圖7 基準電壓源仿真結果

因為倍壓整流電路的輸入電壓會在一定范圍內波動,所以將輸入電壓定義在1.9~3.2 V,溫度變化為-20~80 ℃。由圖7 可以看出該電壓源電路在最低和最高輸入電壓得到的參考電壓Vref結果差距很小,溫度系數為0.000 06/℃,在常溫下的輸出結果為663 mV。

1.3 LDO 穩壓電路

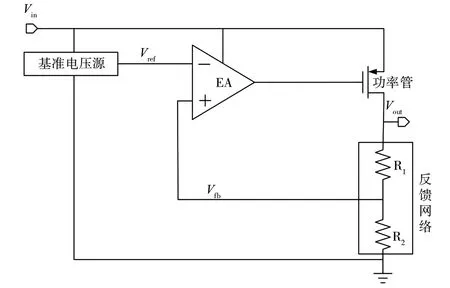

LDO 電路[4]一般由基準電壓源、誤差放大器、功率管和反饋網絡4 部分組成,如圖8 所示。

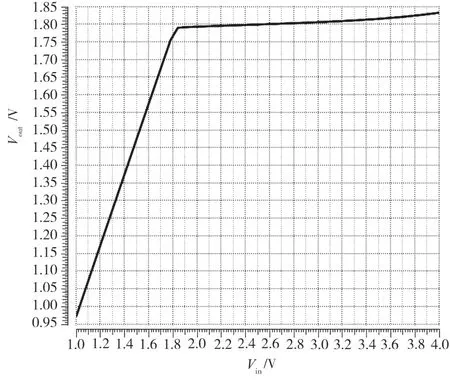

本文設計的LDO 電路,誤差放大器的性能對輸出穩定電壓的精度有很大影響。因此誤差放大器使用了折疊式共源共柵結構,從而減小放大器的輸出電阻,使其極點在內部。LDO 的功率管選擇PMOS 管,PMOS 管雖然驅動能力不如NMOS 管,但是PMOS 管壓降更低,從而能夠提高LDO 的工作效率,降低系統功耗。當誤差放大器的開環增益足夠大,處于深度反饋區,此時Vref等于Vfb,通過調整反饋電阻網絡中串聯電阻比值,控制最終的輸出電壓Vout。LDO 穩壓電路仿真結果如圖9 所示,輸入的電源電壓由1 V 上升到4 V,當電源電壓上升到1.8 V 左右時,LDO 的輸出電壓開始穩定在1.8 V,一直到輸入電壓上升到3.2 V 左右時,LDO穩壓電路始終能將輸入電壓穩定在1.8 V,較好地實現了在整流電路的輸出電壓范圍內將電壓穩定在1.8 V 的目標。

圖8 LDO 穩壓電路

圖9 LDO 穩壓電路仿真結果

1.4 系統仿真分析

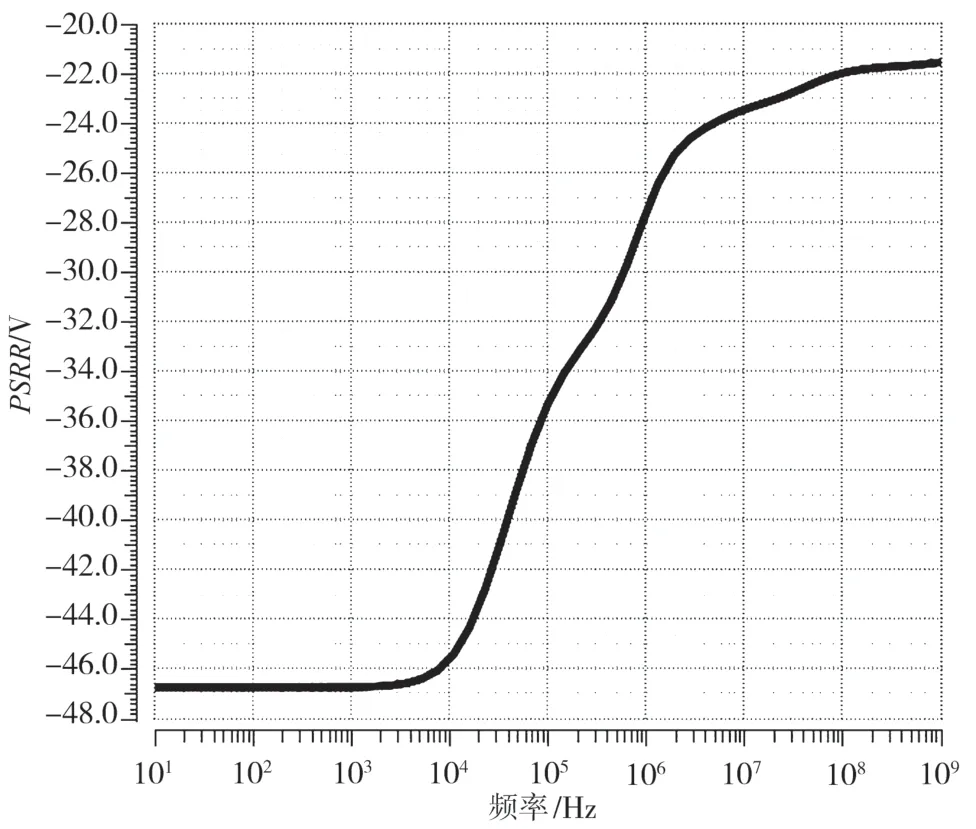

穩壓電路性能參數[5]的優劣很大程度上決定了整體電磁取電電路性能,其中電源抑制比(Power Supply Rejection Ratio,PSRR)對穩壓電路的穩壓效果有很大影響,其反映了輸出的直流電壓受到整流電路輸入信號的影響。穩壓電路輸出的電壓為1.8 V,電源誤差在±5%,即輸出電壓在1.71~1.89 V 之間。同時,由于整流電路的輸出電壓有波紋,因此需要驗證穩壓電路的電源抑制比,PSRR 仿真結果如圖10 所示。

圖10 PSRR 仿真結果

從圖10 可以看出,電路在低頻時對電源輸入雜波的抑制能力達到-47 dB。

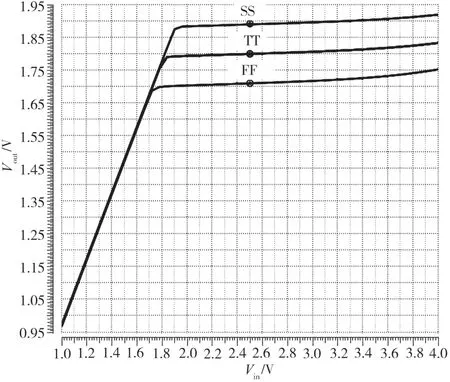

為了提高流片成功率,需要對電路進行可靠性驗證[6],所以分別從TT、SS、FF 等多個工藝角對電路進行可靠性驗證。仿真結果如圖11 所示。

可以看出,當輸入電壓大于1.6 V 時電路開始穩壓,在整流輸入1.6~3.4 V 時,各個工藝角都能將電壓穩定在(1.8±5%)V 以內。

2 版圖設計

模擬集成電路版圖設計的核心要素是器件的匹配設計,在芯片由廠家代工的過程中,由于工藝偏差等原因,芯片測試結果與仿真結果有可能會產生較大的誤差,因此在版圖設計中可以通過匹配的方式來減少這些偏差造成的影響,其中,主要是對晶體管和無源器件進行匹配設計。

圖11 可靠性驗證

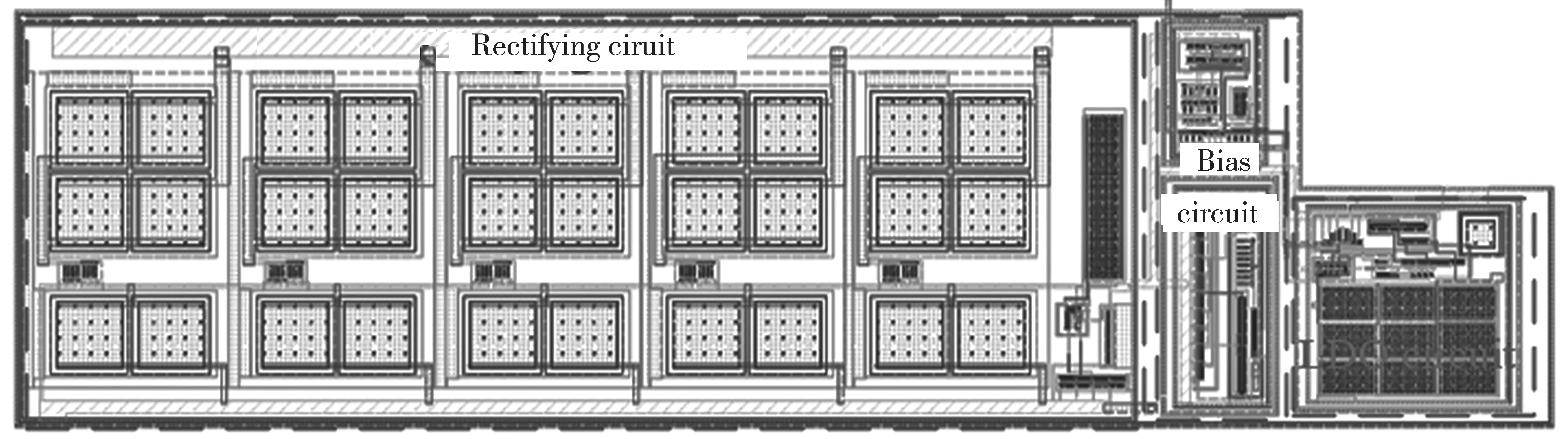

本文對電流鏡晶體管采用軸對稱匹配,運放的差分對晶體管采用中心對稱匹配,穩壓電路中的電阻采用共質心匹配。選擇一個電阻作為基本單元,然后通過串聯或者并聯的方式得到所需要的阻值,最后的整體版圖如圖12 所示。

圖12 電磁取電電路版圖

3 結語

本文使用TSMC CMOS 0.18 μm 工藝,較為完整地完成了電磁取電電路的設計。采用了五級電荷泵和限幅保護電路組成的整流電路,能夠給后級電路提供一個在2.5 V 左右波動的電源電壓。另外,在-20~80 ℃的溫度下,完成了輸入電壓1.9~3.4 V 都能輸出663 mV 左右的帶隙基準電壓源電路設計和穩定輸出1.8 V電壓的穩壓電路設計。