多通道低相噪同步頻率源設計

胥 偉,潘明海,張艷睛

(南京航空航天大學 電子信息工程學院,江蘇 南京211106)

0 引言

DRFM 系統(tǒng)在產生雷達欺騙干擾回波時,需要一個高穩(wěn)定度的頻率源信號用于對外部輸入信號的采集與重構。 作為DRFM 系統(tǒng)關鍵技術之一,頻率源一旦出現(xiàn)偏差,整個系統(tǒng)將無法正常工作。 當前,最主要的頻率源產生技術包括直接數(shù)字合成[1-2]以及鎖相環(huán)頻率合成[3-4],直接數(shù)字合成技術一般結構相對復雜,且很容易輸出較高的雜散[5],而鎖相環(huán)技術相對已比較成熟,且在設計時會考慮加入環(huán)路濾波器,因此能有效地過濾相位噪聲。此外,鎖相環(huán)技術頻率源電路的結構較為簡單,且能輸出低相噪、高穩(wěn)定度的頻率信號[6]。 本文將采用鎖相環(huán)頻率合成技術進行設計。

1 鎖相環(huán)的基本原理

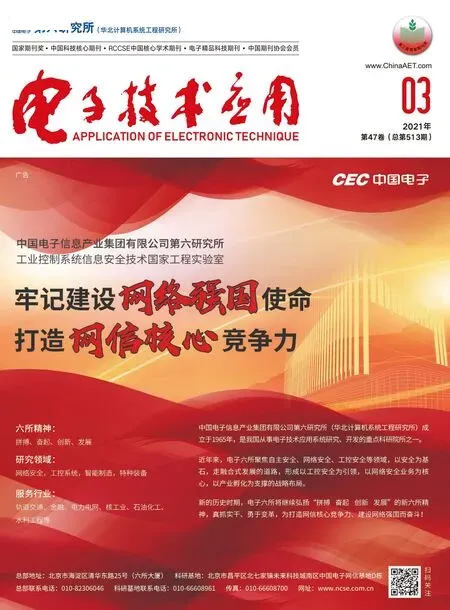

圖1 鎖相環(huán)工作原理框圖

負反饋系統(tǒng)的鎖相環(huán)通常由鑒相器、電荷泵、環(huán)路濾波器、壓控振蕩器(VCO)、分頻器等組成[7],如圖1 所示。 鑒相器對經(jīng)過R 分頻的參考頻率信號與經(jīng)過N 分頻的鎖相環(huán)輸出信號進行比較并產生兩者的相位誤差信號;電荷泵將相位誤差信號轉變?yōu)榕c此成比例的電流信號;低通環(huán)路濾波器對電荷泵輸出電流積分以產生對應的電壓信號;VCO 根據(jù)輸入電壓信號輸出對應的頻率[8-9]。

2 鎖相環(huán)相位噪聲理論分析

2.1 相位噪聲的定義

鎖相環(huán)穩(wěn)定工作時,其自身的非線性效應能有效抑制輸出信號振幅波動,但是其相位波動無法抑制。 因為相位波動的存在,鎖相環(huán)輸出信號在時域上的過零點間隔不再均勻,造成頻率信號的“抖動”。 “抖動”的存在會使部分功率產生頻偏,中心頻譜周邊產生的邊帶,即為相位噪聲[10]。

相位噪聲定義為一個頻偏上的噪聲功率與輸出信號載波功率的比值,一般將其歸一化到1 Hz 帶寬,如圖2所示,單位為dBc/Hz。 則相位噪聲計算公式為[11]:

圖2 相位波動譜密度

2.2 頻率源相位噪聲對采樣性能影響

頻率源信號的性能會嚴重影響ADC 器件,對高速信號的采集,會造成采樣值嚴重偏離理想采樣值,破壞采樣的時序。

當頻率源相位噪聲較高時,頻率源會存在隨機性“抖動”,假設時鐘抖動量為ΔT,此時的頻率源信號為:

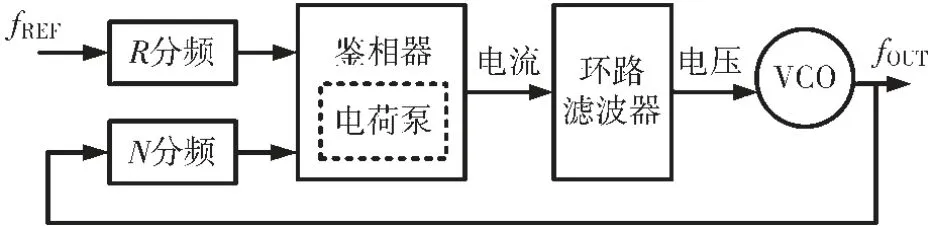

采樣時刻會發(fā)生一定的隨機偏移,偏移量為ΔT,此時的采樣位置不再確定,ADC 器件對輸入信號進行非均勻采樣,采樣輸出如圖3 所示。

圖3 有相位噪聲時鐘采樣

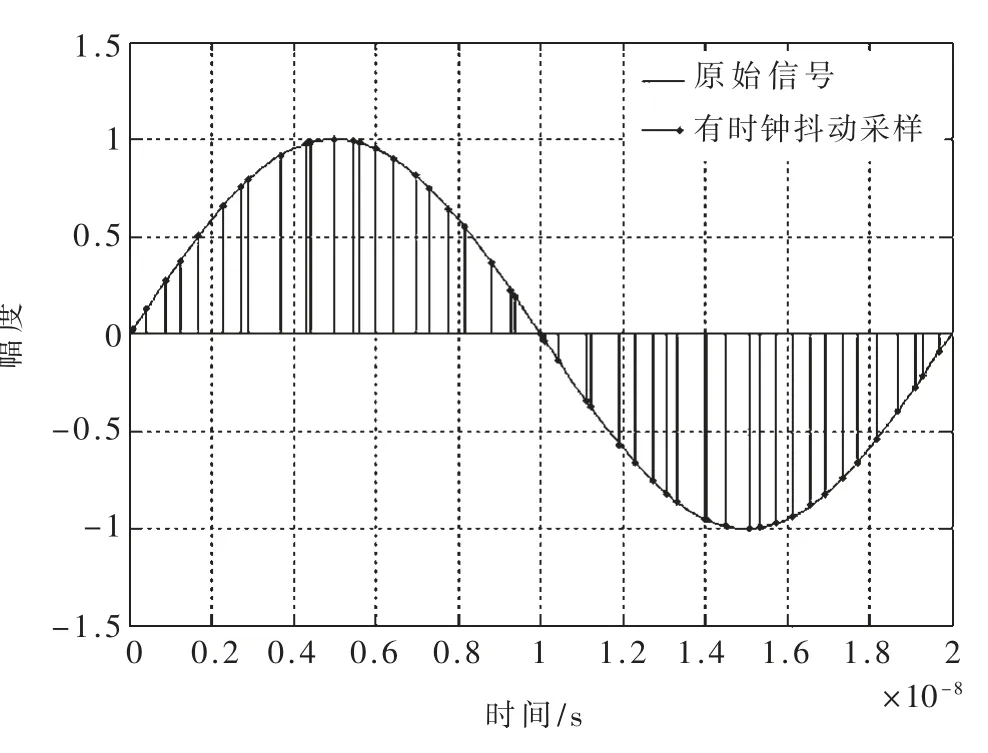

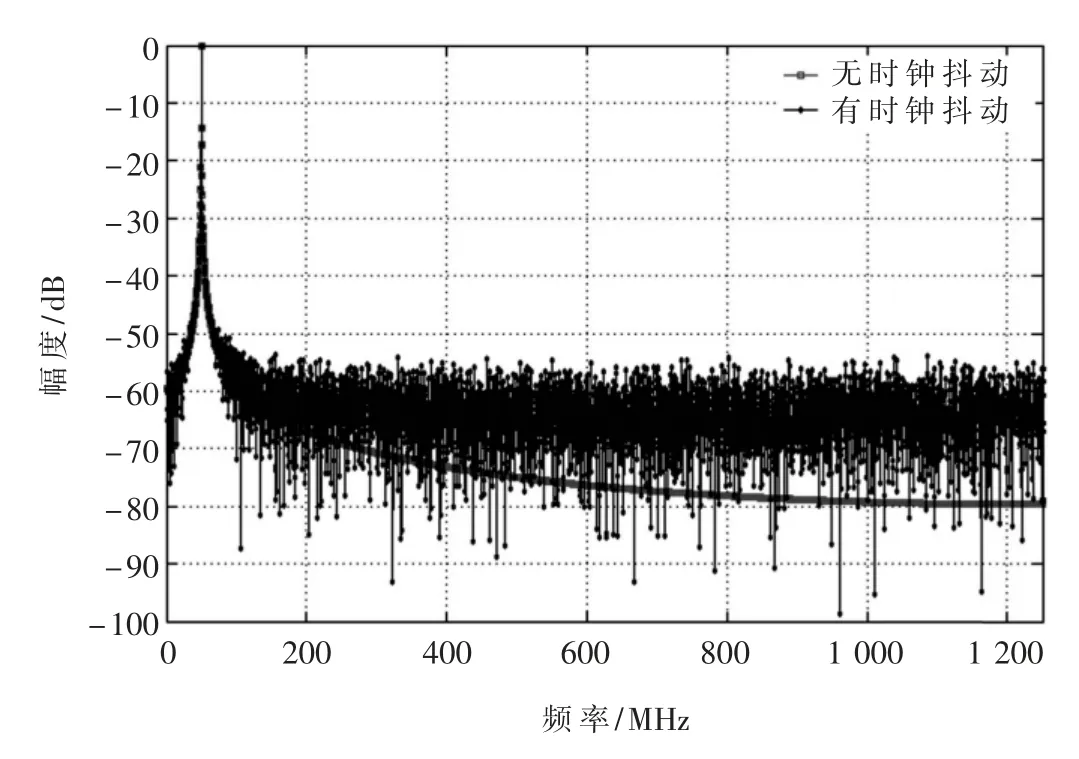

數(shù)據(jù)采集完成以后,若以無“抖動”的頻率源重構采樣信號時,結果如圖4、圖5 所示。

從時域圖4 中可以得出,信號重構時出現(xiàn)了明顯的畸變。從頻域圖5 中可以得出,信號雜散性能顯著惡化。如果采用更高的采樣速度,那么由抖動時鐘引入的噪聲將更加明顯。 因此在ADC 采樣系統(tǒng)孔徑抖動確定時,一個高穩(wěn)定度的頻率源是系統(tǒng)穩(wěn)定性的重要保證。

圖4 均勻頻率時域重構

圖5 均勻頻率頻域重構

2.3 鎖相環(huán)相位噪聲理論

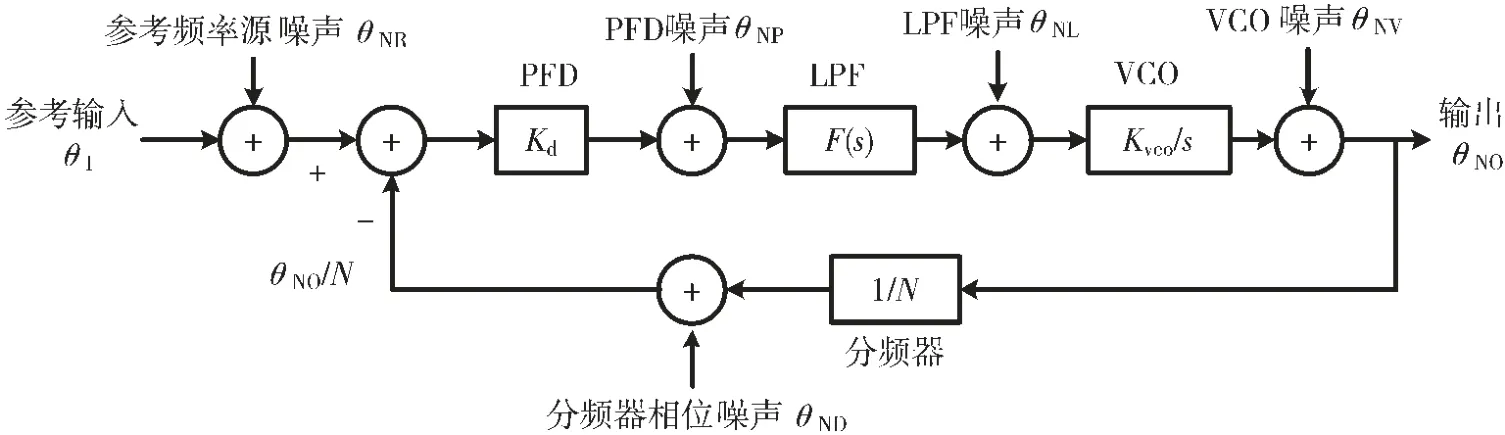

鎖相環(huán)系統(tǒng)是一個非線性的系統(tǒng),但是當鎖相環(huán)的鑒相比較頻率為環(huán)路帶寬的10~20 倍時,可將其近似認為是一個線性系統(tǒng)[12]。 線性系統(tǒng)條件下通過傳輸函數(shù)分析各個模塊對整個環(huán)路相位噪聲產生的影響。假設鎖相環(huán)路中各個模塊產生的是互不相關的加性噪聲,鎖相環(huán)噪聲線性模型如圖6 所示。

該鎖相環(huán)路的開環(huán)增益為:

式中,Kd為鑒相器增益,KVCO為壓控振蕩器靈敏度,F(xiàn)(s)為環(huán)路濾波器的傳輸函數(shù),N 為分頻比。

鎖相環(huán)路總的相位噪聲為參考頻率源相位噪聲、鑒相器相位噪聲、環(huán)路濾波器相位噪聲、壓控振蕩器相位噪聲和分頻器相位噪聲的總和,即為:

圖6 鎖相環(huán)噪聲模型

由于鎖相環(huán)路中采用的是低通濾波設計,故開環(huán)傳遞函數(shù)H(s)和閉環(huán)傳遞函數(shù)NH(s)/(1+H(s))都具有低通特性,而1/(1+H(s))具有高通特性。 所以除了VCO 噪聲源具有高通特性外,其余噪聲源都具有低通特性。 對于低通特性的噪聲,環(huán)路帶寬越小,噪聲抑制能力越強;而高通特性的噪聲,環(huán)路帶寬越大,噪聲抑制能力越強。因此,為了均衡的抑制噪聲,環(huán)路帶寬選擇確定在兩種噪聲譜密度線的交叉點。

2.4 各模塊相位噪聲模型分析

2.4.1 參考頻率源相位噪聲分析

假設一個具有相位噪聲的正弦波時鐘信號為:

因而周期抖動可表示為Jd=θ(t)/2πfc。

因為周期抖動噪聲Jd<<π/2,故式(5)可簡化為:

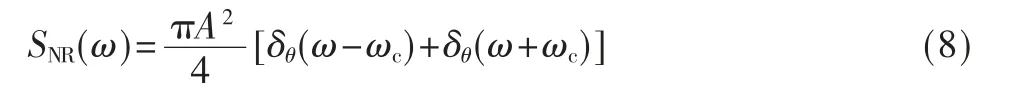

因此式(6)的頻譜可表示為:

其 中,δθ(f)是θ(t)的 頻 域 表 示。

因此可以得到時鐘信號的相位噪聲功率譜密度函數(shù)為:

從式(8)看出,減小參考頻率抖動,可減小輸出信號相位噪聲。

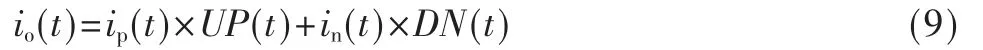

2.4.2 鑒相器等效輸出相位噪聲

鑒相器等效噪聲模型如圖7 所示。

由于式(9)中兩項原理相同,故取其中一項進行分析,并對其取傅里葉變換可得:

圖7 鑒相器等效噪聲模型

從上式得出,提高鑒相頻率fref可減小相位噪聲。

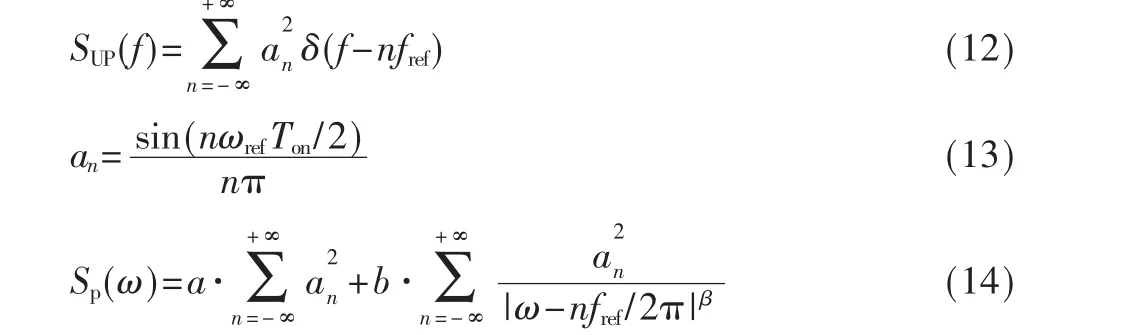

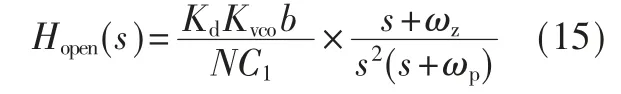

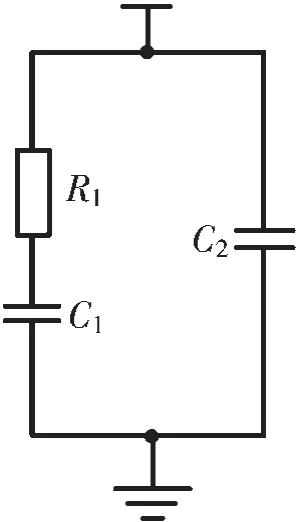

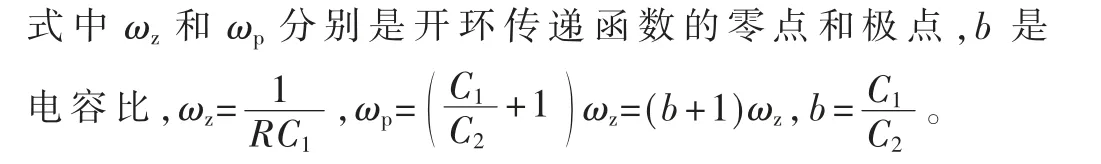

2.4.3 環(huán)路濾波器相位噪聲分析

二階無源環(huán)路濾波器模型如圖8 所示,電容C2將電荷泵輸出電流轉換成直流電壓,并通過濾除電壓紋路,改善振蕩器輸出信號的寄生調制,同時R1、C1支路能有效提高環(huán)路穩(wěn)定性。

環(huán)路濾波器的開環(huán)傳遞函數(shù)為:

圖8 二階無源環(huán)路濾波器模型

無源二階環(huán)路濾波器的相位噪聲功率譜密度為:

式中K 為玻爾茲曼常數(shù),T 為溫度值,B 為帶寬,R 為電阻值。 從式(16)得出,降低電阻R,能夠降低環(huán)路濾波器的相位噪聲。

2.4.4 VCO 相位噪聲分析

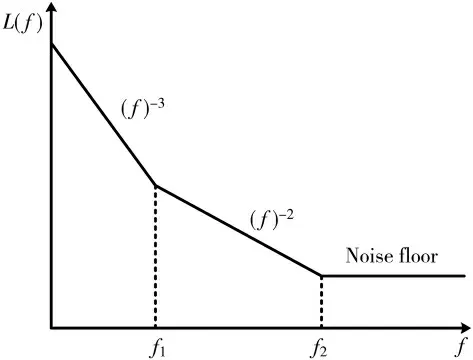

VCO 的相位噪聲模型如圖9 所示,該模型主要分成三個區(qū):與偏移頻率三次方成反比的1/f3區(qū);與偏移頻率平方成反比的1/f2區(qū);與偏移頻率無關的噪底區(qū)。 接近載波功率的1/f3區(qū)的相位噪聲在工作時會被抑制,而VCO 的輸出噪聲主要來自1/f2區(qū)。

圖9 VCO 相位噪聲曲線

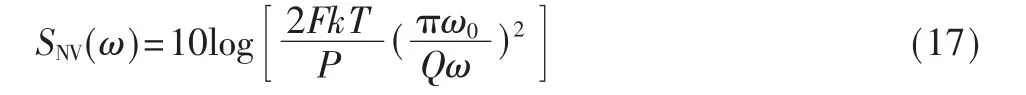

1/f2區(qū)相位噪聲功率譜密度為[13]:

式中,F(xiàn) 是一個實驗參數(shù), 表示的是晶體管對相噪的影響。 k 為玻爾茲曼常數(shù),T 為絕對溫度,P 為載波功率,Q為諧振腔Q 值。

從式(17)看出,提高VCO 的載波功率,即提高VCO的輸出幅值,同時降低Kvco,能夠降低VCO 在1/f2區(qū)的相位噪聲。

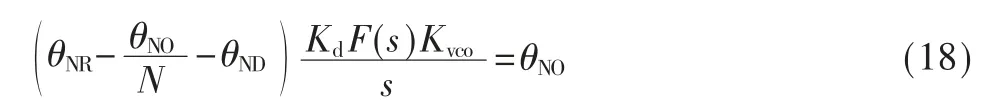

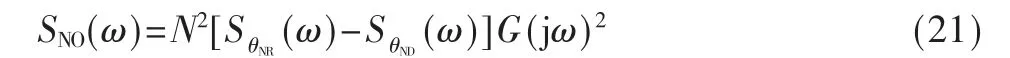

2.4.5 分頻器相位噪聲分析

N 分頻器可在其他條件不變的情況下改變VCO 的輸出頻率,并且可改變鑒相頻率,提高輸出頻率分辨率。

由于N 分頻存在,輸出端會引入噪聲θNO/N,則:

整理可得:

其中:

故分頻器相位噪聲譜密度為:

顯然, 輸出噪聲因為N 分頻器而起到倍頻的效果。在低頻偏時,G(jω)≈1,且SθNR遠大于SθND,輸出噪聲會增加近20logN。 因此N 分頻器的值不宜不太,如果N 太大,可以提高輸入?yún)⒖碱l率或者多級鎖相環(huán)來降低N分頻帶來的影響。

2.5 相位噪聲改善措施

頻率源最重要的性能指標之一就是相位噪聲,綜合上述分析,降低各模塊相位噪聲措施如下:

(1)輸入?yún)⒖紩r鐘:采用高性能的恒溫晶振作為參考頻率源輸入,并且可采用兩級鎖相環(huán)的設計,第一級鎖相環(huán)在外部恒溫晶振驅動下,為第二級鎖相環(huán)提供高穩(wěn)、低相噪的參考時鐘;

(2)鑒相器:提高鑒相頻率可以減小輸出信號相位噪聲;

(3)環(huán)路濾波器:降低電阻R,可減小相位噪聲;

(4)VCO:提高VCO 的輸出幅值,降低Kvco能夠改善其相位噪聲性能;

(5)分頻器:采用更高的頻率信號作為參考時鐘,或者采用多級鎖相環(huán)結構,減小分頻系數(shù)N,以改善分頻器的相位噪聲性能。

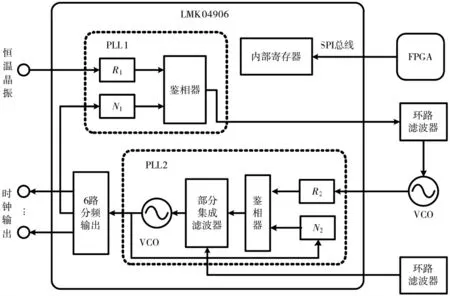

3 頻率源器件選型與方案設計

本頻率源設計最核心的器件是鎖相環(huán)芯片,該器件選用TI 公司的時鐘管理芯片LMK04906,它具有雙鎖相環(huán)結構,可工作于雙鎖相環(huán)和單鎖相環(huán)兩種模式,能實現(xiàn)6 路差分或者12 路單端在2.26~2 600 MHz 范圍內的任意同步頻率輸出,相位檢測器速率可達155 MHz,相位噪聲底低至-227 dBc/Hz,能夠保證高穩(wěn)頻率信號的輸出。

控制器采用一片Xilinx Spartan-6 FPGA 芯片通過SPI 總線完成LMK04906 芯片內部寄存器的配置。

參考輸入是外部給PLL 的參考時鐘信號,該信號會直接影響輸出信號的性能,故采用高穩(wěn)定度的恒溫晶振作為參考輸入。

本設計采用兩級鎖相環(huán)結構,如圖10 所示,增加第一級鎖相環(huán)的目的是為第二級鎖相環(huán)提供高穩(wěn)定度、低相噪的參考頻率。第一級鎖相環(huán)的環(huán)路濾波器為保證恒溫晶振輸入的性能而采用窄帶設計,第二級鎖相環(huán)的環(huán)路濾波器為保證VCO 輸出相噪性能而采用寬帶設計。在此結構下,頻率源可輸出多路與參考輸入同相位的信號。

4 實驗測試結果

多通道同步頻率源設計采用6 階PCB 層疊設計,實物加工板卡如圖11 所示。

通過羅德與施瓦茨的頻譜儀FSL6 對設計的頻率源電路輸出信號進行雜散和相位噪聲測試分析,實測采用高穩(wěn)定度、低相噪的10 MHz 恒溫晶振作為第一級鎖相環(huán)的參考頻率輸入。

PLL2 環(huán)路帶寬內基底相位噪聲由式(22)估算可得[14]:

式中,N@1Hz表示PLL2 的歸一化相位噪聲底,LMK04906器件N@1Hz的值為-227 dBc/Hz;N 表示分頻系數(shù);fpdf表示鑒相頻率。

根據(jù)相位噪聲改善措施進行優(yōu)化設計,設置N 分頻為250,fpdf為10 MHz,則頻率源基底相位噪聲理論值為[15]:

圖10 頻率源設計方案

圖11 頻率源硬件實物圖

從實際測試結果圖12 看出,當頻率源電路輸出中心頻率為1.25 GHz 信號時,頻率信號雜散抑制優(yōu)于-60 dBc/Hz,在500 kHz 頻偏處的相位噪聲為:

圖12 頻率源1.25 GHz 輸出頻譜

相位噪聲的實測值與基底相位噪聲理論值接近,偏差部分可能來自頻率源電路中外部噪聲輸入引起的惡化。

5 結論

本文針對數(shù)字射頻存儲系統(tǒng)中,對ADC 采樣頻率源的實際需求,設計出基于兩級鎖相環(huán)技術的頻率源電路,能夠實現(xiàn)2.26~2 600 MHz 范圍內任意頻率信號的輸出,且根據(jù)實驗測試結果表明,該頻率源輸出信號在穩(wěn)定度、低相噪方面具有非常優(yōu)異的性能,完全滿足本系統(tǒng)的設計指標,具有切實的應用價值。 同時,該頻率源電路成本低、控制靈活,為雷達電子對抗等諸多領域提供了一個高性能的頻率源解決方案。