QPSK調制解調器的設計與實現(xiàn)

公安部第一研究所 洪向宇

本文基于可編程邏輯陣列設計實現(xiàn)QPSK調制解調器,對QPSK調制解調各模塊算法進行了研究,包括信道編譯碼、成型濾波、載波同步等,并在此基礎上燒寫進FPGA中進行仿真,利用信號分析儀分析調制器的性能。

圖1 QPSK調制解調結構框圖

隨著科學技術的發(fā)展,通信系統(tǒng)已成為各個領域的技術基礎,由于數(shù)字傳輸能夠提供數(shù)據(jù)處理種類的靈活性,因此數(shù)字通信系統(tǒng)正受到越來越多的重視。

數(shù)字調制技術是數(shù)字傳輸?shù)幕A,通過載波調制使數(shù)字信號在信道中傳輸,載波的表達式有三個變量,因此數(shù)字信號調制技術分為幅度鍵控(ASK)、頻移鍵控(FSK)和相移鍵控(PSK)三種方式。其中QPSK是目前最常用的數(shù)字信號調制方式之一,QPSK調制方式的優(yōu)點為頻譜利用率高、抗干擾性強,并且能夠很好的權衡頻帶利用率和接收信噪比的折中要求。本文在FPGA平臺上設計實現(xiàn)QPSK調制解調器。

1 QPSK調制解調器的設計

本文設計的QPSK調制解調系統(tǒng)由10個部分組成。信道編解碼部分采用Turbo交織器的設計;校驗部分CRC校驗算法設計;QPSK調制解調部分;成形濾波模塊和匹配濾波模塊采用根升余弦濾波器實現(xiàn);載波同步采用改進的科斯塔斯環(huán)算法實現(xiàn)。結構框圖如圖1所示。

QPSK調制部分如圖2所示,QPSK調制器包括信道編碼器、CRC校驗、數(shù)據(jù)成幀、數(shù)據(jù)調制、成型濾波等模塊。

圖2 QPSK調制部分結構框圖

圖3 QPSK解調部分結構框圖

圖4 信道編碼部分結構框圖

QPSK解調部分如圖3所示,QPSK解調器包括匹配濾波、CRC校驗、載波同步、定時同步與盲均衡、星座映射、信道譯碼等模塊。

本文使用信道編譯碼算法為利用Turbo碼的信道編譯碼算法,利用卷積、交織、刪余、復用模塊實現(xiàn)Turbo碼的編碼,其中基帶信道編碼器采用Turbo碼中的并行級聯(lián)編卷積算法結構。信道譯碼的結構圖如圖4所示。根據(jù)香農(nóng)信道編碼定理,譯碼過程采用最佳的最大似然譯碼方案。因此信道譯碼過程使用最大似然譯碼算法,譯碼數(shù)據(jù)進入解碼器后,經(jīng)過數(shù)據(jù)緩沖器對數(shù)據(jù)進行緩存操作,并將數(shù)據(jù)輸入解交織器進行解交織操作,從而實現(xiàn)譯碼的迭代運算。如圖5所示。

圖5 信道譯碼部分結構框圖

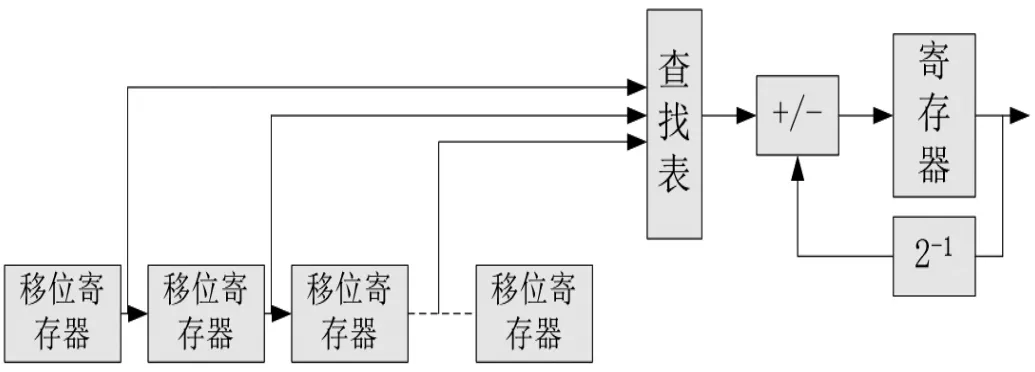

圖6 成型濾波結構框圖

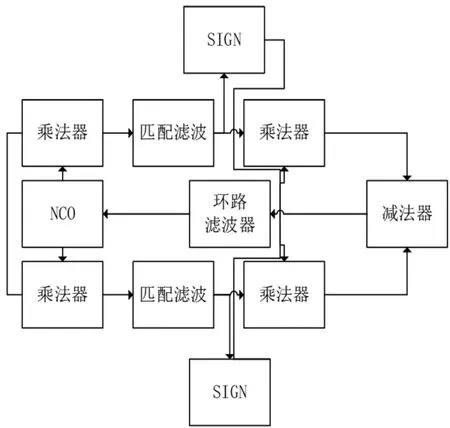

圖7 載波同步系統(tǒng)框圖

本文使用分布式算法實現(xiàn)成形濾波器,分布式算法在FPGA實現(xiàn)中不需要乘法器,而是系數(shù)查找表和移位寄存器實現(xiàn)減小了FPGA的邏輯資源。算法結構圖如圖6所示。

本文采用改進型的科斯塔斯環(huán)設計載波同步,其算法框圖如7圖所示。

本文使用m序列信號發(fā)生器實現(xiàn)CRC校驗。由于算法結構簡單,因此利用移位寄存器的m序列信號發(fā)生器就可實現(xiàn)的CRC校驗。

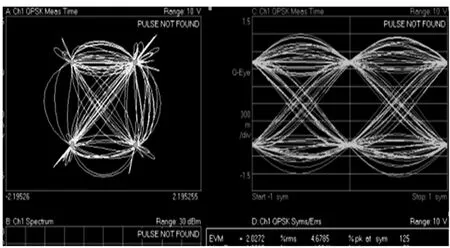

圖8 QPSK的星座圖及眼圖

2 仿真與驗證

將QPSK算法燒寫進FPGA中,利用信號分析儀測設系統(tǒng)的星座圖及眼圖,結果如圖8所示,圖中可以看到QPSK調制的星座點收斂,系統(tǒng)的誤差向量幅度僅為2%,說明調制設計中的幅度誤差和相位誤差極小,驗證了調制系統(tǒng)設計的性能。

結語:本文的設計基于FPGA的QPSK調制解調器。主要研究了信道編解碼算法,成型濾波與匹配濾波算法,CRC校驗算法,載波同步算法等。最終將算法燒寫進FPGA中進行仿真驗證。