基于可見光通信的LED載流子清除電路設計

劉正翔,陳建國,王洪麗

(1.福州職業技術學院 機器人學院,福建 福州 350108;2.福州大學 電氣工程與自動化學院,福建 福州 350108)

0 引 言

自Tanaka等[1]提出可見光通信(VLC)技術以來,由于其不占用傳統無線通信頻帶,且綠色環保、保密性好,使得該技術得到飛速發展。可見光通信使用可控的、快速閃爍的LED傳輸信息,由于人眼無法感知其高速閃爍狀態,使得LED既可用于照明,又有快速傳輸信息的功能[2-3]。遲楠等[4]總結目前國內外的可見光通信研究進展時指出可見光通信急待解決的問題之一就是如何提高LED調制帶寬和系統傳輸速率。Tanaka等[5-6]也意識到LED調制帶寬受限,且在頻率較高情況下,LED無法完全熄滅是因為載流子無法及時釋放,導致LED端電壓無法快速下降。為解決該問題,Tanaka設計了一種用于可見光通信的高速LED載流子清除電路,在LED熄滅瞬間導通MOS管,使LED正負端短路而形成載流子快速釋放回路。該設計雖然可快速縮短LED端電壓下降時間,但該電路使用3個大功率高速MOS管驅動LED,不僅價格昂貴,且功耗較大。隨后Halbritter等[7]提出一種基于電容峰值技術的LED驅動電路,雖然也可快速釋放載流子,但該電路為獲取峰值瞬間電流,要求電路具有較大電流,被動增加電路復雜度,且為防止LED被擊穿,需內部封裝ESD保護。

目前,國內在利用載流子清除方法來改善LED驅動電路性能的研究比較少。謝鑫[8]雖然指出載流子清除電路可用于增加傳輸速率,但并未深入研究該部分內容。夏忠金[9]主要研究Tanaka設計之電路在藍光、紫光LED下的載流子清除性能,但未對降低成本與功耗方面做深入研究。為了獲得較低成本和功耗的LED驅動電路,本研究在不額外增加MOS管的情況下,設計了LED改進電路,在LED熄滅瞬間即接入載流子釋放回路(短路),可使LED快速完全熄滅,進而提升系統性能。

1 LED發射速率受限原因分析

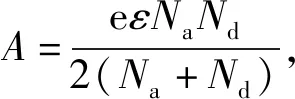

當LED內部PN結附加的正偏電壓增大至PN結的接觸電勢差UD(1.7~2.0 V),耗盡區寬度減小為零。若正偏電壓繼續增大,P區空穴和N區自由電子即可越過PN結,進行空穴與自由電子的復合而釋放出光能。正是由于自由電子與空穴(載流子)的運動,形成了結電容,單位面積結電容計算如式(1)、式(2)[10]所示。

(1)

(2)

式中:Na和Nd分別是P型和N型半導體摻雜濃度;e為1.6×10-19C;ε是材料介電系數;U是LED的正偏電壓。考慮到給定材料的LED參數e、ε、Na、Nd均為常量,設為A,由此得到式(2)所示單位面積結電容表達式。對給定的LED,PN結接觸電勢差UD為某固定值,根據式(2)可知,LED正偏電壓U增大,則結電容變大。也即LED附加正脈沖電壓,結電容快速增大,載流子數量隨之達到最大值。此時若LED端電壓突然消失,式(2)的結電容理論上變為最小,但實際LED中的載流子無法快速釋放,LED端電壓也就無法快速降為零,導致LED實際無法真正熄滅,所以當驅動脈沖頻率增大時,就會出現LED還未熄滅,下一周期的高脈沖已驅動LED再點亮,因此,要使得LED端電壓快速降為零(即LED完全熄滅),需要及時清除結電容里的載流子。

2 現有載流子清除電路分析

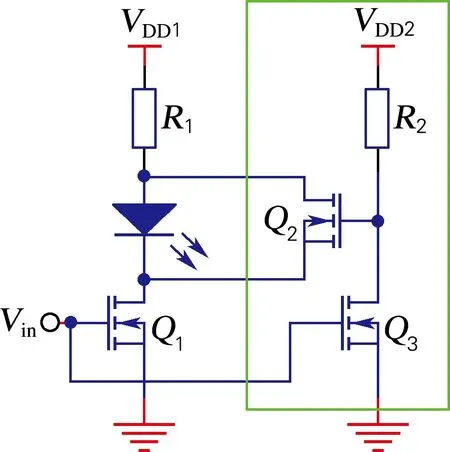

作為可見光通信技術的提出者之一,Tanaka等為提高LED調制速率進行了大量的研究工作,在載流子清除驅動電路方面,提出在LED熄滅瞬間,使其接入一個短路(回路)來釋放載流子[5],如圖1所示。左半部分是傳統的Q1驅動LED電路,右邊綠色實線方框內是載流子清除電路部分。

圖1 LED載流子清除電路Fig.1 LED circuit with drawing-out of carrier

Q3控制Q2,發送Q1的反相電壓至Q2。當Vin驅動LED輸入高電平時,Q1、Q3導通,LED亮,同時Q2關閉,即載流子回路斷開。因此該電路不影響LED點亮操作。當Vin輸入低電平,Q1、Q3關閉,LED熄滅,此時Q2導通,LED被短路,即提供一個釋放載流子的通道。電路看似簡單,卻使得LED熄滅瞬間,接收端電壓波形下降沿時間從56 ns下降為10 ns。然而,該電路在傳統LED驅動電路基礎上增加2個大功率分立高頻器件MGF2407A(Q2和Q3),該器件價格昂貴,雖然能有效清除載流子,但也因此增加了電路的功耗。

3 改進系統電路設計

3.1 載流子清除電路改進

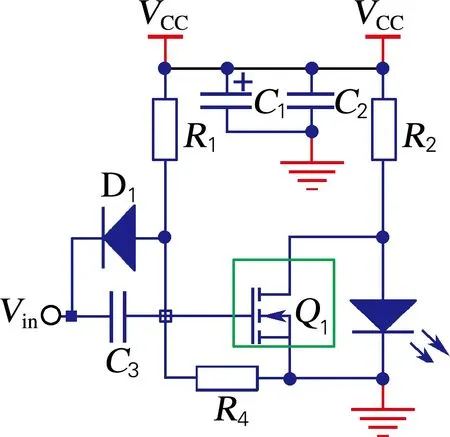

為盡可能減小功耗,設計去掉圖1中的Q2和Q3元件。Q1既用于驅動LED,同時也作為其熄滅瞬間的短接回路,電路圖如圖2所示。當Vin輸入低電平,Q1關閉,由VCC經R2電阻點亮LED。由于Q1關閉,此時并不影響LED點亮。當Vin輸入高電平,Q1導通,LED被短路,LED瞬間熄滅,載流子快速流入GND,即達到快速清除載流子目的。

圖2 改進電路設計圖Fig.2 The improved circuit in this paper

考慮到MOS管的GS端懸空可能會導致自動導通,甚至損壞MOS管。因此接入R4以防止漏極電壓通過寄生電容直接灌到柵極,導致MOS損壞。同時改進電路使用二極管D1和電阻C3并聯,使得在Vin電壓為高電平時,通過隔直電容C3,打開Q1。Vin拉低時,Q1關閉,電容C3被二極管D1短路,加快寄生電容放電,也縮短Q1的關閉時間,有利于高速開關管更快工作。

實驗中的元器件需根據實際電路精準選取,對應元器件清單如表1所示。

表1 驅動電路所用元器件清單Tab.1 List of components used for driving circuit

3.2 改進電路的功率分析

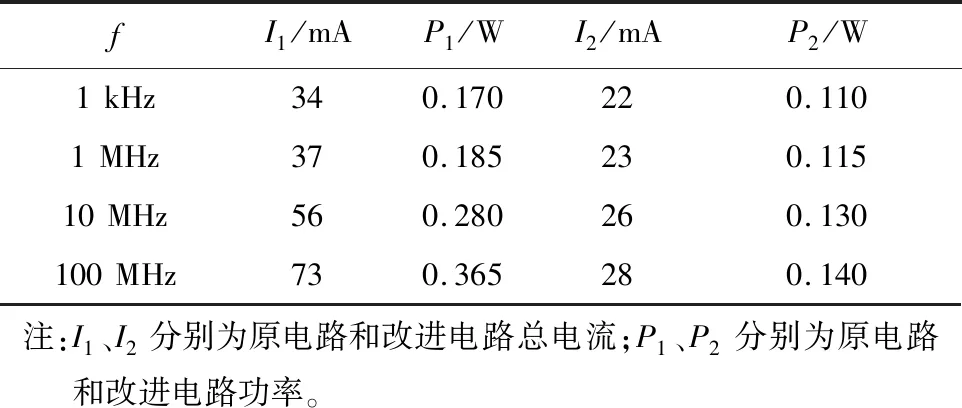

為研究改進電路的功率情況,使用Multisim測試LED驅動頻率在1 kHz~100 MHz時,Tanaka設計的電路與改進電路在功率方面的差異。測試圖2、圖3電路得到的對應數據如表2所示。可見,隨著LED驅動頻率的增大,兩個電路消耗功率均呈現上升趨勢。當頻率超過10 MHz 后,功率遞增量明顯加大,特別是在100 MHz 時,改進電路相比于Tanaka電路,功率只有后者的38.36%。

表2 電路功率對比數據Tab.2 Data of circuit power comparison

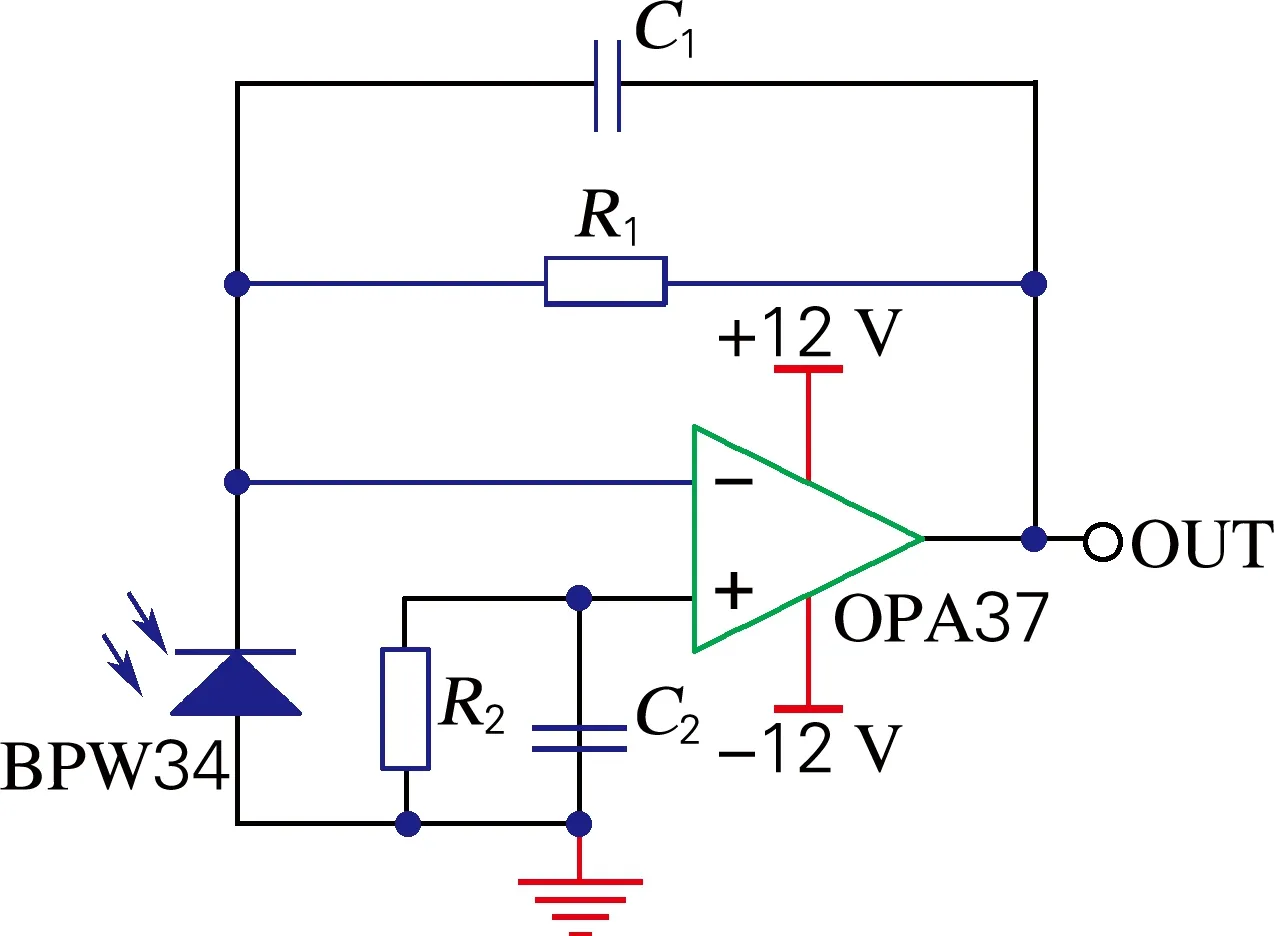

3.3 接收電路設計

為驗證改進電路的通信效果,設計光電檢測電路[11],采用光電二極管BPX65,其信號接收波形的上升沿/下降沿時間為12 ns;采用超低噪聲、高精度運算放大器OPA37芯片,增益帶寬達到63 MHz,以上兩款芯片均滿足本實驗需求,具體電路設計如圖3所示。

圖3 BPX65接收電路原理圖Fig.3 Diagram of BPX65 receiving circuit

該設計只進行光電檢測前置放大電路設計,將BPX65工作于反接短路方式,降低其暗電流,可得到較好的信噪比。為雜散噪聲,將R2并聯C2。R1提供增益,C1為消振電容[12],與R1并聯。

4 實驗與分析

4.1 實驗裝置與實驗過程

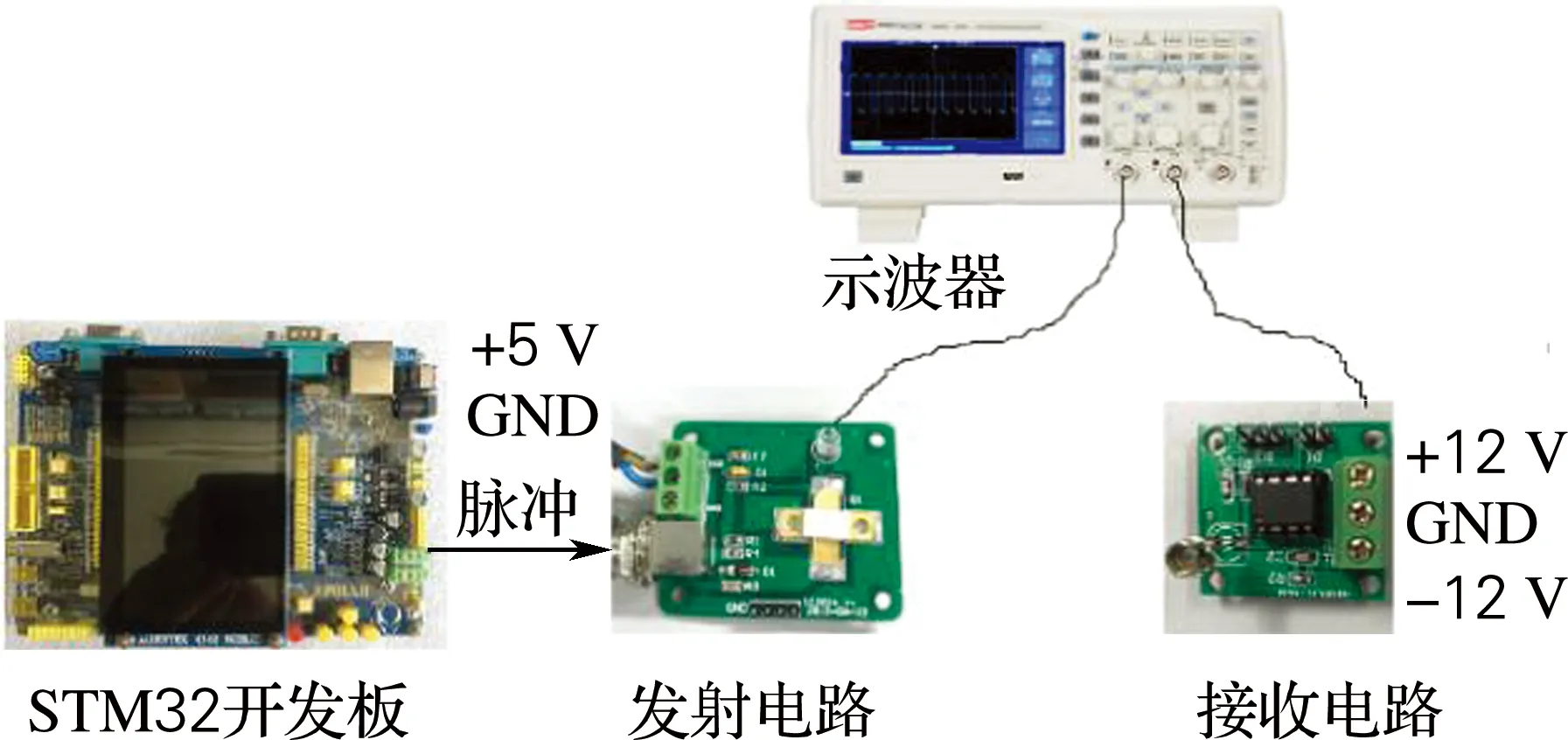

使用電子設計大賽實訓平臺的電源模塊給收發兩端的電路板提供+5 V、+12 V、-12 V、GND。發射端脈沖驅動序列從STM32開發板編程PC5引腳輸出(也可使用函數信號發生器),信號輸出采用BNC雙頭公線連接至發射端。示波器型號選用優利德UTD2102CM,帶寬達100 MHz、采樣率達1 G/s,實驗設備可滿足本實驗需求。發射端電路與接收電路測試實驗裝置如圖4所示。

圖4 實驗裝置示意圖Fig.4 Schematic diagram of experimental device

測試分兩個階段進行。第一階段測試 1 MHz 頻率下,改進電路的載流子清除效果;第二階段進行接收信號測試。兩個階段實驗均對傳統LED電路(關閉載流子清除功能),與改進電路(打開載流子清除功能)的信號進行對比,分析相應性能的改善。

4.2 LED端電壓測試

由于實驗對電流(在PN結內的載流子數量)較為敏感,因此示波器測試端電壓時,采用其兩個通道的正極探頭分別連接LED正、負極,負極探頭接地的方式,在示波器上做兩個通道信號的減法進行測試端電壓。

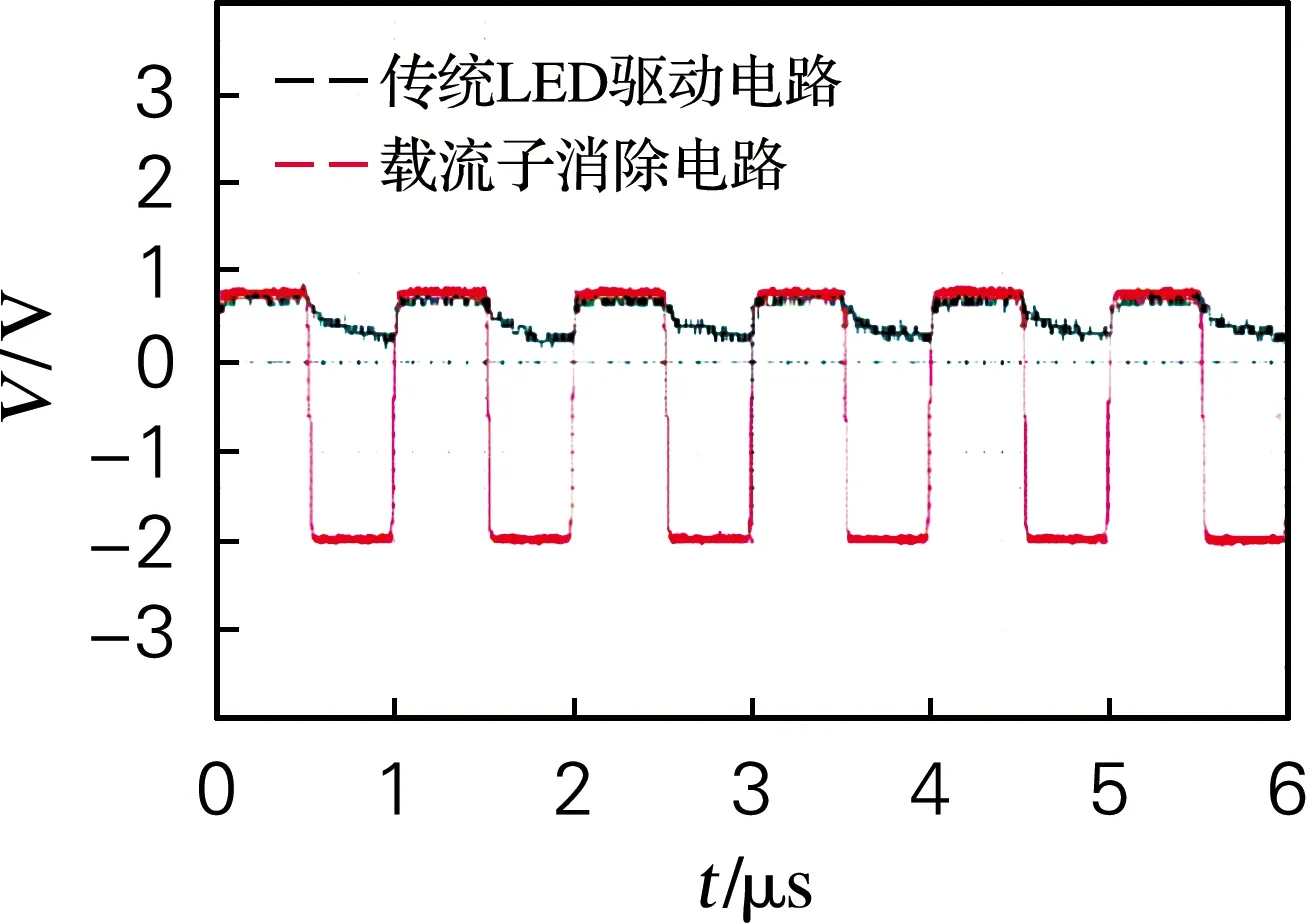

為更好地對比波形,實驗同樣測試了傳統LED驅動電路的端電壓波形,如圖5所示。黑色曲線為傳統LED驅動電路時的LED端電壓波形,紅色曲線為使用載流子清除電路時的波形。

圖5 傳統與改進電路的LED端電壓對比Fig.5 Comparison of LED terminal voltage between traditional and improved circuits

可知,黑色曲線電壓約0.7 V,即為結電容無法快速釋放載流子在端電壓上的反映;紅色曲線波形則為較為規則的矩形脈沖波,端電壓波形下降沿陡峭,說明載流子清除較為及時。同時也可以看出,傳統LED驅動電路在1 MHz脈沖頻率時,下降沿時間甚至超過200 ns,而使用載流子清除改進電路后,高電壓下降時間極短。

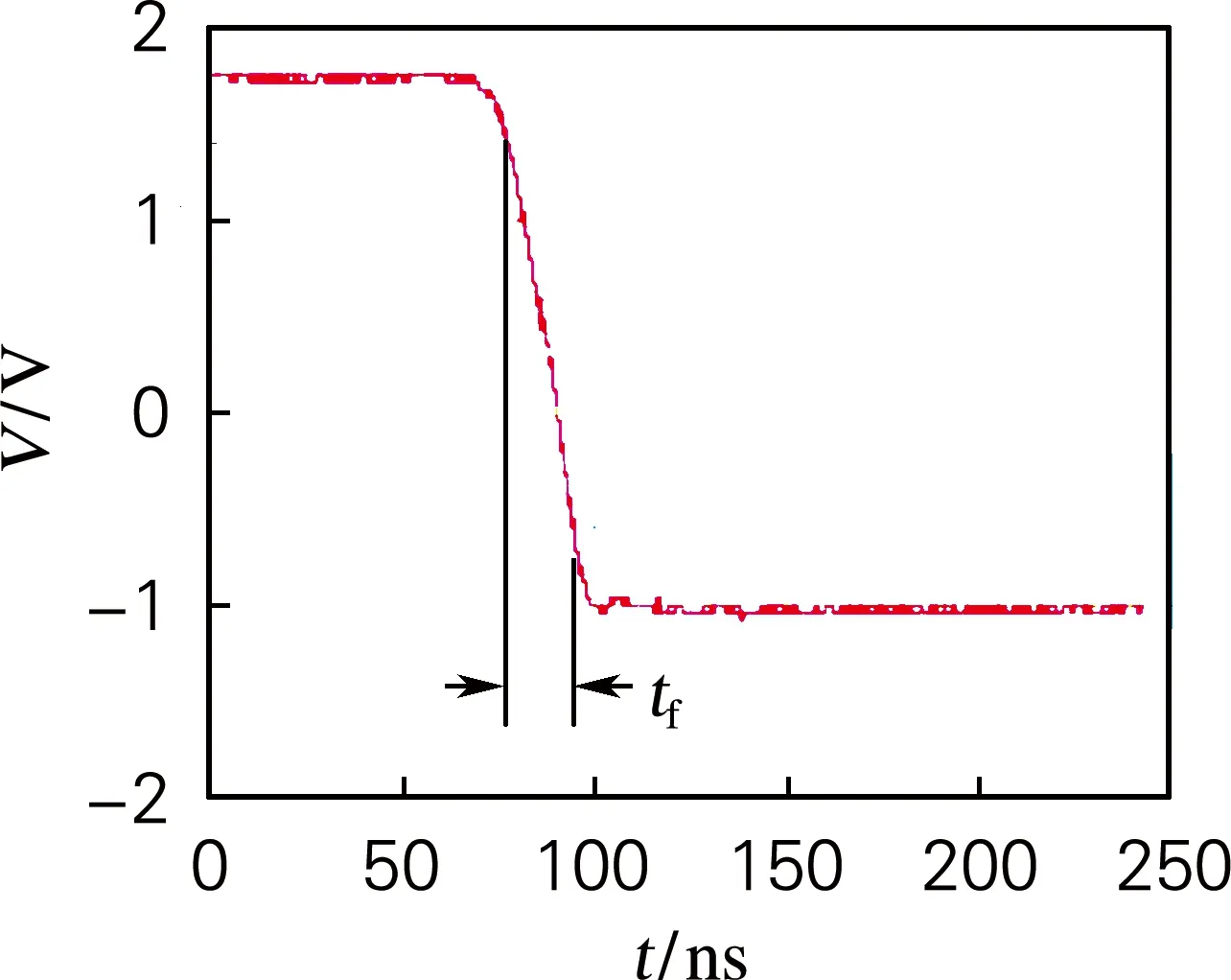

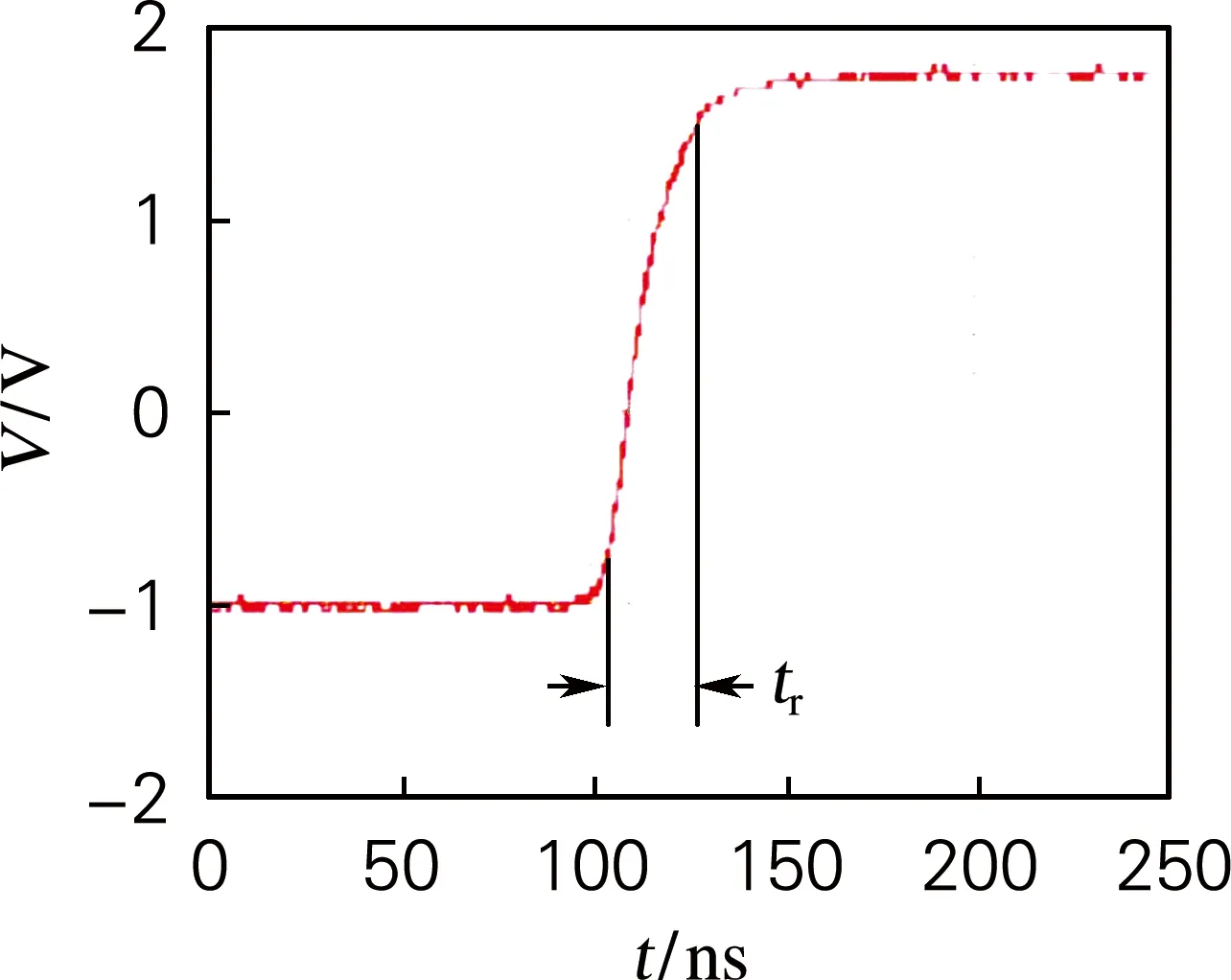

針對載流子清除電路中端電壓的上升、下降時間,如圖6、圖7所示,改進電路的LED端電壓下降沿時間tf僅約15 ns,比傳統電路的下降沿時間200 ns有了很大改善;上升沿時間tr約20 ns,與傳統電路的上升時間幾乎相同。由此可知,改進電路的載流子清除效果良好。

圖6 改進電路LED端電壓下降沿時間Fig.6 The voltage drop time at LED terminal of the improved circuit

圖7 改進電路LED端電壓上升時間Fig.7 The voltage rise time at LED terminal of the improved circuit

4.3 接收信號下降/上升時間

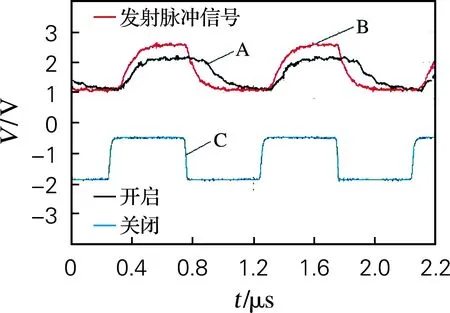

為分析接收信號性能,設置發射頻率為1 MHz 脈沖,使用光電二極管BPX65接收,分別對傳統LED發射電路和載流子清除電路進行測試,得到的接收端波形如圖8所示。為分析方便,黑色曲線為傳統LED電路發射的接收波形,記為A;紅色曲線為使用載流子清除改進電路發射的接收波形,記為B;STM32開發板PC5引腳輸出的脈沖波形,記為C;由圖8可知,在接收端收到的B波形幅值明顯高于A波形,甚至較之高出近50%幅度。同時可以看出,B波形上升至高電平的時間與A波形相近,但下降沿時間明顯小于A波形。經過發射、接收電路后得到的A、B波形,比原始脈沖波形C滯后約15 ns,收發波形的滯后性也將是后續電路改進研究的方向之一。

圖8 開啟與關閉載流子清除電路的接收信號對比圖Fig.8 Comparison of received signals between opening and closing sweep-out carrier circuits

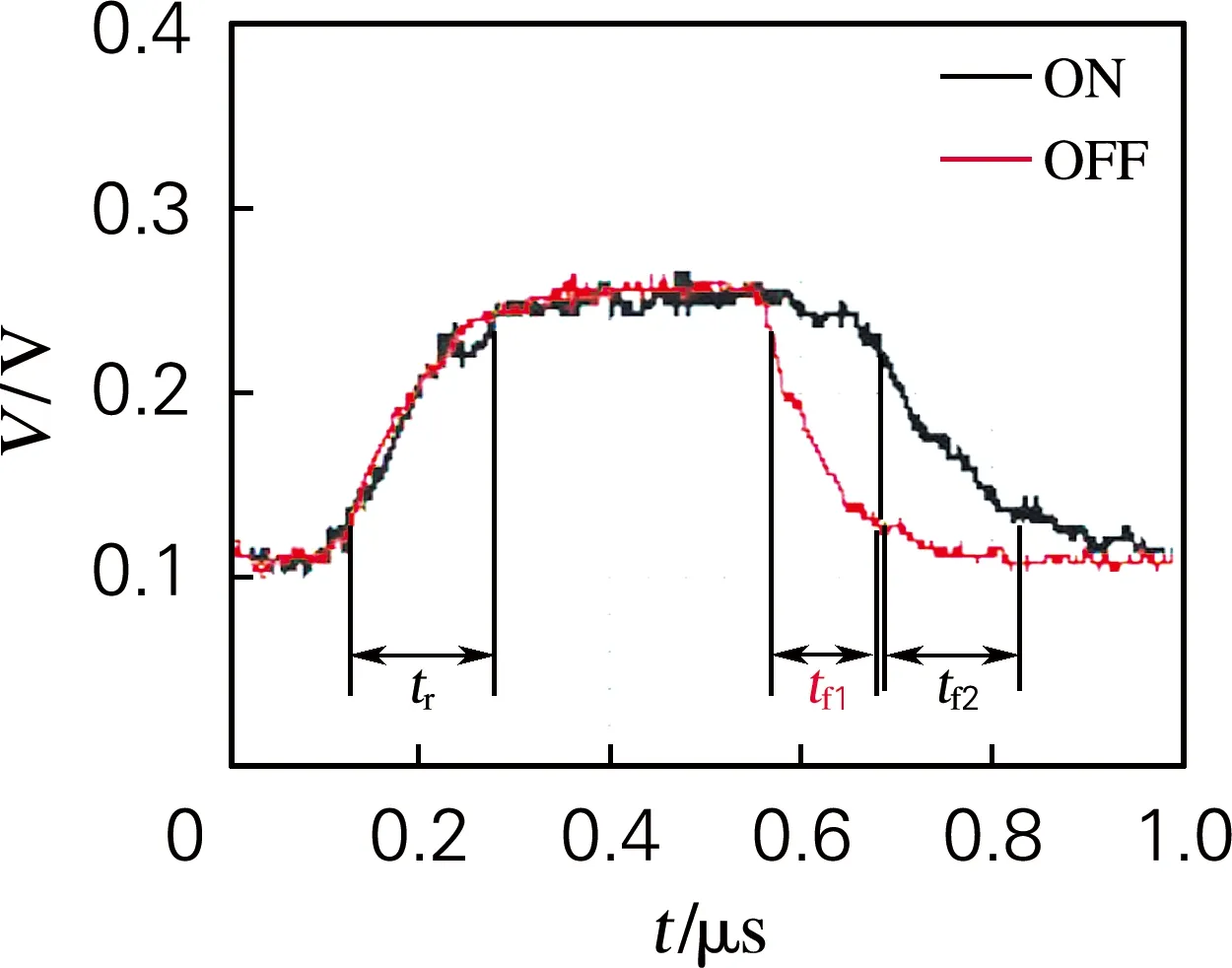

通過圖9所示波形的上升沿/下降沿時間詳細對比,發現傳統LED驅動電路的接收波形(OFF)和改進電路的接收波形(ON),其上升沿時間幾乎一致。但對電壓下降時間tf1和tf2進行對比發現,采用清除載流子改進電路后,接收波形的下降沿時間縮短至約58 ns;不使用載流子清除電路則為85 ns,且該波形延時約40 ns才進入下降沿時間,即相當于用125 ns才降為低電平。

圖9 接收波形上升沿/下降沿時間對比圖Fig.9 Rise/drop time comparison of receiving waveform

5 結束語

通過分析現有的載流子清除電路,進行電路改進,將MOS管用于驅動LED的同時,也作為載流子釋放回路,從而省掉了原電路中的2個MOS管,降低功耗,節省成本。使用該改進電路進行測試,得到的LED端電壓下降時間從傳統電路的200 ns,下降為約15 ns。接收端波形的下降沿時間也從85 ns下降為58 ns,系統性能得到提升。同時實驗過程也出現信號接收延遲問題,將在后續進行深入研究。