寬帶電力線載波通信芯片的FPGA驗證

遲海明,周春良,趙東艷,王于波,唐曉柯

(北京智芯微電子科技有限公司,北京 100192)

隨著微電子技術(shù)的進步,集成電路的發(fā)展日新月異,人們對低成本、低功耗、高性能的芯片設(shè)計不斷地提出更高的要求。片上系統(tǒng)(SoC)設(shè)計理念就是在這樣的追求中發(fā)展了約20年。隨著SoC設(shè)計復(fù)雜度不斷增高,功能驗證的難度也在不斷加大,更加耗時。現(xiàn)場可編程邏輯陣列(FPGA),經(jīng)過約30年的發(fā)展,不僅可以作為單一邏輯功能部件來使用[1-3],更已達到片上系統(tǒng)調(diào)試的性能要求,在容量上可以通過一片或多片F(xiàn)PGA裝下整個SoC的數(shù)字部分[4]。FPGA原型驗證是將SoC數(shù)字部分以及一部分數(shù)模混合部分,一致的或通過一定約束的改變,映射到FPGA中進行軟硬件協(xié)同開發(fā)調(diào)試。其目的,一是為了對設(shè)計有直觀的了解,可以在芯片流片前展示整個系統(tǒng)的設(shè)計概念,做協(xié)議互聯(lián)互通測試;二是希望軟件可以和硬件同步開發(fā),提高整個系統(tǒng)的開發(fā)效率;三是可以作為參考模型輔助芯片調(diào)試。文中以最新一代電力專用寬帶電力線載波通信芯片為例,介紹FPGA原型驗證的設(shè)計流程以及應(yīng)用。

1 寬帶電力線載波通信芯片

1.1 研發(fā)背景

隨著智能電網(wǎng)建設(shè)的推進,通信速率低、可靠性差的窄帶電力線載波通信技術(shù)作為本地接入方式,已不能滿足用電信息交互的需求。在這樣的背景下,寬帶電力線載波通信技術(shù)規(guī)范得以提出。基于國家電網(wǎng)新標準[5]并兼容南方電網(wǎng)標準[6]的高速寬帶電力線載波通信芯片[7-8],從提出經(jīng)過不斷增強,目前已經(jīng)大規(guī)模量產(chǎn)[9-12]。

1.2 芯片結(jié)構(gòu)

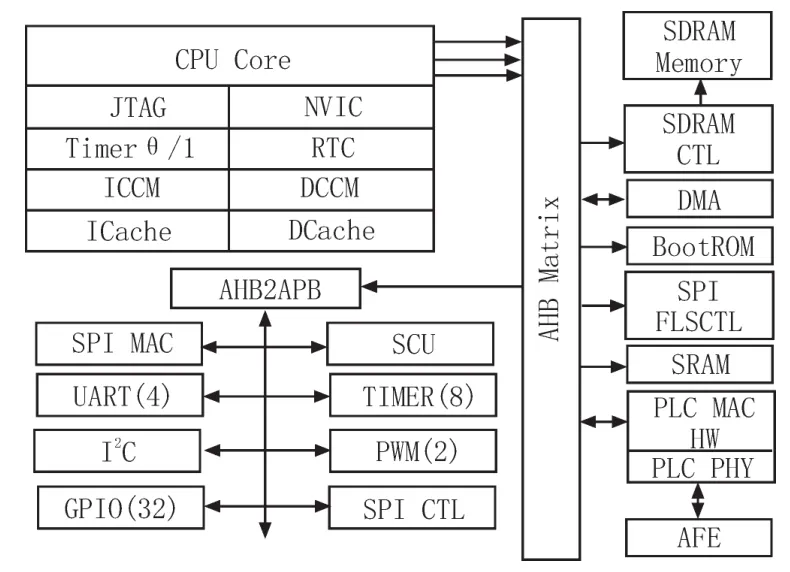

芯片結(jié)構(gòu)如圖1所示。芯片采用AMBA總線架構(gòu),第一級為32位AHB總線。主設(shè)備包括CPU核和系統(tǒng)DMA控制器。從設(shè)備有SDRAM控制器及其配置接口、系統(tǒng)DMA控制器、SPI Flash控制器、BootROM、SRAM控制器、AHB2APB橋以及電力載波通信加速器(PLC)。第二級總線為APB總線,連接的設(shè)備有定時器、PWM模塊、GPIO接口、UART接口、SPI接口、I2C接口以及系統(tǒng)控制單元(SCU)。芯片的模擬部分包含低抖動的系統(tǒng)PLL以及高性能、低功耗的模擬前端(AFE)。其中,AFE又包含高精度模數(shù)/數(shù)模變換器(AD/DA)、低通濾波器(LPF)以及可控增益放大器(PGA)。

圖1 芯片結(jié)構(gòu)

1.3 電力載波通信物理層設(shè)計

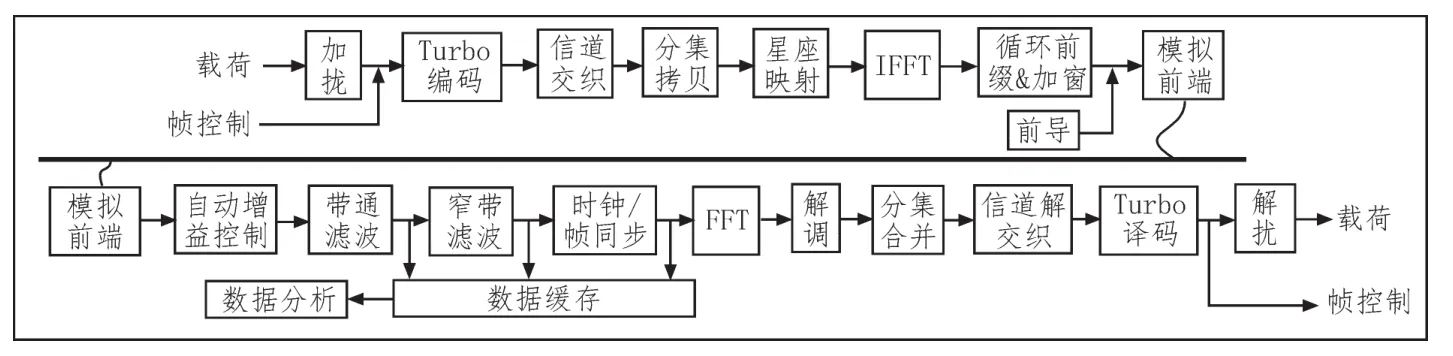

FPGA原型驗證的主要工作是對載波通信物理層加速器進行協(xié)議驗證及性能驗證。物理層收發(fā)結(jié)構(gòu)如圖2所示。包括:加擾/解擾、信道Turbo編碼/解碼、信道交織/解交織、分集拷貝/分集合并、星座映射/解映射、IFFT/FFT、同步定時、數(shù)字前端以及信道數(shù)據(jù)采集。

圖2 物理層收發(fā)結(jié)構(gòu)

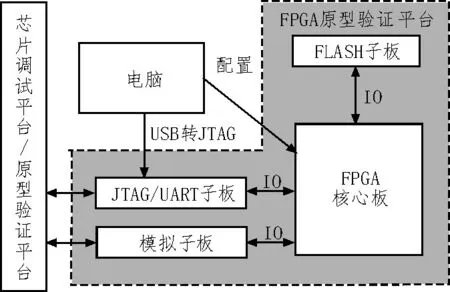

2 FPGA原型驗證平臺設(shè)計

對于一個很大的ASIC設(shè)計,如果資源有限,就不得不將設(shè)計進行分割映射到多片F(xiàn)PGA,通過接口互聯(lián)來實現(xiàn)原本內(nèi)部信號的連通[13]。這對板級設(shè)計以及調(diào)試帶來更大的難度,應(yīng)盡量避免。文中FPGA驗證平臺環(huán)境分為硬件和軟件兩部分,如圖3所示。硬件部分的主體是帶有Virtex7 2000T-FLG1925的核心板。2000T-FLG1925型號可以支持到2 000萬門的ASIC設(shè)計[14],足夠容納所述設(shè)計的數(shù)字部分。核心板具有專用高速I/O接口,連接JTAG/UART子板、模擬子板和FLASH子板。軟件部分包括FPGA設(shè)計軟件VIVADO、FPGA核心板配置軟件以及SoC驅(qū)動開發(fā)/調(diào)試環(huán)境 Metaware IDE/Debugger(MDB)。

圖3 FPGA原型驗證平臺結(jié)構(gòu)

PC機USB口通過DigilentJTAG仿真器連接到JTAG/UART子板,負責加載驅(qū)動程序以及載波信息數(shù)據(jù)傳輸。FLASH子板作為程序數(shù)據(jù)存儲區(qū)。模擬子板負責數(shù)模/模數(shù)轉(zhuǎn)換、濾波和放大,最終信號可耦合到電力線或同軸電纜進行收發(fā)。

3 FPGA設(shè)計流程

3.1 前端設(shè)計移植

FPGA與芯片前端設(shè)計的不同之處在于硬件單元種類有限、結(jié)構(gòu)固定、連接關(guān)系冗余[15]。因此要將不能映射到FPGA中的部分進行移植,改變時鐘及所涉及路徑的約束。文中所述設(shè)計移植的原則是:只進行獨立IP的替換及與之相關(guān)的邏輯修改,最大限度保證芯片與FPGA設(shè)計的一致性。芯片中的系統(tǒng)PLL部分替換為時鐘管理(MMCM)資源,去掉大部分時鐘門控機制并將其余改為數(shù)據(jù)門控。模擬IP替換為片外性能相近的第三方芯片,內(nèi)部與模擬IP相關(guān)接口根據(jù)第三方芯片進行修改并引到FPGA管腳。對第三方模擬芯片的控制也做了相應(yīng)的增加。

3.2 前端設(shè)計驗證

在上板調(diào)試FPGA前,應(yīng)首先對移植的設(shè)計進行功能驗證。如果前端設(shè)計階段進行的功能驗證不夠充分,依靠在板級調(diào)試階段通過內(nèi)建邏輯分析(Chipscope)手段去排查邏輯功能錯誤,既耗時又難以獲取足夠的觀察時間及信號數(shù)目。通過復(fù)用基于覆蓋率驅(qū)動的芯片驗證環(huán)境[16]進行FPGA設(shè)計驗證,保證功能檢驗結(jié)果的一致性。對于功能而言,不針對FPGA額外構(gòu)建測試用例,而是復(fù)用已有的芯片測試用例,從功能的角度考察移植是否正確。對于外部接口電路的改動,可以構(gòu)建針對FPGA的特殊用例。除了針對第三方模擬接口做了單獨的驗證用例外,其余均復(fù)用芯片驗證用例,功能覆蓋率達到100%。

3.3 FPGA設(shè)計軟件流程及實現(xiàn)結(jié)果

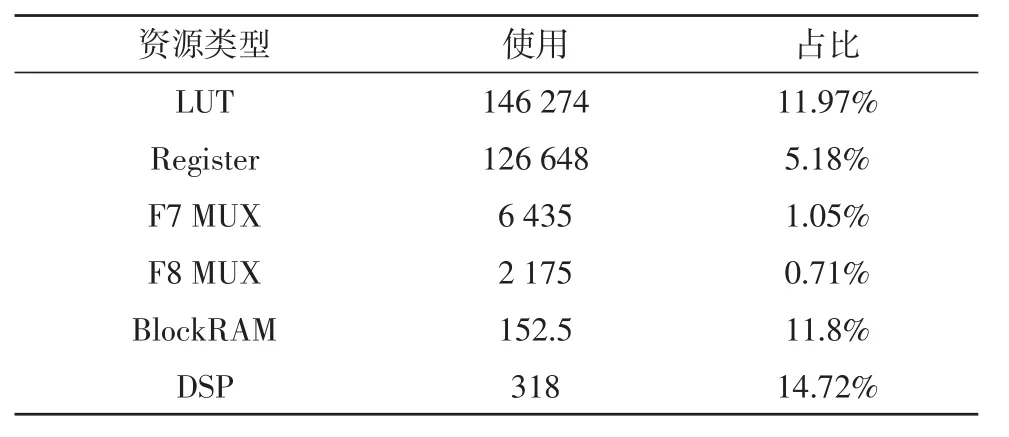

設(shè)計采用Synopsys的Synplify進行綜合,以輸出更好的綜合結(jié)果。將PRJ格式的設(shè)計及策略腳本文件與FDC格式的約束文件輸入綜合工具,綜合輸出EDF格式的網(wǎng)表文件。然后,將EDF網(wǎng)表文件及XDC格式的時鐘及管腳約束文件通過TCL腳本文件附帶一定的工具策略輸入到Vivado進行布局布線,輸出用于FPGA下載的BIT文件。最終時序分析報告沒有出現(xiàn)時序違例,所占資源結(jié)果如表1所示。

4 FPGA原型驗證平臺應(yīng)用

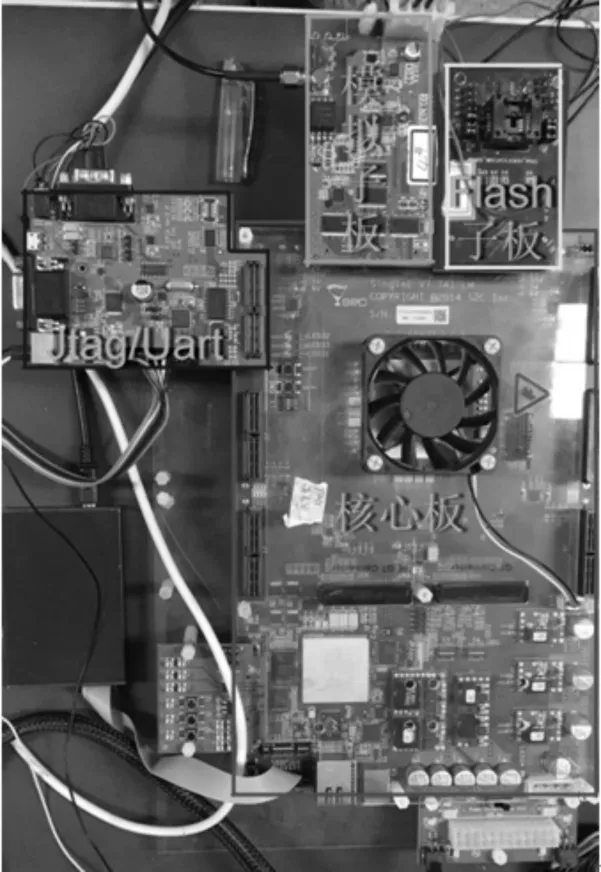

FPGA原型驗證板級調(diào)試主要通過驅(qū)動軟件對原型設(shè)計進行操作,測試CPU、總線、接口以及電力線載波物理層加速器的功能。圖4是FPGA硬件平臺實物圖。將功能子板插接到核心板的專用高速I/O接口,從而連接到FPGA的管腳。利用核心板配置軟件配置FPGA,用DigilentJTAG仿真器連接PC機USB口和Jtag/Uart子板,啟動Metaware IDE,在線修改寄存器值,觸發(fā)硬件操作,觀察各部分硬件功能是否達到預(yù)期結(jié)果。在產(chǎn)生新的系統(tǒng)需求時,通過修改RTL代碼重新回歸FPGA自動化流程,實現(xiàn)快速評估。協(xié)議軟件通過采用Metaware IDE在線調(diào)試,實現(xiàn)軟硬件協(xié)同開發(fā)。

表1 FPGA資源占用結(jié)果

圖4 FPGA硬件平臺

通過搭建兩套驗證平臺,實現(xiàn)物理層在不同調(diào)制模式下的收發(fā)功能。用帶可調(diào)衰減的同軸線連接收端和發(fā)端模擬板同軸接口。用串口線連接收端和發(fā)端的Uart子板的RS-232串口。將編譯好的接收端驅(qū)動程序用MDB通過DigilentJTAG仿真器下載到接收端Flash子板中,然后將仿真器接到發(fā)送端Jtag子板,通過命令行觸發(fā)測試啟動。原始信息通過發(fā)送端Jtag子板傳入FPGA進行發(fā)送端處理,調(diào)制信號耦合到模擬線路。調(diào)節(jié)可調(diào)衰減器可模擬線路衰減行為,接收端在解調(diào)后將信息通過串口傳回發(fā)送端,發(fā)送端校驗后更新測試結(jié)果的報表信息。等所有調(diào)制模式遍歷測試結(jié)束,查看最終報表,可知所遍歷的模式全部成功。

通過將發(fā)送或接收端FPGA原型驗證平臺替換為協(xié)議電表模塊,并將模塊通過串口連到PC機,通過模塊軟件配置電表與平臺之間以不同調(diào)制方式進行信標幀通信,查看串口上報的CRC校驗結(jié)果來判斷協(xié)議的一致性。

5 結(jié) 論

文中針對寬帶電力線載波通信芯片的原型驗證需求,介紹了一種FPGA原型驗證平臺,描述了基于此平臺的FPGA開發(fā)流程及實現(xiàn)結(jié)果。通過載波通信物理層收發(fā)調(diào)制模式遍歷的測試以及協(xié)議一致性測試,說明平臺的調(diào)試方法達到預(yù)期目的。在芯片回片后,可將接收或發(fā)送平臺之一替換為芯片基板,為芯片調(diào)試提供協(xié)助。多套平臺還可連入電力線組網(wǎng),為上層軟件的早期調(diào)試提供載體。