基于 Verilog HDL 的多周期 CPU 設計與實現

嚴浦洲 合肥工業大學 計算機與信息學院計算機與信息工程系

引言

早期CPU都是單周期的,結構簡單,即讓CPU每個時鐘周期執行一條指令。但有的指令執行耗時長,有的指令執行耗時短,且CPU是執行完一條指令再處理下一條的,既然給每個指令的時鐘周期都是相同的,那么時鐘周期就是耗時最長的指令所需的時間。后來人們意識到了計算機的巨大能力,這時為了提升CPU的速度,優化CPU的結構,對指令集的所有指令作分析,可以發現它們處理過程有相同的地方,于是便可將所有的指令切成幾段基本操作,指令執行過程由多個基本操作組成,便引入了多周期CPU結構。

1 設計原理

多周期 CPU 是將單條指令的執行劃分為若干個工作周期,每個工作周期用一個時鐘周期完成,每條指令的具體功能決定了完成該指令需要的工作周期數目。指令執行過程中狀態的轉換由有限狀態機進行實現,控制單元根據指令和其所處工作周期發出為操作命令信號來控制指令的執行。CPU在處理指令時,一般需要經過以下幾個階段:

(1) 取指令:根據PC中的指令地址,從存儲器中取出一條指令,同時PC根據指令字長度自動遞增產生下一條指令的指令地址。(2)指令譯碼:對指令進行分析并譯碼,確定這條指令需要完成的操作。(3)指令執行:根據指令譯碼得到的操作控制信號,具體地執行指令動作。(4)存儲器訪問:所有需要訪問存儲器的操作都將在此步驟執行,該步驟給出存儲器的數據地址,把數據寫入到存儲器中數據地址所指定的存儲單元或取出。(5)結果寫回:指令執行的結果或者訪問存儲器中得到的數據寫回相應的目的寄存器中。

2 總體設計

2.1 指令類型、格式

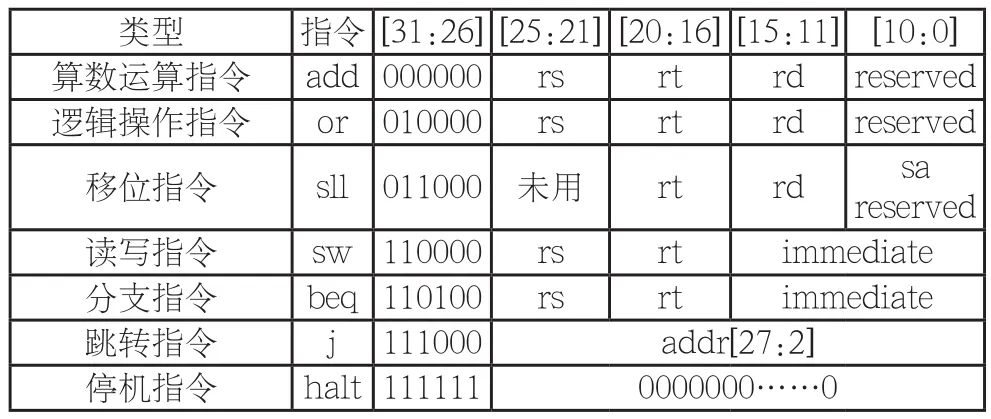

表1 指令格式(每種類型以一條指令為例)

op:操作碼;rs:只讀寄存器;rt:可讀可寫,目的操作數寄存器;rd:只寫寄存器;sa:位移量;funct:功能碼;immediate:16位立即數,用作操作數、數據加載(load)/數據保存(store)指令的數據地址字節偏移量和分支指令中相對程序計數器的有符號偏移量;address:地址。

2.2 狀態轉換圖

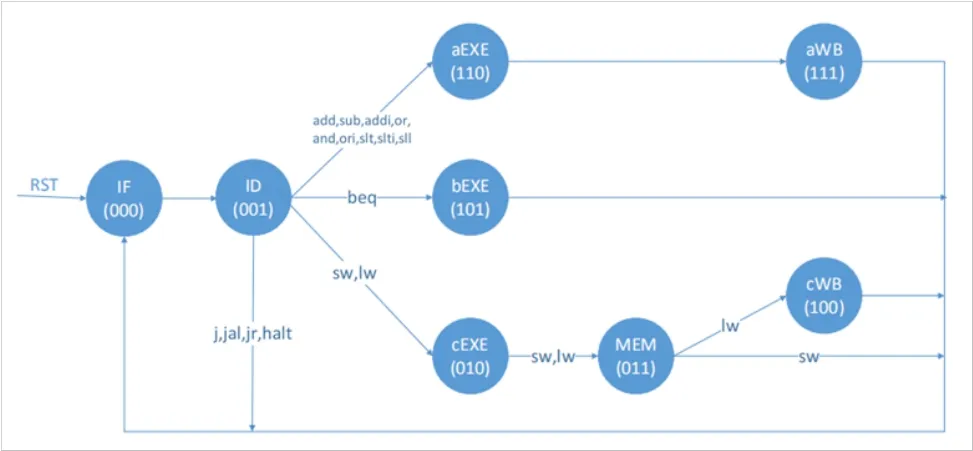

圖2 各指令執行的狀態轉換圖

首先為每個狀態定義一個參數,例如定義IF為000,ID為001等。對于EXE狀態,由于分支指令,存取指令和其他指令經過的指令執行階段各不相同,故定義了aEXE,bEXE,cEXE三個狀態;對于WB狀態,由于sw和lw經過的指令執行階段不相同,故定義了aWB,cWB兩個狀態。當輸入NextState的狀態碼與操作碼發生改變時,使用case產生下一狀態,對case的設計如下:(1)由于所有指令都需要經過IF-ID階段,所以IF的nextState一定是ID。(2)對于ID階段,有四條分叉的支路:對于j,jal,jr,halt指令,它們直接跳轉,不需要經過后面的狀態則nextStste為IF;其它指令的nextState是EXE。當指令是sw、lw指令時,指令的nextState為cEXE;當指令是beq指令時,指令的nextState為bEXE;剩余的指令nextState為aEXE。(3)對于aEXE,各種運算指令的結果無需寫回存儲器,故nextState為aWB;對于bEXE,分支指令的nextState為IF;對于cEXE,由于是存取指令,需要經過存儲區,故nextState自然為MEM。(4)對于MEM,如果是lw指令,則要將結果寫回寄存器,那么nextState為cWB;如果是sw指令,則無需寫回,那么nextState為IF。(5)aWB與cWB的nextState都為IF。

2.3 主要功能部件描述

(1)PC

根據控制信號PCSrc,計算獲得下一個PC以及控制信號RST重置。根據復位信號RST、PC寫使能信號PCWre決定輸出的pc值。與PC相關的部件還有PCAddFour:獲取順序存儲的下一個地址;PCJump:獲取子程序地址;PCAddImm:獲取跳轉后的地址。

(2)指令存儲器

定義8位的寄存器數組,將指令的32位二進制數分割成4個8位的小段并順序存儲在數組中。

(3)寄存器堆

根據指令中的rs,rt到對應寄存器堆中獲取數據,得到要讀的數據,然后根據rd將輸入的數據存到對應的寄存器中。

(4)算術邏輯單元

在輸入A、輸入B以及ALU控制信號ALUOp發生變化時,使用case并根據ALUOp的值執行對應的操作得到計算的結果。

(5)數據存儲器

定義8位的寄存器數組,將32位的數據分割成4個8位的小段進行存取。寫與讀操作的單位是8位二進制數,—共操作四次。大端方式存儲。

(6)數據選擇器

二選一數據選擇器用于選擇ALU的A操作數,B操作數;選擇存入寄存器的數和選擇寫入寄存器的數;三選一數據選擇器選擇要寫入數據的目的寄存器是rt,rd還是31號寄存器;四選一數據選擇器用于選擇下一條指令的地址。

(7)控制單元

控制單元由三個模塊封裝組成。分別實現當時鐘上升沿到來時進行狀態切換;產生下一階段;根據當前狀態和操作碼產生各部件的控制信號三種功能。

(8)其他

臨時寄存器ADR,BDR,ALUtoDR,DBDR在時鐘信號觸發下將寄存器中的內容輸出;指令寄存器IR用于存放正在執行的指令代碼。

3 測試仿真

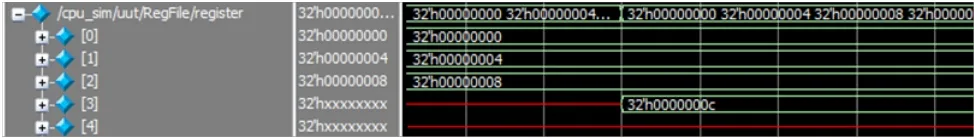

以指令add $3,$2,$1 (指令編碼為000000 0 0 0 1 0 00001 0001100000000000)為例。

4 結語

與單周期CPU設計相比,多周期CPU的數據通路上發生了一些較為明顯的變化。增加了一定數量的臨時寄存器存儲關鍵數據,這是由多周期指令特性決定的。同時,多周期cpu的設計運用了有限狀態機的思想,每個指令在不同的時鐘周期里,其控制信號完全不同,所以需要狀態機來控制狀態,并且根據不同指令的不同狀態來決定控制信號的輸出,這在單周期cpu里是沒有體現的。所以多周期CPU具有時鐘周期短、各功能部件可共享的優點,它既符合現代CPU的真實設計,又是流水線CPU設計的基礎。最后通過軟件仿真驗證,來證實所設計的CPU的正確性,可以看到所設計的CPU具有實用性。