高速接口電路發送器的設計*

呂新為

(西安郵電大學電子工程學院 西安 710121)

1 引言

隨 著 高 速 模/數 轉 換 器(Analog-to-Digital,ADC)和數/模轉換器(Digital-to-Analog,DAC)分辨率和采樣率的不斷提高,對數據轉換器接口的性能要求不斷提高[1]。多路并行傳輸方式由于碼間干擾[2]、信號偏移等問題限制了應用速度和傳輸距離[3],并且還增加芯片引腳設計和板級布線與系統互聯的硬件開銷,直接增加系統成本[4]。而串行傳輸節約設計成本與空間、應用更靈活等優勢使得高速串行接口電路成為高速轉換器接口電路的首選,用于解決高速轉換器與FPGA之間的傳輸問題。不僅可以克服并行數據傳輸帶來的性能下降問題,同時可支持更高速數據傳輸。此外還降低了I/O需求及封裝尺寸,降低靜態功耗節省系統成本。

本文主要針對高速接口電路發送器[5]進行研究,高速接口電路發送器主要實現并行數據到高速串行數據的轉換與傳輸,并解決高頻信號傳輸時所帶來的信號完整性問題[6]。發送器包含并串轉換電路、CML驅動電路[7]及阻抗匹配電路三個模塊。并串轉換電路實現10∶1數據串化,串行數據最高位速率可達3.125Gbps,CML驅動電路將串化后的信號以差分信號傳輸到片外,阻抗匹配電路實現單端50Ω電阻匹配。本文采用SMIC 0.18μm工藝實現完整的高正高速接口發送端電路并進行電路功能的仿真驗證。

2 發送器的設計

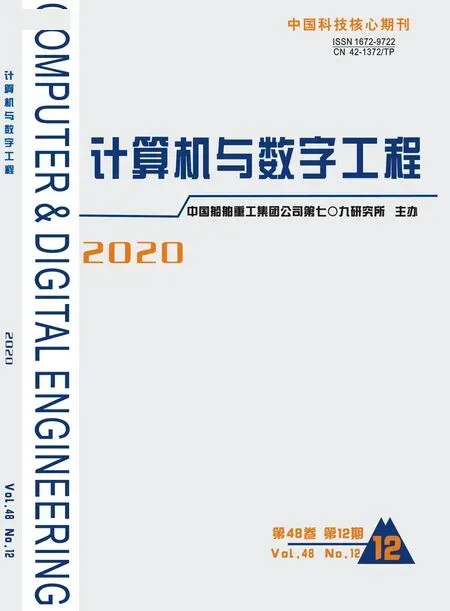

高速接口電路包含發送器和接收器,發送器將多路并行的數字信號轉換為適合信道傳輸的串行模擬信號并將其傳輸到信道上,而接收器將信道傳輸過來的數據進行處理重新恢復成多路并行數據。圖1所示為高速接口電路發送器結構示意圖,發送器包含時鐘控制信號產生、并串轉換電路、CML驅動電路及阻抗匹配電路。時鐘控制信號產生與并串轉換電路實現并行數據到串行數據的轉換[8],CML驅動電路將串化后的數據以差分信號形式按照要求傳輸到信道上,阻抗匹配電路解決高頻信號傳輸時由于阻抗不匹配而產生的信號完整性問題。

圖1 高速接口電路發送器結構示意圖

2.1 并串轉換電路的設計

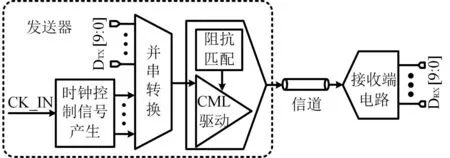

本文設計的并串轉換電路是將位速率為312.5Mbps的10路并行數據轉換為3.125Gbps的1路10位串行數據,圖2所示并串轉換電路整體結構,包含控制信號產生模塊及并串轉換模塊。控制信號模塊是對輸入時鐘信號進行分頻,實現10:1并串轉換的時鐘,包含二分頻與五分頻電路;并串轉換模塊則是實現10路數據1路數據的串化過程,包含5∶1并串轉換和2∶1并串轉換。

圖2 10∶1并串轉換電路結構框圖

時鐘信號CK_IN通過二分頻電路產生一對反相的時鐘信號CK_A與CK_B,其頻率f=781.25MHz,用于產生五分頻時鐘信號以及控制實現2∶1并串轉換;時鐘控制信號CK_A與CK_B通過五分頻電路產生兩組控制信號:占空比均勻的CK_D、占空比為1∶4的5對反相的時鐘控制信號CK_i_M/CK_i_N(i=1~5),控制電路實現5∶1并串轉換。

并串轉換模塊包含5∶1并串轉換和2∶1并串轉換,輸入數據信號為10路并行數據D0~D9,其位速率為312.5Mbps。將輸入數據分為兩組通過5∶1并串轉換模塊得到輸出信號Data1和Data2,其中Data1與Data2的位速率為1.5625Gbps;Data1與Data2再通過2∶1并串轉換電路實現并串轉換,得到的信號為OUT1、OUT2,并且OUT2是OUT1的反相信號,此時完成了傳輸數據的10∶1并串轉換,數據的位速率為3.125Gbps。

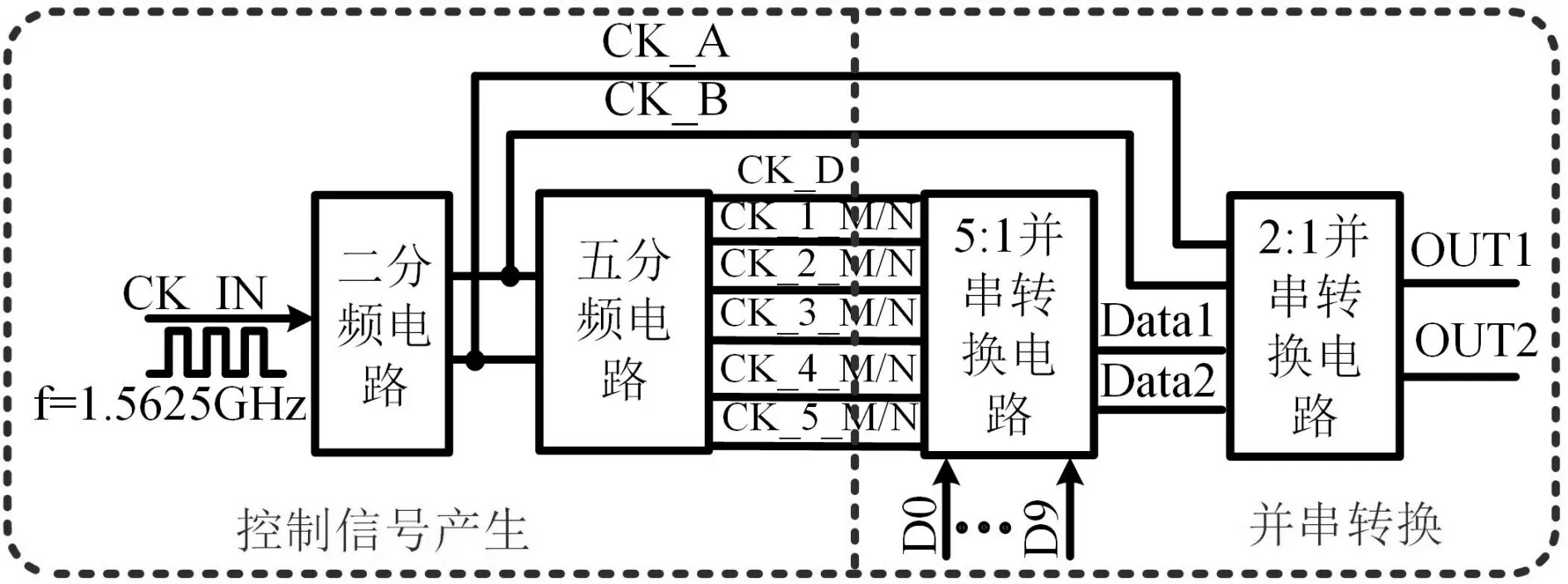

圖3 時鐘控制信號時序圖

圖3 為時鐘控制信號時序圖,輸入時鐘信號CK_IN的周期為T=640ps,其通過二分頻后得到CK_A與CK_B反相且周期為T=1.28ns,通過五分頻電路得到的時鐘信號CK_D、CK_i_M/CK_i_N(i=1~5)其周期均為T=6.4ns,但是CK_D信號占空比均勻,CK_i_M/CK_i_N信號占空比為1∶4,CK_i_N與CK_i_M波形對應且反相,并且一組信號從CK_1_M到CK_5_M其上升沿逐次延遲640ps。

2.2 CML驅動電路的設計

CML驅動電路在高速接口電路中負責將片內數據傳輸到片外介質上,并保證數據具有一定的驅動能力。

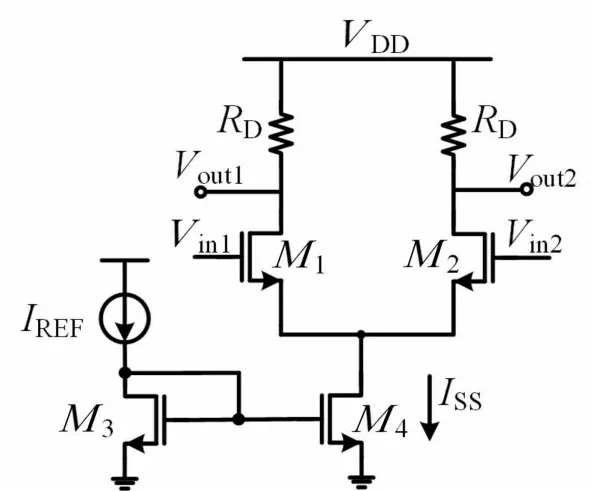

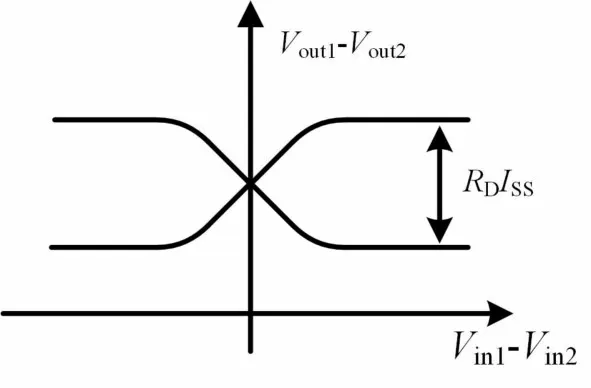

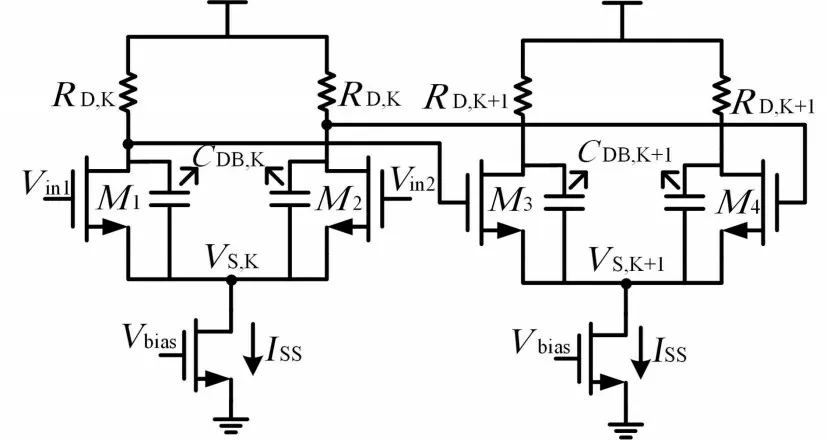

本文設計的CML驅動電路以差分對形式為基礎,多級錐形級聯的形式增強驅動能力[9]。圖4為單級電路結構,為保證電路能夠工作在較高的速度,差分對管M1至M4均應工作在飽和區,尾電流源ISS為電路提供了一個獨立于輸入的偏置。單級電路要實現最好的性能則尾電流需處于全切換狀態[10],尾電流處在全切換狀態時電路輸出的差分擺幅僅是負載電阻和尾電流的函數。

圖4 單級電路結構

圖5 輸入輸出特性

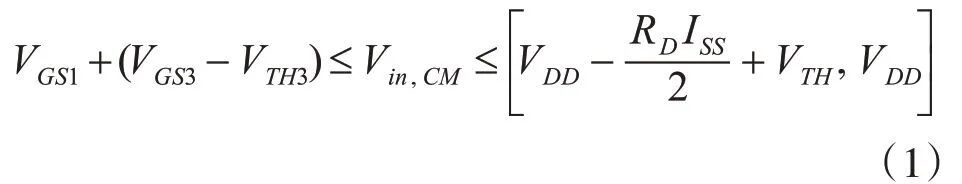

為保證電路能夠工作在較高的速度,CML buffer的差分對管、均應工作在飽和區,且尾管也應保持在飽和區,這樣將得到輸入共模電平的范圍:

其中VGS為晶體管的柵源電壓,VTH為晶體管閾值電壓。圖5為差分電路的輸入輸出特性曲線,差分輸出擺幅受MOS閾值電壓的限制[11],最大差分輸出擺幅為

在級聯時,上一級的輸出擺幅即為下一級的輸入擺幅。此處要注意的是,在主驅動電路的最后一級考慮阻抗匹配[12]其電阻R=50Ω,由于本設計中對輸出擺幅要求為500mV,因此所選MOS管器件的閾值電壓VTH≥500mV。

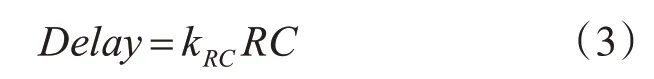

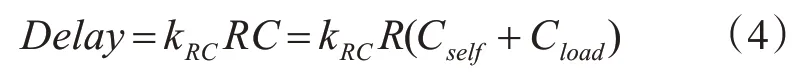

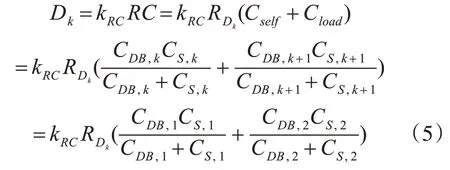

為了增大電路的驅動能力,同時使電路的延時達到最小,本文中采用多級級聯的方式,將總的延時平均分到每一級上,這樣每一級管子的尺寸和電流都是以一個相同的比例u來逐級增大的。本文采用數字電路中常用的計算延時的RC延遲模型[13],確定電路的級數N和比例常數u。其延時Delay如式(3)

其中,kRC是對數項,R為等效電阻,C為等效電容。對于CML電路來說,其延時同樣可以用該模型來計算:

在CML電路中每一級的等效電容為本級的寄生電容Cself與負載電容Cload之和。據此計算出電路總的延時,從而確定電路的級數N以及比例常數u。圖6所示為第k級與第k+1級的兩級級聯電路。

圖6 兩級級聯的CML電路

由上圖可得第k級電路的延時為

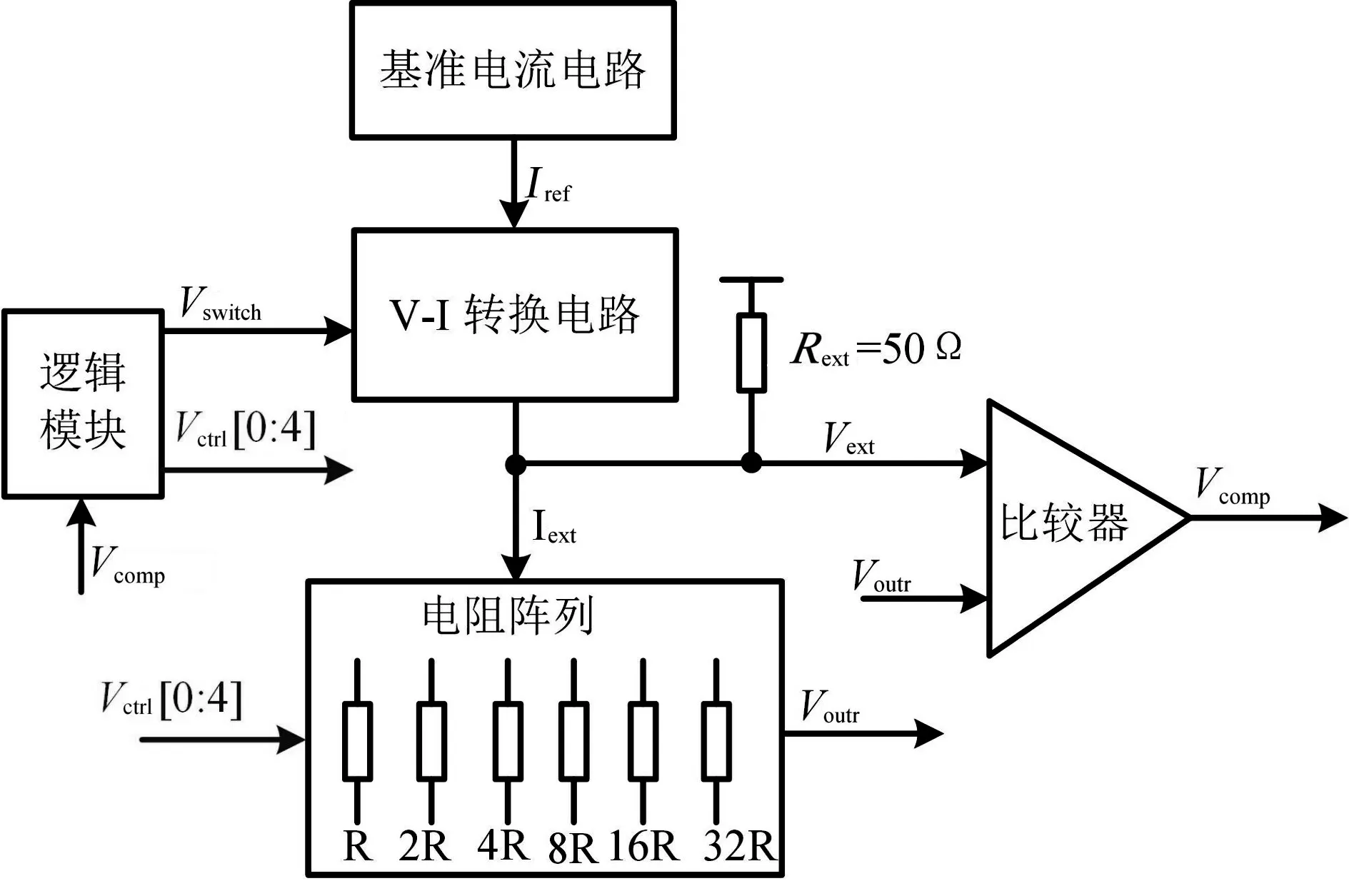

當CDB< 其中: 可以根據電路的具體參數來得到λ,從而求得Nopt和u。本文據此優化后確定電路結構為4級級聯,MOS管尺寸比例為2倍。 在高頻信號傳輸過程中,與傳輸線特征阻抗不匹配會帶來一系列的信號完整性問題,如傳輸線上信號反射、串擾、駐波[14]等,會嚴重影響信號或能量的傳輸質量,進而影響后級電路的性能。為此,本文設計了自適應阻抗匹配電路,以實現精準度較高的電阻。 本文所設計的自適應阻抗匹配電路結構如圖7所示,包含邏輯模塊、基準電流電路[15~16]、V-I轉換電路、電阻陣列及比較器[17]。根據所需電阻值的大小確定電阻陣列中各阻值的設定,并按照一定算法設計控制信號Vctrl[0:4]的變化,進而控制電阻陣列阻值的變化;通過基準電流源與V-I轉換電路產生精準電流Iext,精準電流分別與片外50Ω電阻及片內電阻陣列產生兩個電壓信號Vext與Vreal,兩個電壓通過比較器得到的信號Vcomp又設計為邏輯模塊的控制信號,使得比較出正確的結果后邏輯模塊可保持所需的序列。當Voutr達到所需的電壓值時的電阻陣列的阻值即為符合要求的阻值。 圖7 自適應阻抗匹配電路結構框圖 本文基于SMIC 0.18μm CMOS工藝完成了電路設計及仿真驗證,主要驗證發送器電路的三個主要模塊功能的實現:10∶1并串轉換的實現、CML驅動電路的輸出以及阻抗匹配電路。下面將對整體電路進行仿真驗證與分析。 圖8 整體電路仿真結果 圖8 為整體電路前仿真結果,輸入信號是為10路并行輸入數據D0~D9,位速率為312.5Mbps。輸出是兩組差分信號,第一組是實現10∶1并串轉換后的串行數據OUT1及反相信號OUT2,并串轉換后的數據位速率為3.125Gbps;第二組是并串轉換后的數據通過CML驅動電路后的差分輸出,其保持了串行數據的波形與速率并且CML驅動電路的輸出擺幅為762mV。圖8中以顯示兩組數據為例表明10∶1并串轉換的實現與傳輸。 圖9 自適應阻抗匹配電路仿真結果 圖9 是自適應阻抗匹配電路仿真結果,其中固定電平Vref=1.3V是參考電壓,阻抗匹配電路的輸出信號Voutr從1.205V開始階升,直到Voutr≥Vref時開始保持不變,此時電壓為1.31V,同時所測電流值為9.79mA,則電阻值為R=(VDD-Voutr)/I,R=50.05Ω,偏差僅為0.1%。同時Vref與Voutr是比較器的輸入信號,比較器的輸出是Vcomp。當Vref大于Voutr時Vcomp為高電平,當Vref小于Voutr時,Vcomp跳變為低電平。同時Vcomp是邏輯模塊的控制信號,Vcomp為低電平時邏輯模塊的輸出狀態鎖定,則使得Voutr保持不變。表1為不同工藝角下阻抗匹配電路仿真結果。 表1 不同工藝角下阻抗匹配電路仿真結果 本文基于SMIC 0.18μm CMOS工藝完成了電路版圖設計,圖10所示為整體電路版圖。圖中左邊為添加I/O與PAD之后的整體電路版圖,右邊為整體電路IP核版圖。整體電路IP核版圖中主要包含10∶1并串轉換電路、CML驅動電路、阻抗匹配電路以及電阻陣列四大模塊,其中電阻陣列是由兩組阻抗匹配電路中的電阻陣列模塊組成,由于CML驅動電路的結構需要兩個50Ω電阻,為保證該部分電路的匹配性而添加單獨的電阻陣列。整體電路IP核的版圖長*寬為220.14μm*197.5μm。 圖10 整體電路版圖 本文設計了一種高速接口發送器電路,包含10:1并串轉換、CML驅動電路、阻抗匹配電路,實現了高速數據轉換與傳輸,并實現傳輸終端的阻抗匹匹配。整個電路采用SMIC 0.18μm CMOS工藝,仿真結果表明,電路實現了位速率為312.5Mbps的并行數據到位速率為3.125Gbps的串行數據的轉換,CML驅動電路實現了串行數據的傳輸功能,輸出擺幅為762mV,阻抗匹配電路實現的高精度電阻50.05Ω,偏差僅為0.1%。

2.3 自適應阻抗匹配電路的設計

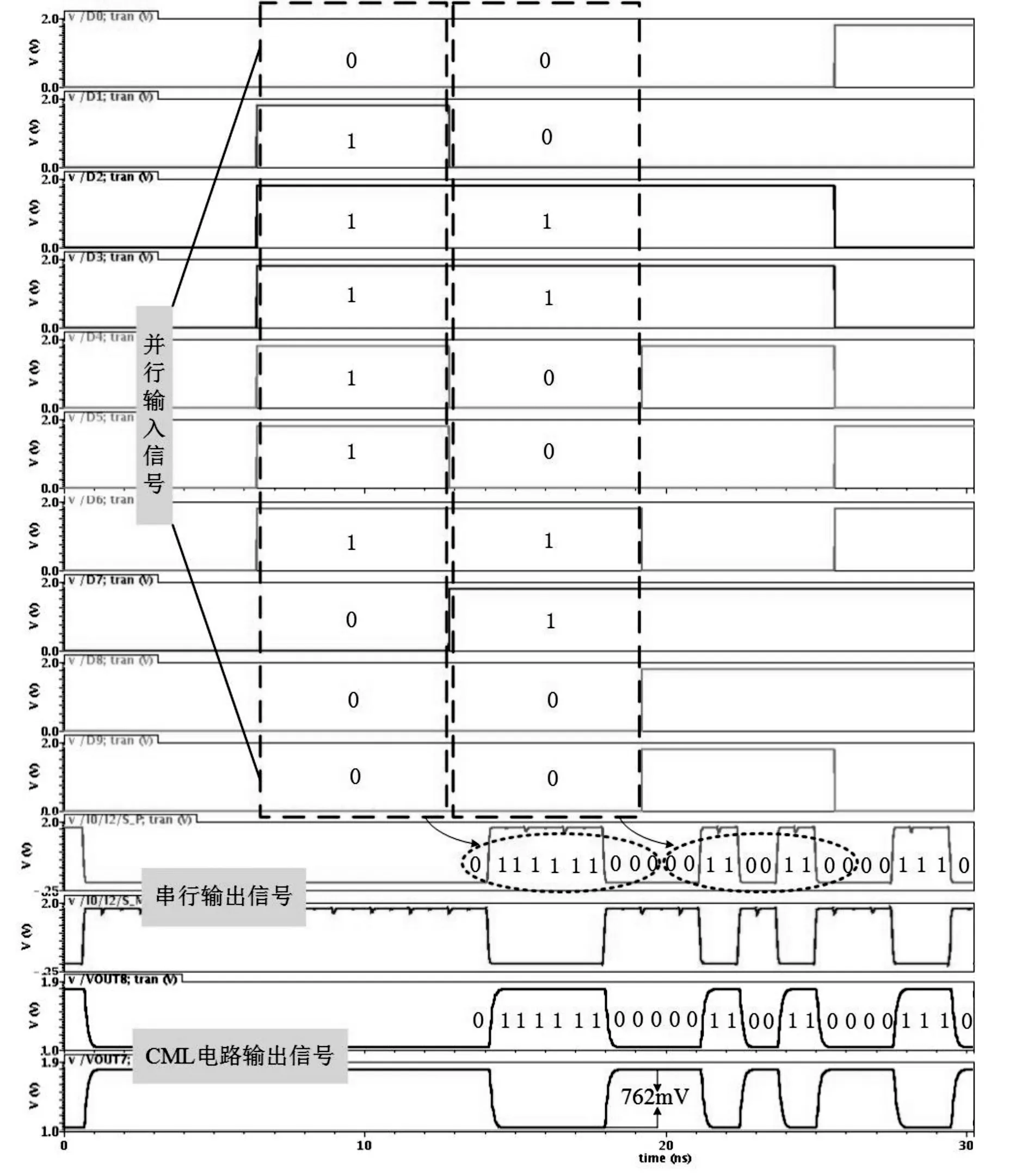

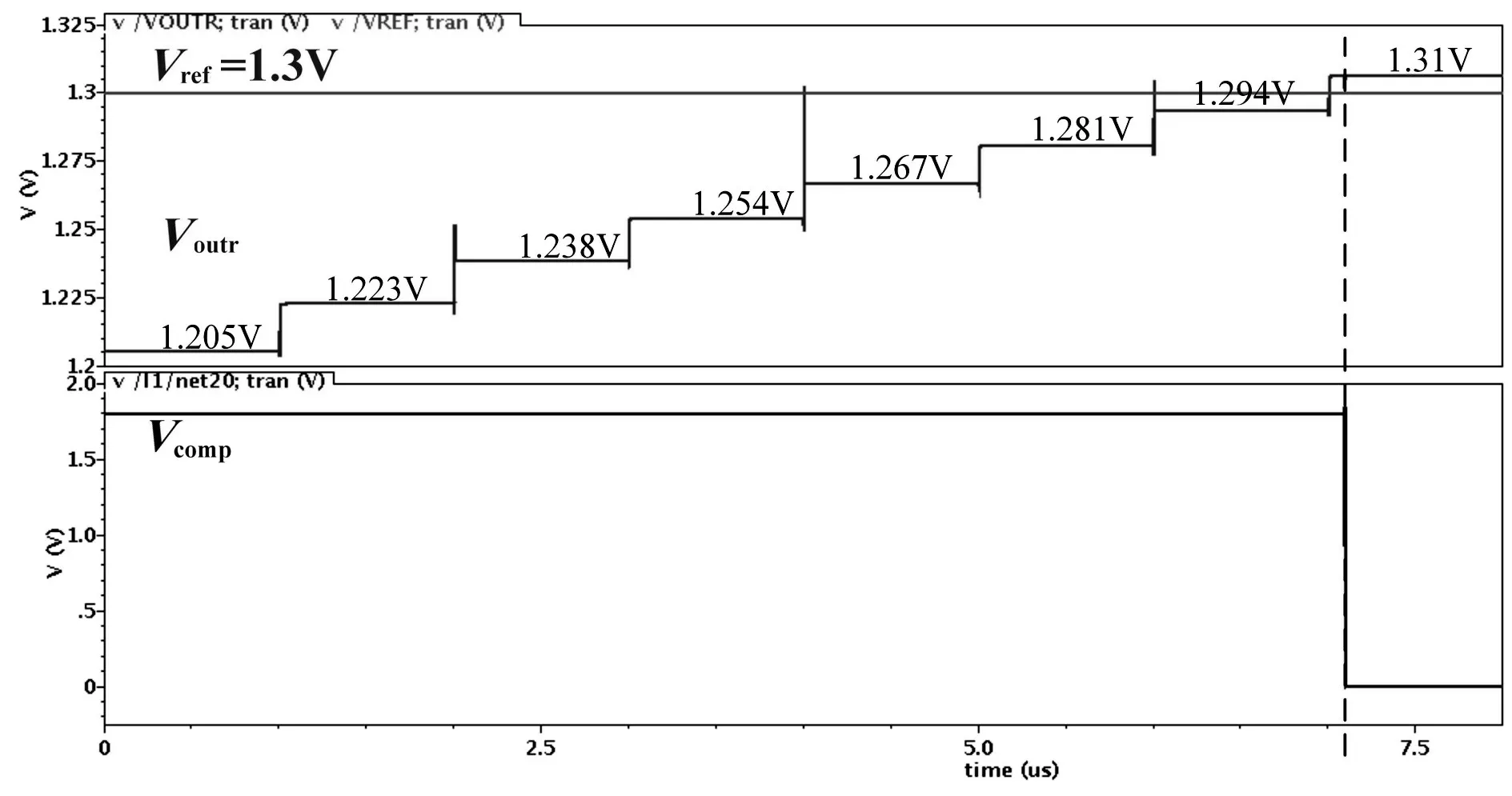

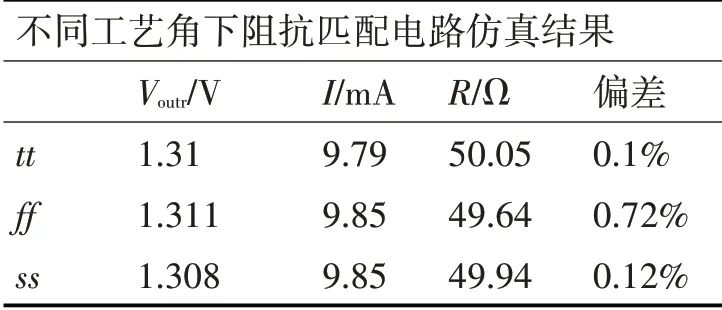

3 仿真結果及分析

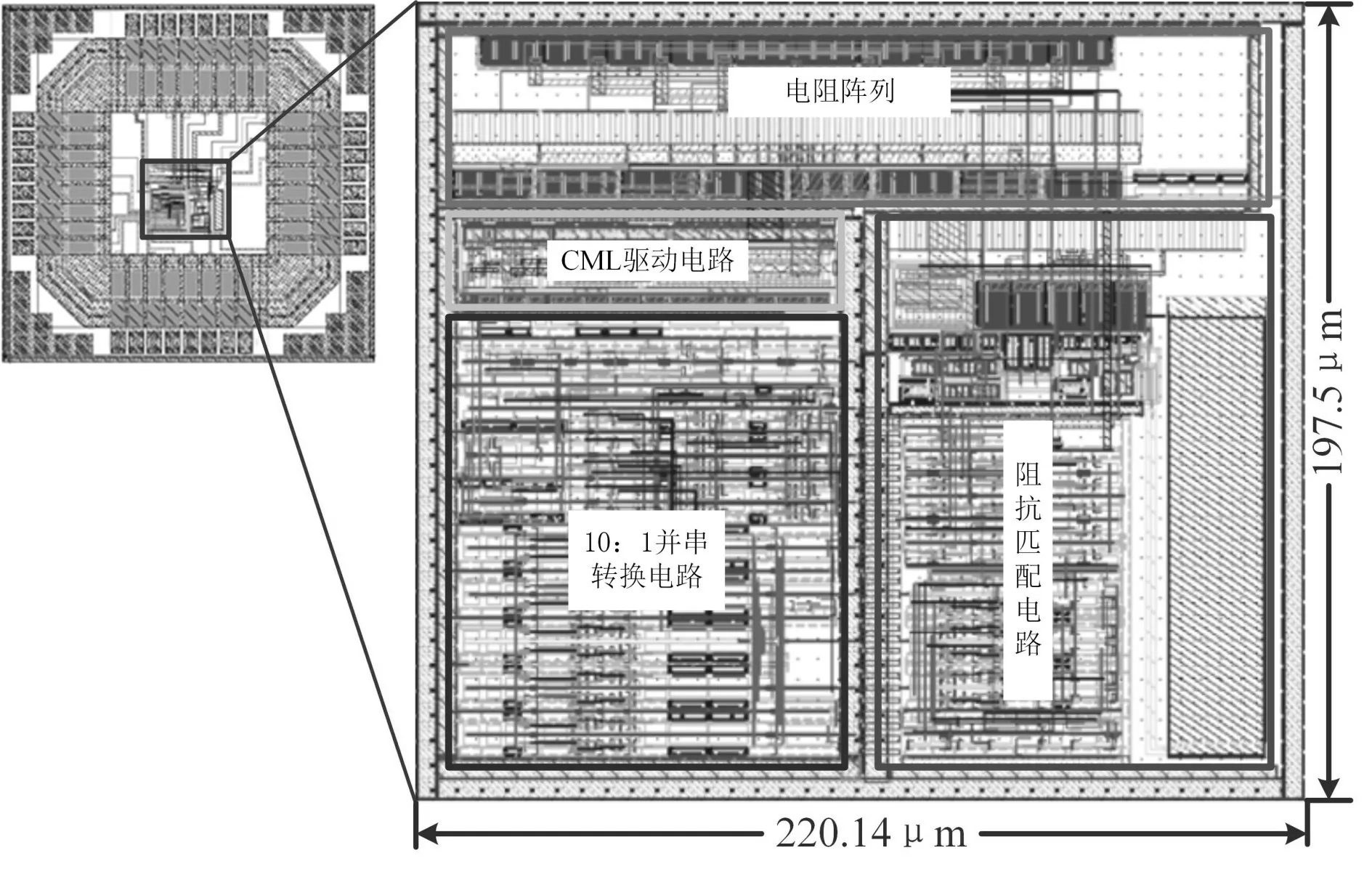

4 版圖設計

5 結語