高壓電解電容波峰焊放電擊穿板上芯片的機理研究及對策

王大波 施清清 李會超 宗巖

摘要:芯片失效作為困擾電子行業(yè)的難題,失效機理復(fù)雜,對于因生產(chǎn)現(xiàn)場環(huán)境造成的過電、靜電失效,環(huán)節(jié)無法鎖定。通過對高壓電解電容帶電插裝對印制電路板上芯片損傷分析,確定主板過波峰焊時錫面連錫短路導(dǎo)致高壓電解電容放電擊穿芯片的失效機理,并制定管控對策,有效降低芯片失效不良。

關(guān)鍵詞:芯片失效;高壓電解電容;擊穿;波峰焊;PcBA

0引言

隨著電子技術(shù)的發(fā)展,小型化、集成化的芯片被應(yīng)用于各個領(lǐng)域,如何保證自身可靠性及產(chǎn)品質(zhì)量成為芯片廠商不斷深入研究的熱點。但芯片因生產(chǎn)環(huán)境、使用環(huán)境苛刻,失效情況時有發(fā)生。目前業(yè)界已經(jīng)識別到的失效原因分兩大類:①芯片本身制造缺陷;②生產(chǎn)現(xiàn)場不規(guī)范操作導(dǎo)致失效。業(yè)內(nèi)常用的失效分析方法包括:芯片開封、X-Ray無損探傷、SEM掃描電鏡、EMMI偵測等。此類分析方法對于芯片制造缺陷,如晶元異常、金線綁定異常等能直觀判斷失效環(huán)節(jié),但是對于因生產(chǎn)現(xiàn)場環(huán)境造成的EOS(過電應(yīng)力)、ESD(靜電放電)卻難以鎖定失效點,給生產(chǎn)、產(chǎn)品質(zhì)量改善帶來不便。

電解電容因容量大,廣泛應(yīng)用于輸出濾波電路中,起儲能和濾波作用。高壓電解電容因其制造工藝及電子特性,在插裝前會殘留部分電壓,而殘留電壓對于電路板上半導(dǎo)體器件的影響一直被行業(yè)內(nèi)電路設(shè)計者所忽略。學(xué)者針對高壓電解電容殘留電壓對芯片失效進行深入研究,并做了充分試驗驗證。結(jié)果表明高壓電解電容未放電即插裝,在過波峰焊時會通過錫面將殘留電壓作用于芯片上,致使芯片失效。同時,學(xué)者通過大量數(shù)據(jù)驗證,通過改進電路布局或過板方向,有效解決了因高壓電解電容未放電導(dǎo)致的芯片失效,降低產(chǎn)品不良率,提高產(chǎn)品可靠性。

1案例分析

1.1背景

控制器車間生產(chǎn)某兩款主板,某廠家開關(guān)電源芯片零星下線,批次不集中,失效外在表現(xiàn)為芯片的1腳(使能腳)與5腳(地腳)之間阻抗值異常,正常品阻抗為M歐級別,失效品阻抗為K歐級別。對正常、異常芯片分別測試U-I曲線,如圖1、圖2所示,表明芯片失效,有漏電流。圖3、圖4為異常芯片X-Ray圖像,結(jié)果表明芯片內(nèi)部結(jié)構(gòu)無明顯異常。經(jīng)廠家對芯片開封確認,如圖5所示,確認芯片失效模式為過電損傷。

1.2分析過程

取庫存開關(guān)電源芯片,對PIN1(EN/UV)腳與PIN5(s)腳施加15V直流電壓,測試阻值,試驗后芯片1~5腳阻抗在10kΩ左右,與下線異常品阻抗一致,測試U-I曲線與下線品一致,存在明顯漏電。經(jīng)對芯片開封確認,芯片屬過電失效。

對生產(chǎn)線及員工的靜電防護、在線測試設(shè)備進行排查,未發(fā)現(xiàn)異常。為鎖定失效環(huán)節(jié),對未上線芯片全檢1~5腳阻抗,無異常后進入下一生產(chǎn)流程。最終鎖定失效環(huán)節(jié)發(fā)生在主板進入波峰焊后與出波峰焊間,進一步檢查波峰焊設(shè)備接地狀態(tài)及防靜電檢查,無異常。初步分析為高溫導(dǎo)致芯片失效。因芯片為SMT貼裝,對比回流焊、波峰焊溫度及過板時間,回流焊環(huán)境更為惡劣,但未出現(xiàn)異常。同步安排芯片高溫、低溫、冷熱沖擊、高溫潮態(tài)試驗均未發(fā)現(xiàn)異常,鎖定失效發(fā)生在波峰焊浸錫環(huán)節(jié)。

對開關(guān)電源芯片電路分析,電路中有450v/22uf的電解電容,初步鎖定過電源為電解電容放電異常。經(jīng)驗證,使用直流電源對主板上電解電容充15V的直流電后對開關(guān)電源芯片1-5腳進行放電,芯片失效,與下線樣品現(xiàn)象一致。查詢該芯片技術(shù)參數(shù),P1N1腳(EN/UV)工作的最大額定電壓為9V,高于9V有過電擊穿隱患。隨機抽取350個未上線使用的電解電容測試殘余電壓,有3個電壓高于10V,理論上高壓電解電容殘余電壓在未放電即插裝使用存在擊穿芯片隱患。

2實驗驗證

2.1驗證條件及結(jié)果

1.同編碼電容及下線主板;

2.殘余電壓:30V;

3.驗證數(shù)量:30PCS;

4.驗證結(jié)果:未復(fù)現(xiàn)。

2.2原因分析

通過對生產(chǎn)過程及波峰焊內(nèi)部構(gòu)造分析,確認未復(fù)現(xiàn)原因有以下3點:

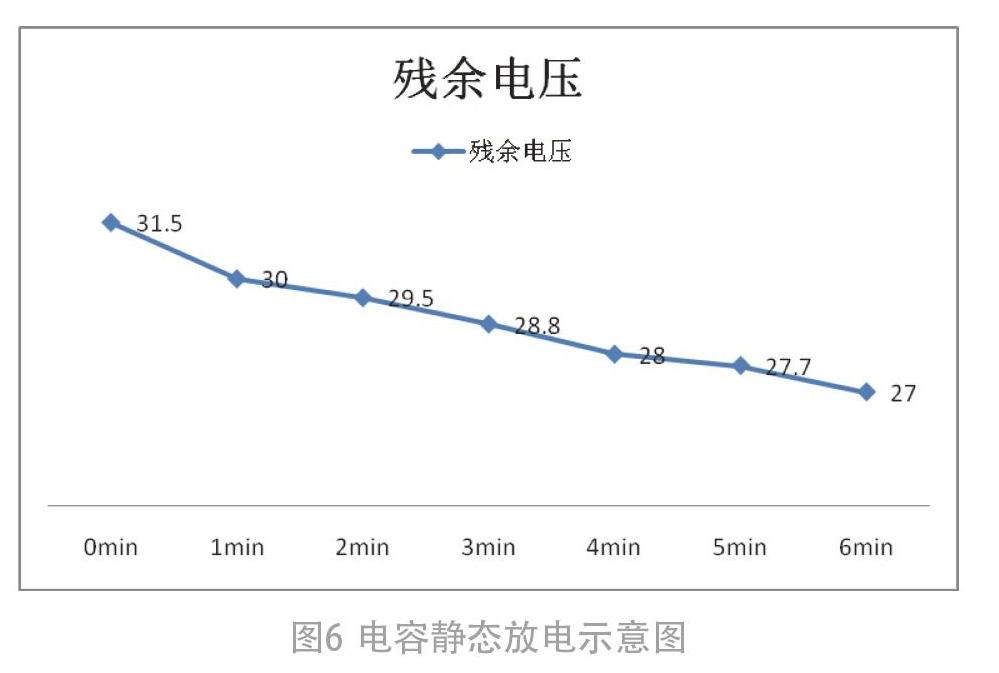

1)電解電容充電后會靜態(tài)放電,下線主板由波峰焊入口到錫爐位置需5min,同步做電容靜態(tài)放電試驗,如圖6所示,表明電容殘余電壓隨時間遞減。

2)電解電容插裝后由插件段至波峰焊錫爐過程中,因鏈爪不平穩(wěn)電容在晃動過程中引腳會碰到焊點過孔沉銅,經(jīng)由印制線路板回路中耗能器件,加速電容放電。經(jīng)驗證,電容充電后,人為晃動電容會加速放電。同步對充電后電容在波峰焊內(nèi)部不同階段殘余電壓測量,浸錫前殘余電壓相差較大,高可至20V,低可至5V以下,表明電容帶電插裝后其放電過程屬隨機過程,存在偶發(fā)性。

3)高壓電解電容放電擊穿芯片發(fā)生在主板浸錫過程中,因該芯片為sMT貼裝,需滿足電容引腳和芯片1腳測試點同時接觸錫面方可實現(xiàn)放電。錫爐的錫面為鋸齒狀斜坡面,波峰高度有差異。同時,若電容雙引腳浸錫則放電給錫面而不會給芯片。

結(jié)合以上三點,高壓電解電容放電擊穿芯片需空間與時間上同時滿足要求,為概率性事件,此為該芯片零星下線原因。

3失效機理分析

3.1失效機理

對主板電路及過板方向進行分析,電容負極與開關(guān)電源芯片5腳共地,芯片1腳與過孔測試點共線路。當(dāng)測試點、電容正極同時處于錫面時,電容的正極與測試點通過錫面連通,即此時電容正極與芯片1腳連通形成回路,相當(dāng)于電容儲存電量直接作用于開關(guān)電源芯片,致使芯片失效,失效機理如圖7所示。

用導(dǎo)線將電容的正極與測試點短接,模擬過錫爐情形,短接導(dǎo)線模擬測試點與電容正極同時浸錫錫面。電容充電后插裝,測試芯片1~5腳阻抗,阻抗異常,與下線現(xiàn)象一致。同步增加電容帶電插裝驗證,故障可復(fù)現(xiàn)。

3.2失效模式確認

此開關(guān)電源芯片共使用在7款PcB上,統(tǒng)計18個月生產(chǎn)數(shù)量及芯片下線數(shù)量如表1所示。

從上表可以得出,迄今此開關(guān)電源芯片所用的板,只有c、D兩款主板有下線,針對此主板上的開關(guān)電源芯片、電容、測試點、過板方向等布局展開研究。

B主板從過板方向看,電容先于芯片1腳測試點浸錫,電容過錫爐時電容正負極先接觸錫面,測試點還未接觸錫面前電容已放電,因此沒有電容放電給芯片的條件。

F、G兩款主板芯片1腳的測試點先接觸錫面,而后電容正負極引腳同時浸錫,三者有共同處于錫面的時間,但當(dāng)電容的正負極同時浸錫時,電容即放電,不會再通過測試點回路放電給芯片。

A、E兩款主板從過板方向看,芯片1腳測試點先過錫爐,存在電容、測試點同時處于錫面的條件,但是此主板的電容是負極先接觸錫面,即存在電容負極、測試點同時處于錫面的情況。此時電容負極通過錫面與測試點連通,測試點與芯片1腳連通,即電容負極與芯片1腳連通,而電容的負極與芯片的5腳是連通的,此時相當(dāng)于電容的負極同時與芯片的1腳和5腳連通,而此時電容的正極在錫面以外,顯然無放電回路,如圖8所示。當(dāng)電容的正極進入錫面以后,電容的正極與負極通過錫面連通,電容的電會直接通過錫爐釋放。

排查c、D兩款主板歷史在線失效數(shù)據(jù)時,了解到此兩款主板的最初生產(chǎn)的階段此開關(guān)電源芯片無在線失效案例,進一步調(diào)查發(fā)現(xiàn),此兩款主板進行過三次版本升級,更改后開始出現(xiàn)芯片在線失效,對比幾次更改情況,第一次更改調(diào)整了電容、芯片、測試點的布局,改變了波峰焊階段電容放電回路,滿足電容對芯片放電的條件,此點更改后一直延續(xù)到后面的版本,因此第一次更改后的版本都出現(xiàn)過此芯片的零星下線。

為驗證以上分析的準(zhǔn)確性,將c、D兩款主板改變過板方向,從而破壞了電容放電給芯片的放電回路,累計驗證數(shù)據(jù)超過3w,開關(guān)電源芯片無一在線失效案例,進一步佐證了分析的準(zhǔn)確性。

4結(jié)論與對策

4.1研究結(jié)論

芯片生產(chǎn)線失效的原因為同主板的高壓電解電容存在放電不徹底的情況,當(dāng)主板經(jīng)過錫面時,電容的正極與芯片1腳的測試點同時處在錫面,而測試點是與芯片1腳連通的,同時電容的負極與芯片的5腳連通,即相當(dāng)于電容的正負極分別加在芯片的1腳和5腳,從而將參與電壓釋放在上,導(dǎo)致芯片過電失效,原理如圖7所示。

對于DIP封裝的芯片,無需依靠測試點,芯片的引腳直接與錫面接觸,此種情況下,需考慮芯片上高壓電解電容在主板上的空間布局,同時要考慮錫面的寬度。芯片過電損傷后,其在廠內(nèi)并不以某種失效形式表現(xiàn),但長期運行影響芯片及成品可靠性。

4.2解決對策

為減少因高壓電解電容未放電插裝導(dǎo)致的芯片失效,可選擇以下方案進行解決:

1)PcBA的空間布局滿足電解電容兩正負引腳的連線垂直波峰焊過板方向,既確保電容的正負引腳同時進入錫面,將可能存儲的電放給錫面。

2)貼片封裝的芯片考慮將其測試點布控在遠離高壓電解電容的位置,具體是平行過板方向的距離大于波峰焊錫爐錫面的距離,DIP封裝芯片考慮芯片本身遠離高壓電解電容的位置,具體是平行過板方向的距離大于波峰焊錫爐錫面的距離,同時確保與芯片引腳連通的電容引腳先到達錫面。