偽隨機測試激勵信號設計

孫永建 秦鵬 唐景華

摘要:模數混合電路的內建自測試(BIST)研究是近些年比較有挑戰的,其中如何以較小的硬件開銷獲得模擬激勵信號以及數據響應分析比較關鍵。本文將以偽隨機信號作為研究對象,對BIST結構的激勵模塊進行設計偽隨機信號,并在QuartusⅡ里進行仿真驗證,為后續混合信號BIST結構設計打下基礎。

關鍵詞:BIST;測試激勵;LFSR

中圖分類號:TN407文獻標識碼:A文章編號:1672-9129(2020)07-0076-02

Abstract: The study of modular hybrid circuit built-in self-testing (BIST) is challenging in recent years, among which how to obtain analog excitation signal and data response analysis with less hardware cost is key. This article will take the pseudo random signal as the research object, the incentive of BIST structure module design pseudo random signal, and Quartus Ⅱ simulation verification, lay the foundation for subsequent mixed-signal BIST structure design.

Key words: BIST; Test incentives; LFSR

1引言

內建自測試(BIST)是由測試電路自身生成測試激勵信號,作用于電路本身并根據響應來進行測試的方法[1],是一種很重要的測試方法。若測試結構中的測試激勵為零均值的高斯隨機信號時,不僅能簡化求取各階累積量譜的計算[2],而且高斯隨機信號在性質上接近白噪聲,其帶寬和幅度都可以控制,可以保證對被測電路的持續激勵,所以采用高斯隨機信號作為某混合信號BIST結構中的激勵信號。但是設計服從高斯分布的隨機信號比較復雜而且在設計中是無法得到完全服從高斯分布的激勵信號。

2激勵模塊設計

2.1 激勵結構。偽隨機信號在現實應用中通常采用線性移位寄存器序列(M序列)來產生,具有十分接近白噪聲的性質,因此又稱偽隨機信號為偽高斯信號。激勵生成的結構如圖1所示,包含控制信號、線性反饋移位寄存器(LFSR)[3]和DAC三部分組成。當BIST控制器使能有效時,激勵內部的控制器則產生LFSR使能信號,使得LFSR開始移位輸出,并同時給DAC控制時鐘信號,DAC輸出的模擬信號就是偽隨機信號。

2.2 ?LFSR設計。如果n元布爾函數 f(x1,x2,…,xn)可以表示成n個變元x1,x2,x3,…,xn的線性奇次函數:f(x1,x2,…,xn)=cnxn+cn-1xn-1+…c1x1f(x1,x2,…,xn)=cnxn+cn-1xn-1+…c1x1其中ci=0或1,則以f(x1,x2,…,xn)為反饋函數的移位寄存器就叫做線性反饋移位寄存器(LFSR)[4]。圖2為n級線性反饋移位寄存器的一般結構形式。

其中A1,A2,…,An是寄存器串聯成的移位寄存器;hi是反饋控制,hi∈0,1。為0不存在,為1則存在反饋控制,線性反饋移位寄存器的特征多項式為:

h(x)=xn+h1xn-1+h2xn-2+…+hn-1x+1(1)

產生線性反饋移位寄存器序列的n級移位寄存器,其特征多項式必須是n次本原多項式,也就是說特征多項式與輸出序列的周期有密切的關系。要設計LFSR,并使之輸出序列具有最大的周期性,必須要找到本原多項式[5]。

以12Bit的TI芯片DAC902芯片(轉換速度最高達到165M)為例,最少需要12bit位移位寄存器。選取LFSR本原多項式為: x12+x6+x4+x+1,設計線性反饋移位寄存器取其并行輸出作為DAC的編碼,在QuartusII環境下用Verilog HDL硬件描述語言設計,輸出的序列仿真如圖3所示。

該序列發生器的輸出信號是一個數字隨機信號,在設計中,通過D/A轉換器得到模擬信號。若被測電路是數字輸入,不需要再加D/A轉換器,可根據實際需要直接將數字信號接到被測電路。

2.3 控制設計仿真

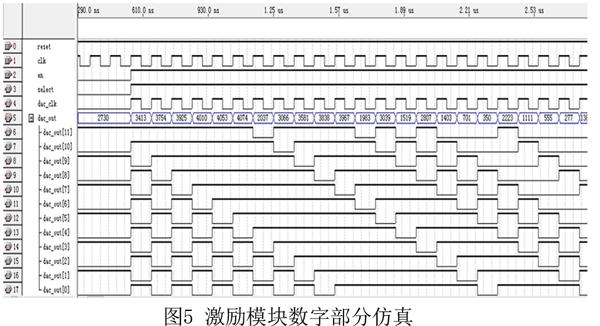

由圖1可知,激勵模塊不僅要設計LFSR產生隨機序列,還要產生控制時鐘來控制DAC工作,DAC902控制時序圖如圖4所示。

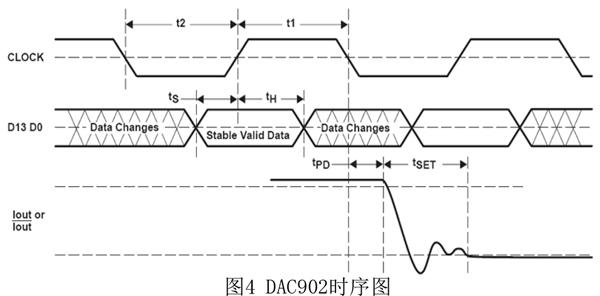

DAC控制起來比較容易,使能LFSR后,產生M序列并行輸出到DAC數據端,然后控制器輸出DAC控制時鐘,上升沿時數據有效,DAC轉換輸出信號。用硬件描述語言對激勵模塊數字部分進行設計,功能仿真如圖5所示。

從圖5中可以看出,在復位信號無效(即高電平)時,在系統時鐘的驅動下,模塊的輸入使能置位有效時,LFSR并行有數據輸出到DAC,并同時輸出DAC控制時鐘,來驅動DAC工作。

3結論

本文對BIST結構的測試激勵進行設計,通過仿真結果可知,能夠實現ADC的控制信號和數據,產生偽隨機測試激勵信號,為后續混合信號BIST測試結構設計打下基礎。

參考文獻:

[1]陳佳楠,馬永濤,李松等. 多目標優化的多存儲器內建自測試[J].電子測量與儀器學報.2020,01(34):193-198.

[2]孫永建,加等.混合BIST對象建模及結構分析[J].國外電子測量技術2010.05(29):21-23.

[3]劉偉,雷加.基于偽隨機測試的模數混合信號內建自測試法[J].計算機工程與應用.2008,44(33).

[4]肖國鎮,梁傳甲,王育民.偽隨機序列及其應用[M].國防工業出版社.1985.3

[5]王榮陽,劉福浩,李向陽 紫外光通信誤碼率測試系統設計[J].半導體光電.2012.05:707-710

[6]楊舟,王紅,楊士元.混合信號SOC聯合測試方案[J].清華大學學報(自然科學版),2011.5(S1):1381-1387

[7]安寶森等.BIST電路在嵌入式非易失性存儲器可靠性測試中的應用[J].電子設計工程.2019,06(11):33-36

[8]談恩民,賈亞平.用于數模混合電路中ADC測試的IP核設計[J].北京: 微電子學, 2016.12(6):849-851

作者簡介:孫永建(1986—),男,研究方向:混合信號電路測試研究、嵌入式系統開發。