基于FPGA 的手勢(shì)信號(hào)實(shí)時(shí)采集綜合性實(shí)驗(yàn)項(xiàng)目研究

鄭雪峰,馬學(xué)條,湯 峻,陳 龍,楊 柳

(杭州電子科技大學(xué) 電子信息技術(shù)國家級(jí)虛擬仿真實(shí)驗(yàn)教學(xué)中心,浙江 杭州 310018)

借助信息技術(shù)能有效解決實(shí)驗(yàn)教學(xué)過程中時(shí)間、地域和安全等限制問題,對(duì)于探索實(shí)驗(yàn)教學(xué)新模式具有重要意義[1]。我校數(shù)字電路教師團(tuán)隊(duì)為了實(shí)施全方位開放式教學(xué),圍繞拓展實(shí)驗(yàn)內(nèi)涵、激發(fā)學(xué)生學(xué)習(xí)興趣、培養(yǎng)學(xué)生工程創(chuàng)新意識(shí)等,開發(fā)了“基于FPGA 的手勢(shì)信號(hào)實(shí)時(shí)采集綜合性實(shí)驗(yàn)項(xiàng)目”,借助遠(yuǎn)程虛擬仿真實(shí)驗(yàn)教學(xué)手段,實(shí)現(xiàn)了全方位開放式教學(xué),有效地拓寬了數(shù)字電路實(shí)驗(yàn)教學(xué)的時(shí)空領(lǐng)域。

1 實(shí)驗(yàn)教學(xué)模式

數(shù)字電路實(shí)驗(yàn)教學(xué)一般是利用實(shí)驗(yàn)室數(shù)字電路實(shí)驗(yàn)箱,學(xué)生在實(shí)驗(yàn)室里完成實(shí)驗(yàn)設(shè)計(jì),然后提交實(shí)驗(yàn)總結(jié)報(bào)告。這種教學(xué)方式缺乏靈活性,不能激發(fā)學(xué)生的學(xué)習(xí)興趣和實(shí)驗(yàn)熱情[2]。

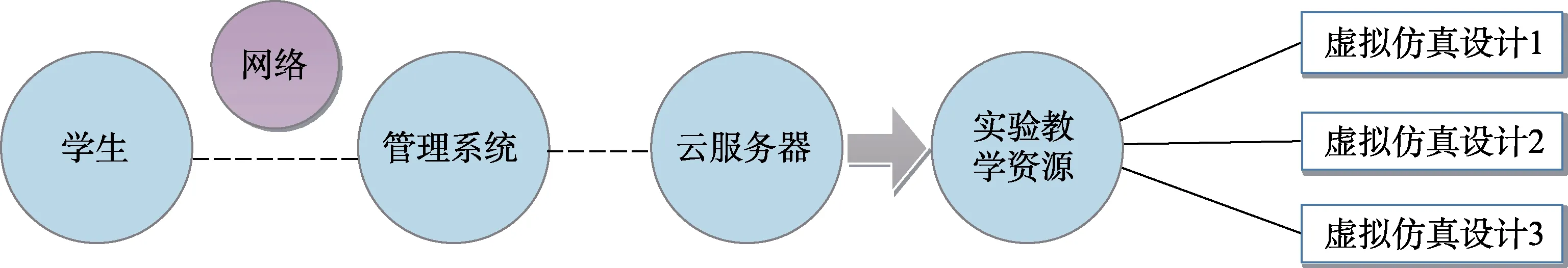

經(jīng)過多年實(shí)驗(yàn)教學(xué)改革與實(shí)驗(yàn)平臺(tái)建設(shè),形成了“遠(yuǎn)程虛擬實(shí)驗(yàn)”教學(xué)模式,如圖1所示。學(xué)生只需連接網(wǎng)絡(luò),通過開放式實(shí)驗(yàn)教學(xué)管理系統(tǒng),即可在寢室、實(shí)驗(yàn)室或教室等區(qū)域遠(yuǎn)程共享實(shí)驗(yàn)教學(xué)資源,突破時(shí)間、空間限制,進(jìn)行數(shù)字電路虛擬仿真實(shí)驗(yàn)操作,遠(yuǎn)程提交仿真結(jié)果,實(shí)現(xiàn)“處處能學(xué)、時(shí)時(shí)可學(xué)”的泛在化學(xué)習(xí)[3]。

圖1 遠(yuǎn)程虛擬仿真實(shí)驗(yàn)教學(xué)流程圖

2 綜合創(chuàng)新性實(shí)驗(yàn)項(xiàng)目開發(fā)

“基于FPGA 的手勢(shì)信號(hào)實(shí)時(shí)采集綜合性實(shí)驗(yàn)項(xiàng)目”,旨在使學(xué)生綜合運(yùn)用電子設(shè)計(jì)自動(dòng)化(EDA)技術(shù),通過自主設(shè)計(jì)、虛擬仿真等環(huán)節(jié),完成實(shí)驗(yàn)設(shè)計(jì)。使學(xué)生將理論和實(shí)驗(yàn)知識(shí)融會(huì)貫通,提高設(shè)計(jì)復(fù)雜數(shù)字系統(tǒng)的能力及實(shí)踐創(chuàng)新能力[4]。

如圖2 所示,實(shí)驗(yàn)系統(tǒng)由數(shù)據(jù)采集模塊、異步FIFO 模塊、SDRAM 模塊和VGA 顯示模塊等組成。通過I2C 配置好OV5640,將采集到的8 位特定分辨率信號(hào)轉(zhuǎn)化為RGB565 格式;將轉(zhuǎn)換好的16 位的像素信號(hào)通過FIFO1 緩存,同時(shí)存入SDRAM;存入每幀像素后,將SDRAM 輸出給FIFO2;再將FIFO2 輸出的每幀數(shù)據(jù)通過VGA 模塊進(jìn)行顯示。

圖2 “基于FPGA 的手勢(shì)信號(hào)實(shí)時(shí)采集綜合性實(shí)驗(yàn)”系統(tǒng)框圖

2.1 數(shù)據(jù)采集電路設(shè)計(jì)與仿真

數(shù)據(jù)采集模塊采用OV5640 攝像頭進(jìn)行圖像采集,外接18 根引腳。SCLK、SDAT 為I2C配置引腳;DB0~DB7為采集像素?cái)?shù)據(jù);CMOS_HREF、CMOS_VSYNC 為攝像頭行同步信號(hào)和幀同步信號(hào);PCLK 為I2C 配置好的像素時(shí)鐘;XCLK 為輸入時(shí)鐘;3.3 V 供電引腳和接地引腳;復(fù)位引腳,低電平有效;PWDN 為上電控制引腳,高電平有效。采集的過程為先通過攝像頭的上電時(shí)序之后,F(xiàn)PGA 通過I2C 配置其寄存器,設(shè)置輸出格式為RGB565,輸出分辨率為1024×720。由于攝像頭采集的是8 位像素?cái)?shù)據(jù),而RGB565 格式為16位信號(hào),所以需要將兩個(gè)8 位信號(hào)合成16 位信號(hào)。一個(gè)PCLK 上升沿,采集一個(gè)8 位信號(hào),輸出一個(gè)16位RGB565 信號(hào),則需要兩個(gè)PCLK。當(dāng)幀同步信號(hào)VSYNC 從低電平到高電平跳變時(shí),標(biāo)志一幀采集的結(jié)束,當(dāng)滿足VSYNC 為低電平并且HREF 為高電平時(shí),才是有效像素。由數(shù)據(jù)手冊(cè)可知,OV5640 采集的前10 幀是無效幀,因此有效幀應(yīng)該從第12 幀開始算起。寄存器配置及采集位拼接電路如圖3 所示。

FPGA 通過I2C 協(xié)議向攝像頭發(fā)送配置攝像頭所需的寄存器值,以下是常用的配置寄存器值。

分辨率設(shè)置:

Reg_Data<=24'h380804;

Reg_Data<=24'h380900;

Reg_Data<=24'h380a02;

Reg_Data<=24'h380bd0;

亮度調(diào)節(jié):

Reg_Data<=24'h558740;

Reg_Data<=24'h558801;

鏡像調(diào)節(jié):

Reg_Data<=24'h382107;

Reg_Data<=24'h382100;

翻轉(zhuǎn)調(diào)節(jié):

Reg_Data<=24'h382047;

Reg_Data<=24'h382047;

2.2 FIFO 模塊設(shè)計(jì)與仿真

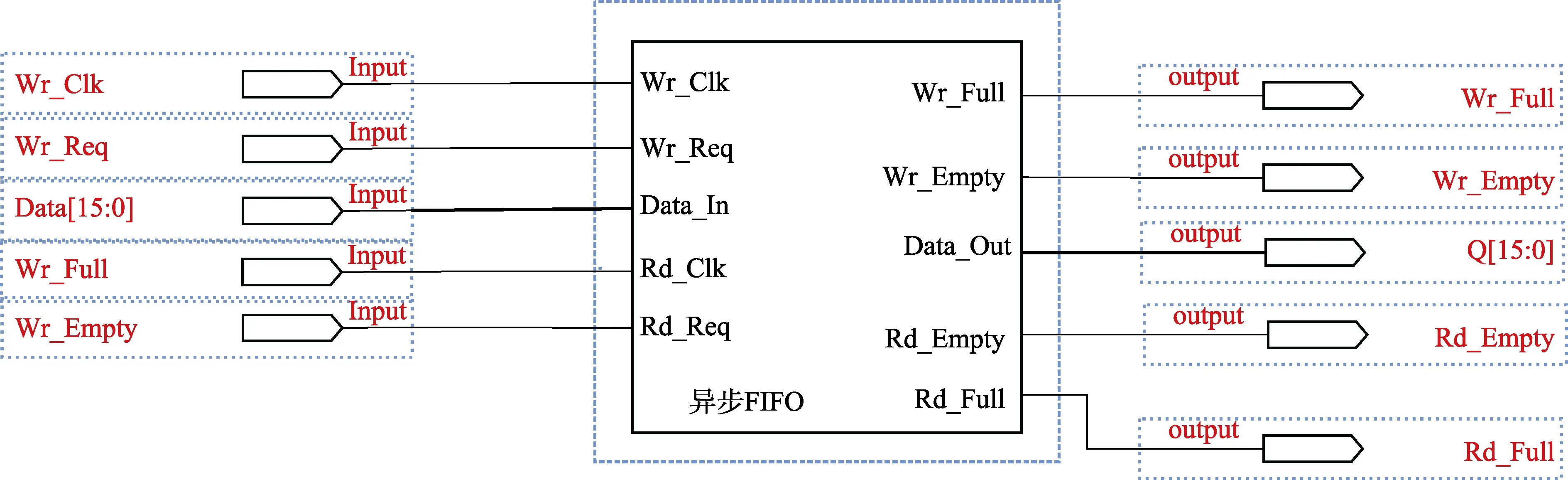

實(shí)驗(yàn)設(shè)計(jì)中需采用兩個(gè)異步 FIFO,記為異步FIFO1 和異步FIFO2。異步FIFO1 主要負(fù)責(zé)緩沖來自攝像頭采集的像素,然后交給SDRAM 緩存;異步FIFO2 主要負(fù)責(zé)接收來自SDRAM 的像素信號(hào),然后投到VGA 上顯示。攝像頭采集的視頻數(shù)據(jù)時(shí)鐘頻率為24 MHz,SDRAM 的驅(qū)動(dòng)時(shí)鐘頻率為100 MHz,因此需要異步FIFO1 作為中間緩沖。VGA 顯示的時(shí)鐘頻率為65 MHz,與SDRAM 的驅(qū)動(dòng)時(shí)鐘頻率也不同,因此需要通過異步FIFO2 進(jìn)行緩沖。如圖4 所示,當(dāng)兩個(gè)獨(dú)立的系統(tǒng)主頻不一樣時(shí),需要通過異步FIFO作為緩沖,使得數(shù)據(jù)可以從一端傳送到另一端[5]。

圖3 寄存器配置及采集位拼接電路框圖

圖4 異步FIFO 框圖

設(shè)置異步FIFO 模塊的數(shù)據(jù)為16 位,深度為512 個(gè)單元。對(duì)FIFO 模塊進(jìn)行仿真,時(shí)序仿真結(jié)果如圖5 所示。其中,Wr_Req 為寫信號(hào),Wr_Clk 為寫時(shí)鐘,Wr_Data為寫數(shù)據(jù),Wr_Full 為寫滿標(biāo)志,Wr_Empty 為寫空標(biāo)志,Rd_Req 為讀信號(hào),Rd_Clk 為讀時(shí)鐘,Rd_Data 為讀數(shù)據(jù),Rd_Full 為讀滿標(biāo)志,Rd_Empty 為讀空標(biāo)志。

圖5 FIFO 模塊仿真圖

由異步FIFO 仿真圖可知,在輸入端24 MHz 頻率Wr_Clk 下寫入256 個(gè)數(shù)據(jù),寫請(qǐng)求信號(hào)Wr_Req 在寫入過程中一直呈現(xiàn)有效電平狀態(tài),寫滿后Wr_Full 信號(hào)拉高,寫請(qǐng)求信號(hào)Wr_Req 拉低。在n 個(gè)時(shí)鐘后,Rd_Full 讀滿信號(hào)拉高,于是在輸出端100 MHz 頻率的Rd_Clk 下,開始往外讀出數(shù)據(jù),在讀數(shù)據(jù)過程讀請(qǐng)求信號(hào)Rd_Req 一直呈現(xiàn)有效電平狀態(tài),在順利讀出256 個(gè)數(shù)據(jù)后,讀空信號(hào)Rd_Empty 拉高,讀請(qǐng)求信號(hào)拉低,n 個(gè)時(shí)鐘后,寫空信號(hào)Wr_Empty 開始拉高,準(zhǔn)備繼續(xù)寫入數(shù)據(jù)。之后,這一過程不斷循環(huán)執(zhí)行[6]。

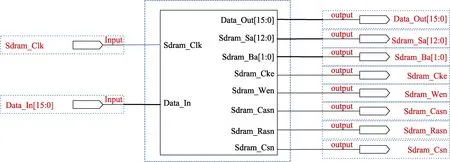

2.3 SDRAM 模塊設(shè)計(jì)與仿真

SDRAM 采用型號(hào)為HY57V2562GTR 的芯片,256 M 容量,16 根數(shù)據(jù)線,13 根地址線,2 個(gè)區(qū)選線,5 根命令控制線。實(shí)驗(yàn)設(shè)計(jì)中,SDRAM 模塊共分初始化、刷新、寫操作、讀操作等四個(gè)步驟。

在對(duì)SDRAM 進(jìn)行寫入讀出的過程中,常規(guī)操作是對(duì)Bank1 中寫入一幀數(shù)據(jù),然后由異步FIFO2 讀出并顯示,接著繼續(xù)寫入下一幀。這種操作使得在寫入SDRAM 過程中,異步FIFO2 無法讀取,只能等待一幀寫完才能讀取。如果實(shí)驗(yàn)過程采用乒乓操作法原理,則在對(duì)Bank1 寫入第一幀數(shù)據(jù)后,異步FIFO2 開始讀出Bank1 中的一幀數(shù)據(jù),同時(shí)異步FIFO1 向SDRAM中的Bank2 中寫入下一幀數(shù)據(jù)。如此交替往復(fù)的讀寫過程,省去了大量等待時(shí)間,加快了視頻傳輸效率[7]。

SDRAM 模塊電路框圖如圖6 所示。其中:

Sdram_Clk(輸入時(shí)鐘頻率):100 MHz。

Data_In(寫數(shù)據(jù)):來自異步FIFO1 寫入的16位RGB565 數(shù)據(jù)。

Data_Out(讀數(shù)據(jù)):由異步FIFO2 讀出至顯示的16 位RGB565 數(shù)據(jù)。

Sdram_Sa(地址信號(hào)):讀寫地址,行列共用,A0—A12 為行地址,CA0—CA8 為列地址。

Sdram_Ba(區(qū)選信號(hào)):該塊SDRAM 共有4 個(gè)Bank 區(qū),每個(gè)Bank 可以存儲(chǔ)64 Mbits。

Sdram_Cke(命令信號(hào)):片選信號(hào),拉低有效。

Sdram_Wen(命令信號(hào)):片選信號(hào),拉低有效。

Sdram_Casn(命令信號(hào)):片選信號(hào),拉低有效。

Sdram_Rasn(命令信號(hào)):片選信號(hào),拉低有效。

Sdram_Csn(命令信號(hào)):片選信號(hào),拉低有效。

圖6 SDRAM 模塊電路框圖

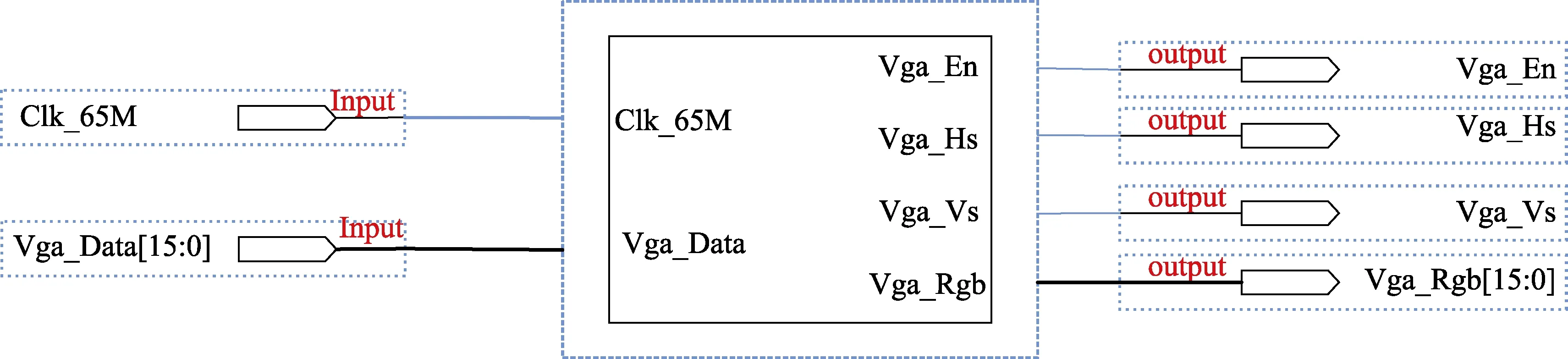

2.4 VGA 顯示電路設(shè)計(jì)與仿真

VGA 顯示模塊電路框圖如圖7 所示。實(shí)驗(yàn)設(shè)計(jì)中,VGA 顯示分辨率為1024*768,控制時(shí)鐘為65 MHz。該電路設(shè)計(jì)中,需要描述VGA 的顯示時(shí)序,包括行、幀同步信號(hào),行消隱、幀消隱像素以及相關(guān)時(shí)序參數(shù)。有效像素的顯示,行同步信號(hào)處于高電平;有效信號(hào)的顯示,幀同步信號(hào)處于高電平。其中:

Clk_65M(輸入時(shí)鐘):VGA 顯示時(shí)鐘。

Vga_Data(輸入數(shù)據(jù)):來自異步FIFO2 的16 位RGB565 數(shù)據(jù)。

Vga_En(使能信號(hào)):行幀同步的共同使能信號(hào)。

Vga_Hs(行同步信號(hào)):選擇出VGA 上有效行信號(hào)區(qū)間。

Vga_Vs(幀同步信號(hào)):選擇出VGA 上有效幀信號(hào)區(qū)間。

Vga_Rgb(輸出數(shù)據(jù)):顯示到VGA 顯示器上的數(shù)據(jù)

VGA 行幀同步信號(hào)仿真結(jié)果,如圖8 所示。其中:

H_Front 24 個(gè)像素時(shí)鐘 V_Front 3 個(gè)行時(shí)鐘

H_Sync 136 個(gè)像素時(shí)鐘 V_Sync 6 個(gè)行時(shí)鐘

H_Back 160 個(gè)像素時(shí)鐘 V_Back 29 個(gè)行時(shí)鐘

H_Disp 1024 個(gè)像素時(shí)鐘 V_Disp 768 個(gè)行時(shí)鐘

H_Total 1344 個(gè)像素時(shí)鐘 V_Total 806 個(gè)行時(shí)鐘

2.5 實(shí)驗(yàn)結(jié)果

根據(jù)系統(tǒng)方案設(shè)計(jì)要求,在原理圖編輯文件中調(diào)用已生成的數(shù)據(jù)采集模塊元件、異步FIFO 模塊元件、SDRAM 模塊元件和VGA 顯示模塊元件,構(gòu)成圖像采集顯示系統(tǒng)頂層電路。選用FPGA 開發(fā)板進(jìn)行硬件測試,硬件測試系統(tǒng)包括OV5640 攝像頭、VGA 顯示器、數(shù)字示波器和數(shù)字可調(diào)電源等[8]。針對(duì)同一手勢(shì)信號(hào),1024×768分辨率原圖、800×600 分辨率原圖、1024×768 分辨率鏡像、1024×768 分辨率翻轉(zhuǎn)、1024×768 分辨率亮度調(diào)節(jié)、1024×768 分辨率環(huán)境光調(diào)節(jié)等結(jié)果,如圖9 所示。

圖7 VGA 顯示模塊電路框圖

圖8 VGA 行幀同步信號(hào)仿真示意圖

圖9 “基于FPGA 的手勢(shì)信號(hào)實(shí)時(shí)采集綜合性實(shí)驗(yàn)”測試結(jié)果

2.6 硬件測試

完成遠(yuǎn)程實(shí)驗(yàn)仿真操作后,學(xué)生可利用實(shí)驗(yàn)室配備的FPGA 測試系統(tǒng)開展虛實(shí)融合測試,實(shí)現(xiàn)仿真指導(dǎo)實(shí)體實(shí)驗(yàn)、實(shí)體實(shí)驗(yàn)驗(yàn)證仿真的閉環(huán)流程。FPGA測試系統(tǒng)包括上位機(jī)、開發(fā)板、下載器、OV5640 攝像頭、VGA 顯示器等,在頂層文件設(shè)計(jì)的電路中定義輸入輸出引腳并進(jìn)行鎖定,編譯后下載.sof 文件,在VGA 上顯示各種處理后的圖像。硬件測試系統(tǒng)如圖10 所示。

圖10 硬件測試系統(tǒng)

3 實(shí)驗(yàn)教學(xué)實(shí)施效果

數(shù)字電路實(shí)驗(yàn)課程面向我校電子信息、通信、自動(dòng)化等12 個(gè)電子類專業(yè)的學(xué)生,每年直接授課學(xué)生1800 多人。團(tuán)隊(duì)教師對(duì)傳統(tǒng)數(shù)字電路實(shí)驗(yàn)教學(xué)在教學(xué)內(nèi)容、教學(xué)方法、課程組織及時(shí)間安排上存在的問題進(jìn)行了研究和改革,以電子設(shè)計(jì)自動(dòng)化(EDA)技術(shù)的學(xué)習(xí)為手段,注重工程能力、分析能力和實(shí)踐能力的培養(yǎng),構(gòu)建了一個(gè)從基本實(shí)踐技能向創(chuàng)新能力逐級(jí)遞進(jìn)的實(shí)踐階梯。“基于FPGA 的手勢(shì)信號(hào)實(shí)時(shí)采集綜合性實(shí)驗(yàn)”項(xiàng)目,提高了學(xué)生設(shè)計(jì)復(fù)雜數(shù)字系統(tǒng)的能力和參與學(xué)科競賽的積極性[9]。

如表1 所示,學(xué)生在完成傳統(tǒng)數(shù)字電路實(shí)驗(yàn)教學(xué)后(大學(xué)第四學(xué)期),其設(shè)計(jì)的電路規(guī)模僅為幾十個(gè)邏輯門(如交通燈等),而參加課程改革的學(xué)生(大學(xué)第二學(xué)期),其設(shè)計(jì)的復(fù)雜數(shù)字系統(tǒng)規(guī)模大都在10 000邏輯門以上,學(xué)生設(shè)計(jì)數(shù)字系統(tǒng)的能力和水平得到很大提升[10]。學(xué)生通過自主完成實(shí)驗(yàn)項(xiàng)目設(shè)計(jì)、方案優(yōu)化、硬件測試、撰寫報(bào)告等工作,鍛煉和提升了實(shí)踐創(chuàng)新和工程應(yīng)用能力,這些學(xué)生近三年共主持國家級(jí)、省級(jí)創(chuàng)新創(chuàng)業(yè)計(jì)劃13 項(xiàng)。

表1 課程改革班與傳統(tǒng)實(shí)驗(yàn)教學(xué)班情況對(duì)比

4 結(jié)語

經(jīng)過多年實(shí)踐與改革,基于FPGA 開發(fā)設(shè)計(jì)的綜合創(chuàng)新性實(shí)驗(yàn)教學(xué)項(xiàng)目已成功應(yīng)用于我校數(shù)字電路實(shí)驗(yàn)教學(xué),具有如下特點(diǎn):

(1)團(tuán)隊(duì)教師以開放式遠(yuǎn)程虛擬仿真實(shí)驗(yàn)平臺(tái)建設(shè)為契機(jī),拓寬數(shù)字電路實(shí)驗(yàn)教學(xué)時(shí)空領(lǐng)域,學(xué)生突破時(shí)空束縛,實(shí)現(xiàn)“處處能學(xué)、時(shí)時(shí)可學(xué)”的泛在學(xué)習(xí)[11]。

(2)采用“小班化、翻轉(zhuǎn)實(shí)驗(yàn)室”模式進(jìn)行綜合創(chuàng)新性實(shí)驗(yàn)教學(xué),激發(fā)了學(xué)生實(shí)驗(yàn)的自主性和創(chuàng)新性,符合創(chuàng)新能力培養(yǎng)要求。

(3)將傳統(tǒng)數(shù)字技術(shù)與現(xiàn)代數(shù)字技術(shù)有機(jī)融合,采用FPGA 進(jìn)行實(shí)驗(yàn)設(shè)計(jì),有效解決了在有限課時(shí)內(nèi)完成復(fù)雜數(shù)字系統(tǒng)設(shè)計(jì)的難題[12]。

- 實(shí)驗(yàn)技術(shù)與管理的其它文章

- 沈陽工業(yè)大學(xué)風(fēng)力發(fā)電實(shí)驗(yàn)室.

- 高校實(shí)驗(yàn)室環(huán)境安全智能監(jiān)控系統(tǒng)設(shè)計(jì)

- 預(yù)防醫(yī)學(xué)實(shí)驗(yàn)室廢液管理及國外高校經(jīng)驗(yàn)啟示

- 基于機(jī)器視覺提高實(shí)習(xí)安全性的金工實(shí)習(xí)教學(xué)改革探索

- 高校三級(jí)實(shí)驗(yàn)室安全保障體系的建立

- 基于網(wǎng)絡(luò)層次分析法的高校政府采購績效評(píng)價(jià)研究