系統(tǒng)級電源完整性的時-頻分析方法研究

虞菊花 常興治 胡春芬

摘 ?要:電源完整性已經(jīng)成為高速電路領(lǐng)域中的一個重點分析對象,從芯片架構(gòu)設(shè)計到芯片內(nèi)的電源分布設(shè)計,從芯片封裝布局到印刷電路板布局,都在考慮如何在電源完整性設(shè)計和自身系統(tǒng)性能設(shè)計之間找到最佳平衡點。文章進行系統(tǒng)全鏈路的參數(shù)分析,分析系統(tǒng)中各個部分對阻抗曲線如何產(chǎn)生作用,初步判斷系統(tǒng)的性能;同時,通過時域仿真模型分析,確定整體的鏈路能否達到芯片設(shè)計指標,采用時-頻仿真分析方法,對實際整體的鏈路中的PI現(xiàn)象進行有效的分析,為芯片的設(shè)計提供了良好的解決方案。

關(guān)鍵詞:電源完整性;頻域/時域分析;電源分配系統(tǒng);阻抗曲線

中圖分類號:TN86 ? ? 文獻標識碼:A 文章編號:2096-4706(2020)04-0062-03

Abstract:Power Integrity (PI) has become a key analysis object in the field of high-speed circuits. From the chip architecture design to the power distribution design in the chip,from the chip packaging (PKG) layout to the printed circuit board (PCB) layout,we are considering how to find the best balance between the power integrity design and the performance design of our own system. This paper analyzes the parameters of the whole link of the system,analyzes how the various parts of the system affect the impedance curve,and preliminarily judges the performance of the system;at the same time,through the analysis of the time-domain simulation model,determines whether the overall link can reach the chip design index. In this paper,the time-frequency simulation analysis method is used to effectively analyze the PI phenomenon in the actual overall link,which provides a good solution for the chip design.

Keywords:power integrity;frequency/time domain analysis;power distribution system;impedance curve

0 ?引 ?言

電源完整性(PI)通常是指集成電路的供電電源經(jīng)過印刷電路板(PCB)和芯片封裝(PKG)等一定的電源分布網(wǎng)絡(luò)后,可以提供給晶體管供電的完整程度。PI不僅受系統(tǒng)鏈路上電源分配網(wǎng)絡(luò)(PDN)的影響,還受芯片內(nèi)部晶體管工作狀態(tài)的影響。因此,有必要分析全鏈路系統(tǒng)級的PI狀態(tài)。由于全鏈路系統(tǒng)級的PI分析牽涉的范圍較廣,需要對系統(tǒng)的互連、封裝、后端、架構(gòu)等有深入的理解,并在系統(tǒng)范圍內(nèi)進行仿真分析和設(shè)計測試,最終才能使所設(shè)計的芯片達到電源供電的最佳狀態(tài)。

全鏈路系統(tǒng)級PI的概念雖提出已久,但是業(yè)界尚沒有提出一套有效的仿真分析和解決該難題的方法。PCB和PKG的PDN可以通過仿真工具提取相對準確的散射S參數(shù),本文便是基于這些模型,提出了研究系統(tǒng)級PI的仿真分析方法,具體地分析全鏈路系統(tǒng)級的關(guān)鍵參數(shù),并驗證我們提出的分析方法的正確性和可靠性。

1 ?系統(tǒng)級電源完整性問題

系統(tǒng)全鏈路的電源分配網(wǎng)絡(luò)PDN主要由四個部分組成:電壓調(diào)節(jié)模塊(VRM)、PCB的電源分配網(wǎng)絡(luò)、封裝的電源分配網(wǎng)絡(luò)及芯片(die)內(nèi)的電源分配網(wǎng)絡(luò),如圖1所示。

PDN系統(tǒng)中VRM是供電的源端,其通過控制DC-DC轉(zhuǎn)換電路為器件提供穩(wěn)定的工作電壓。要確保PI的有效性,VRM需要具有小信號的輸出阻抗,即在負載電流允許的整個范圍內(nèi),輸出電壓的紋波較小。在直流DC情況下,VRM提供低阻抗輸出,供電電源穩(wěn)定較容易滿足,但是隨著頻率的增大,輸出阻抗增加,很難保證負載電流變化較大時的輸出穩(wěn)定性。在實際PCB布板設(shè)計時,常常在VRM附近并聯(lián)幾個大容量的電容來降低其輸出阻抗,抑制VRM的低頻輸出紋波。

PCB和PKG的電源分配網(wǎng)絡(luò)是系統(tǒng)級電源分配網(wǎng)絡(luò)的重要組成部分,其作用就是為所有的器件提供一個穩(wěn)定均衡的電壓。目前,高速電路設(shè)計的集成度越來越高,成本壓力卻越來越大,PCB和PKG的層數(shù)降低,布局空間非常受限。同時,信號走線要求嚴苛,從而導(dǎo)致電源地平面布局的不合理,如何利用其有限的空間,達到最佳的PDN性能,成為互連工程師們研究的課題。

PCB和PKG的PDN設(shè)計主要包括三個方面:電源地平面,去耦電容和過孔。

電源地平面,是PDN一個非常重要的組成部分,主要表現(xiàn)為分布式的高頻小電容器,其合理的疊層結(jié)構(gòu)和走線布局可較好地改善電源噪聲,但是最大的問題在于其會形成電磁諧振腔,成為噪聲源。

在互連工程師進行布局設(shè)計的時候,可盡量選擇諧振頻率與實際工作頻率相近的電容,來改善電源噪聲,一般在VRM周圍會放置大容量Bulk電容,在PCB上會放置中小電容,來減小中低頻噪聲,在PKG上使用埋容等方式來解決中高頻噪聲。

過孔,不管是在電源地平面還是電容的使用中都會涉及到。過孔如何在有限的布局空間中發(fā)揮最大的作用,已經(jīng)成為PI工程師必須面臨和重視的一個問題。電源地平面之間利用有限的過孔可減少其電感,而電容打過孔時也必須注意盡量靠近焊盤,或直接打在焊盤上,也可用多個過孔連接電容到電源地平面,減小其寄生參數(shù)。

片上電源分布網(wǎng)絡(luò)是由很多電源Mesh單元組成,由于片上PDN緊靠開關(guān)電路,其電感非常小,因此可以在頻率為GHz的寬頻范圍內(nèi)提供低阻抗路徑。但是由于工藝的更新,電路集成度增大,引起片上互連電阻的增加,器件開關(guān)速度越來越快,工作電壓也越來越低以降低功耗,種種因素都導(dǎo)致了電源噪聲的增大和對噪聲容限的降低。因此,如何設(shè)計最佳片上PDN成為解決高頻噪聲的關(guān)鍵。一般來說,片上PDN主要體現(xiàn)在電阻和電容兩個方面,使用Apache的Redhawk等工具提取的參數(shù)文件,也主要包括這兩個參數(shù)。片上電阻增大會引起阻性IR-Drop(壓降),但在一定程度上增加了Q值;片上電容可看成局部電荷源,能夠有效地降低高頻狀態(tài)下的電源分配阻抗,相當于高頻的開關(guān)電流被“去耦”,噪聲降低。片上電容主要包括本征去耦電容和外加電容,本征去耦電容主要包括晶體管的分布電容/電源地的分布電容等,光靠這些不足以將高頻噪聲控制在可接受范圍內(nèi),因此,在現(xiàn)在的電源設(shè)計過程中,都需要外加電容,即Intentional Decap來改善噪聲,以達到電源要求。

當芯片中的晶體管發(fā)生高速翻轉(zhuǎn)的時候,形成較大的瞬態(tài)電流,這時候必須保證芯片端PDN的輸入阻抗較小,才能滿足供電電源的容限,芯片的電源才會穩(wěn)定,芯片才能正常工作。

綜合上述的PI理論分析可以看到,電源完整性問題的根源主要有兩個方面:一是系統(tǒng)級的電源分配網(wǎng)絡(luò)存在電感,從而造成輸入阻抗過大,引起較大的電磁干擾和電源噪聲;二是在晶體管高速開關(guān)狀態(tài)下,瞬態(tài)跳變電流過大,會導(dǎo)致瞬態(tài)負載電流和噪聲電流過大。

2 ?時頻域分析

本文使用頻域仿真方法對PDN進行分析,研究瞬態(tài)跳變電流的變化,利用瞬態(tài)電流和系統(tǒng)全鏈路PDN的S參數(shù)評估系統(tǒng)級的PI問題,同時使用時域仿真模型對其進行全鏈路分析。

系統(tǒng)全鏈路的阻抗曲線,首先應(yīng)該重點關(guān)注的便是諧振頻點,以及對應(yīng)的幅度。全鏈路的諧振頻點由封裝及PCB的電感與die上的電容相互作用而形成,如本文中,PCB的電感大約為2.7 nH,封裝的電感為900 pH,die上的電容為10 nF,由諧振頻點公式(3)可以計算出,諧振頻點在26 MHz左右。一般來說,我們都希望封裝和PCB的電感越小越好,中低頻噪聲可以得到很有效的抑制;而die上的電容越大越好,可以有效地降低高頻噪聲。但是如果封裝及PCB的電感與die上的電容相互作用,形成的諧振點剛好在芯片的主工作頻點周圍,我們就要好好考慮下,如何更好地避開工作頻點的諧振,使得相應(yīng)的噪聲能盡量減小。全鏈路諧振頻點處的幅度也同樣決定了噪聲的大小,該幅度主要由各部分的電阻大小決定,電阻越大,阻抗幅值越大,電阻越小,阻抗幅值越小。其次,我們可以看到鏈路的各個部分在阻抗曲線中的體現(xiàn),諧振點前,頻率越高,阻抗越大,主要體現(xiàn)了封裝和PCB的電感作用;諧振點后,頻率越高,阻抗越小,主要體現(xiàn)了封裝和die上的電容作用。

我們在設(shè)計PCB、PKG和die的電源網(wǎng)絡(luò)時,可以根據(jù)阻抗特征曲線來進行優(yōu)化改進,而最終判斷電源完整性的依據(jù),則是時域的噪聲是否能夠控制在電源噪聲裕量內(nèi)。因此,必須從時域仿真的結(jié)果來對全鏈路的電源完整性進行合理判斷。

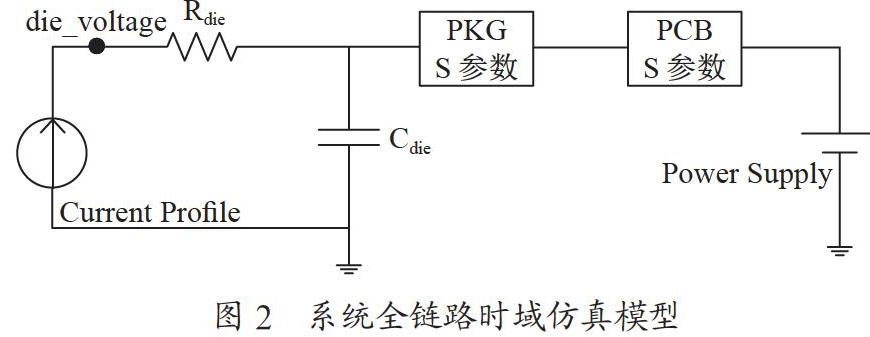

目前,電源的系統(tǒng)全鏈路時域仿真,有很多仿真工具可以做,但是仿真需要的參數(shù)、文件及方法都大體相似。如圖2所示的系統(tǒng)全鏈路仿真模型所示,PCB的VRM模塊,一般很難與中高頻的工作頻點同時仿真,因此,VRM輸出的電源,我們可按照理想電源進行連接,若要單獨考慮此部分的影響,可單獨做電源完整性仿真,本文不做詳細討論;PCB和PKG都由S參數(shù)來體現(xiàn)其性能,也可將兩者的S參數(shù)轉(zhuǎn)換成電路文件進行仿真,解決數(shù)值收斂問題;die的模型,各個設(shè)計階段提供的電容和電阻是不一樣的,但是都會給出Cdie和Rdie的參數(shù)或者文件,die的模型在頻域上主要受這兩個參數(shù)的影響,但是在時域上還有一個非常重要的文件,即典型的、最高功耗或其他工作模式的電流文件(Current Profile),該電流文件反映了各個工作模式下,相應(yīng)電源的工作電流曲線,在一定程度上決定了電源完整性評估的準確程度。

因此,電源的系統(tǒng)全鏈路時域仿真,在VRM電源已知、PCB和PKG的電源S參數(shù)模型已經(jīng)提取、Cdie和Rdie已經(jīng)給出的情況下,重點來關(guān)注die上的電流文件。

電流文件一般分為三種描述方式,一種為人為構(gòu)造曲線,此曲線結(jié)合頻域仿真結(jié)果與實際工作場景,人為地構(gòu)造噪聲相對惡劣的電流跳變曲線;另一種為瞬間跳變曲線,該工作狀態(tài)下跳變的電流幅度與跳變時間之間的比值最大,由數(shù)字前端給出該曲線;最后一種為經(jīng)典的Current Profile,此曲線是由仿真工具對最后提交的前后端網(wǎng)表進行仿真,得到的某個工作場景下的電流曲線,選擇何種最能體現(xiàn)噪聲最大值的工作場景由后端仿真工程師與前端數(shù)字工程師共同討論決定,由后端工程師給出該曲線。第一種評估方法能夠讓PI工程師在各類仿真分析條件不甚明朗的情況下,給出風險評估初判斷,也是我們研究所關(guān)注的。

若該3.3 V電源的指標要求為10%,則此噪聲可滿足電源完整性要求;若超過指標要求,則需要綜合考慮die、PKG和PCB的影響因素,得到最佳的平衡點,以最合適的方式調(diào)整各部分的布局。

總結(jié)以上內(nèi)容,我們可以知道,不管是頻域還是時域仿真方法,對電源完整性的評估都起到了很重要的作用,綜合合理地使用這兩種方法進行最恰當?shù)姆治觯拍鼙WC芯片達到最佳性能。

3 ?結(jié) ?論

電源完整性在芯片設(shè)計過程中占據(jù)了非常重要的地位。電源是否穩(wěn)定可靠,除了對芯片的性能會產(chǎn)生影響之外,更會影響PLL、AD電路等性能,從而直接導(dǎo)致芯片的功能受限。本文從時域和頻域的兩個角度,分析了系統(tǒng)全鏈路的電源完整性問題,重點研究了從頻域的角度分析電源完整性出現(xiàn)在各個部分時,工程師應(yīng)該如何采取相應(yīng)的措施改善或解決PI問題,最后通過時域仿真驗證系統(tǒng)是否能達到電源的要求。

參考文獻:

[1] SMITH L D. Frequency Domain Target Impedance Method for Bypass Capacitor Selection for Power Distribution Systems [C]//DesignCon,2006.

[2] 周磊,劉慶想,張健穹,等.印制電路板去耦網(wǎng)絡(luò)優(yōu)化設(shè)計 [J].微波學(xué)報,2014,30(S1):612-615.

[3] SMITH L D,ANDERSON R E,F(xiàn)OREHAND D W,et al. Power distribution system design methodology and capacitor selection for modern CMOS technology [J].IEEE Transactions on Advanced Packaging,1999,22(3):284-291.

[4] CHOI M J,PANDIT V S,RYU W H. Controllable parameters identification for high speed channel through signal-power integritycombined analysis [C]//58th Electronic Components and Technology Conference.IEEE,2008.

[5] REN J H,OH D,CHANG S,et al. Statistical link analysis of high-speed memory I/O interfaces during simultaneous switching events [C]//2008 IEEE-EPEP Electrical Performance of Electronic Packaging.IEEE,2008.

作者簡介:虞菊花(1985-),女,漢族,江蘇常州人,教師,講師,碩士研究生,主要研究方向:信號完整性與電源完整性、信息安全與管理。