納米級超大規模集成電路芯片低功耗物理設計分析

張博文

(運城學院,山西 運城 044000)

1 納米級超大規模集成電路芯片功耗構成

動態功耗可分為P 溝道MOS 晶體管、N 溝道MOS晶體管同一時間導通形成的短路電流引起的功耗以及電容器充電和放電引起的功耗。靜態功耗包括擴散區、襯底形成的反向偏置二極管的漏電流、通過柵氧的電流引起的功耗。由于泄漏電流大小和溫度有關,因此芯片溫度升高時,漏電流引發的靜態功耗急劇增加,而且泄漏電流與晶體管大小成反比。動態功耗受開關頻率、負載、電源電壓影響,芯片電壓越高,功耗越大。因此,要優先選擇可在低電壓運行的芯片,以降低整體功耗。本文主要針對超大規模集成電路功耗優化設計進行研究[1]。

2 納米級超大規模集成電路芯片低功耗物理設計方法

2.1 工藝層面的芯片低功耗物理設計

工藝層面的芯片低功耗物理設計基本思路是通過改進工藝、優化電子元件布局及縮小低電子元件大小等方式實現低功耗設計目標。目前,集成電路制造工藝已經邁入7 nm 級,電路集成度急速增加,單位面積芯片中集成的晶體管數量達千億級,導致芯片功耗快速增長。晶體管特征尺寸與其漏電流引發的靜態功耗成反比。為了降低靜態功耗,可利用包括多種閾值電壓的單元庫,盡量用閾值更高的元件,以提高閾值電壓,降低功耗。此外,還可以改進工藝,根據CMOS 晶體管的襯底偏置效應適當提高晶體管閾值電壓,減少漏電流,從而降低靜態功耗。例如,采用立體鰭狀柵結構增強元件開關特性,使元件關閉時漏電流顯著降低,還可以用高介電常數材料替換二氧化硅、多晶硅柵極,以減少柵極中寄生電容[2-3]。

2.2 電路結構上的芯片低功耗物理設計

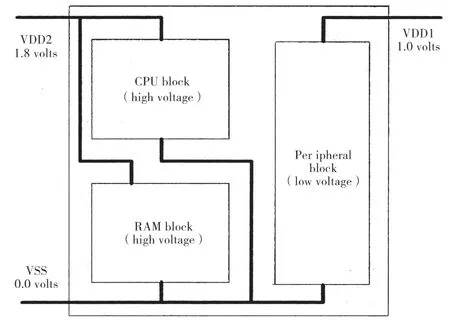

通過優化電路結構、電路實現途徑的方式來實現低功耗設計目的。供電電壓越高,動態功耗越大,即便是很小的電壓變化都能顯著降低功耗。基于此,在電路結構方面的低功耗設計中,降低供電電壓是一種基本思路。例如,供電電壓降低0.6 V 時,動態功耗會降低40%左右。而芯片模塊的供電電壓可能存在差異。圖1 為多供電電壓設計。

圖1 多供電電壓設計

圖1 中處理器CPU、主存RAM 模塊運行速度要盡量快,但外部接口的運行速度要求不高。模塊運行速度和供電電壓成正比,為了在速度與低功耗之間找到平衡,CPU、RAM 模塊的供電電壓VDD2為1.8 V,外部接口模塊的供電電壓VDD1為1.0 V。這屬于多供電電壓低功耗設計方案,芯片性能要求不同,適用于芯片的多供電電壓低功耗設計方案也存在差異。

2.3 門級層面的芯片低功耗物理設計

2.3.1 單元映射

在邏輯門層面描述電路時應使用邏輯門單元。執行門級綜合時如為手動輸入,則綜合器將從合成庫中選擇邏輯門模塊。大多數工藝提供商會提供低功耗單元庫。選擇這樣的單元庫可以降低功耗,這是使用單元格映射的基本思路。此外,活躍度高的節點要盡量置于邏輯單元中,以降低其負載電容,從而降低功耗。最常見的設計思路就是增加電路的輸入門,如三輸入門,以減少邏輯門數量并縮短總線長度,達到降低功耗的目的。

2.3.2 公因子提取

提取公因子以精簡邏輯網絡,降低電路結構復雜程度,從而降低功耗。例如,設計者可通過多種邏輯結構實現同一個函數,雖然在面積、時間方面不同邏輯結構的差異不大,但輸入信號反相頻率存在差異,導致電路功耗存在較大差異。因此,在設計電路時,由高速旋轉信號控制的負載應盡可能小,即這些信號應更靠近輸出,即元件越小越好。在設計電路時,有必要弄清每個信號的活躍度,然后根據每個信號的活動性提取公因子,并合理地對每個信號在電路中的位置進行排序。

2.3.3 門尺寸優化

通過縮減路徑非關鍵網關尺寸,實現低功耗設計目標。在電路性能不受限制的情況下,可縮小全部電路中所有邏輯門的尺寸,將門尺寸優化轉為延遲限制下的功耗最低優化問題。首先可以根據路徑對時間約束進行線性化,再求解線性方程獲得全局最優解。由于采用了低帶寬的模塊,電平轉換速度減慢,從而導致短路電流增加,這是優化門尺寸的一個限制因素。對于給定時間范圍內優化離散快門大小變化功率問題,其基本思想是從最小的門開始逐步增加關鍵路徑。大小以滿足限制并最小化通道切換活動。

2.4 系統層面的芯片低功耗物理設計

2.4.1 軟硬件劃分

軟硬件劃分是指將電路系統分為軟件、硬件兩部分。目前,很多知名電子設計自動化EDA 公司已相繼發布了系統層面的電路設計軟件,能夠實現電路系統層面軟硬件劃分,被行業廣泛應用。例如,Synopsys 公司的CoCentric 可以同時設計、仿真、實現多個系統核心元器件,Cadence 推出的Virtual Component Co-design可以定義、分析、優化系統層面的電路設計,給電路設計者提供了系統集成、驗證所需技術和工具,圖形化界面方便設計人員進行協同設計和驗證。利用這些軟件設計人員可以從系統層面對軟件、硬件兩個角度綜合考慮,確定最佳設計方案。

2.4.2 功耗管理

功耗管理包括動態、靜態兩種管理方式。動態功耗管理是指根據實際情況控制空閑模塊關閉,以減少功耗。靜態功耗管理的對象是電路工作模式。如果系統空閑,則停止芯片工作,休眠系統,從而減少功耗。動態功耗管理實現需要操作系統,因此其應用受到限制。

2.4.3 指令優化

指令優化流程包括如下4 步。

(1)提取指令集。合理選用指令集可以讓系統功耗降至最低。

(2)合理選擇指令長度,提高程序代碼密度,從而降低對存儲器的訪問,降低功耗。

(3)優化指令編碼,減少指令讀取時總線信號翻轉,以降低功耗。

(4)壓縮指令,指令在內存中進行壓縮,輸入CPU 之前再解壓可以降低CPU 功耗。

3 基于Golden UPF 的低功耗物理設計流程

Golden UPF 主要有便于追蹤、無需修改UPF 文件及設計效率高等優點。因此,本次研究基于Golden UPF(Unified Power Format)進行低功耗物理設計,在滿足電路性能需求的情況下實現低功耗設計目標,設計基本流程如圖2 所示。

圖2 基于Golden UPF 的低功耗物理設計流程

在開始設計前要準備好相應資料,主要包括如下3 個。

(1)網表。使用邏輯綜合工具,將設計好的RTL代碼轉換為基于特定工藝庫的邏輯門級網表。

(2)SDC 文件。用Tcl 語言編寫用于表述設計目標的一種文件,如面積、時序、功耗等方面的設計目標。目前,電路低功耗設計多采用多重邊角多重模式(MCMM)需多個SDC 文件來確保設計正確。

(3)UPF 文件。Unified Power Format 文件對電路低功耗物理設計思路進行了規定,用于設計的全過程。

準備好這些資料之后,通過低功耗物理設計將網表轉換成GDS2 格式版圖文件,經多次ECO 修復時序違例后,在MVtool 中檢查低功耗器件插入正確性。再抽取版圖RC 參數,使用功耗分析軟件讀取ICC 輸出的門級網表、對應UPF 對電路功耗進行計算。

4 結論

本文簡要介紹了電路功耗的構成,分別從工藝、電路、門、系統四個層面研究了低功耗物理設計方法,但是低功耗設計領域還有很多待解決的問題,因此還有待進一步研究,以不斷降低芯片功耗。