引信高頻脈沖編碼信號測試裝置優化

張 鵬,謝 銳

(中北大學儀器科學與動態測試教育部重點實驗室,山西 太原 030051)

0 引言

采用電磁感應技術通過設定出炮口處的線圈,可控制引信工作方式。引信隨彈丸發射通過炮口處的發射線圈將編碼信號傳輸給引信的接收線圈,此過程信號頻率高、速度快、環境惡劣[1]。引信系統是否能夠可靠穩定工作決定著武器的性能能否充分發揮,因此在高沖擊、高頻率、強干擾的動態惡劣環境下,有效的試驗與測試引信輸出信號質量是否符合系統設計要求非常必要。

近年來專用數據采集卡迅速發展,例如西安電子科技大學研制的VPX3-SBD讀/寫速度分別為296 MB/s和304 MB/s,768 GB的超大容量存儲[2]。中北大學針對動態數據的采集存儲先后研制出侵徹測試的小容量記錄儀和多通道彈載大容量記錄儀,存儲容量大于100 GB,讀取速度100 Mbps。但現有數據采集卡不能完成對高頻脈沖編碼信號的采集。

中北大學研制的500 MHz采樣速度的高頻脈沖編碼信號測試儀在調試過程中電路工作時易發熱影響模擬信號質量,而且由于采樣時鐘的抖動,容易引起ADC采樣誤差導致信噪比降低。對模擬狀態下引信輸出脈沖編碼信號的測試研究不能滿足引信測試的需求。針對上述問題,提出了一種基于高速數據采集存儲技術的高頻脈沖編碼信號采集存儲測試裝置。

1 高速數據采集技術

高速數據采集存儲系統的主要技術指標有模數轉換、信號調理、信號完整性、電磁兼容性、電源完整性和存儲技術。高速采集系統的關鍵是高速電路的設計和部分高速信號的時序約束。通常定義的高速電路為數字信號的傳輸延時大于1/2倍的邊沿時間或數字電路的頻率大于45 MHz。當系統時鐘頻率超過100 MHz或上升沿小于1 ns時也稱為高速系統。本文采集系統屬于高速電路,對高頻信號的采集存儲必須考慮傳輸線效應引起的串擾、反射、延時等信號完整性問題以及高頻電路中對電容的等效處理問題。

2 基于高速數據采集存儲技術的測試裝置

2.1 測試裝置總體方案

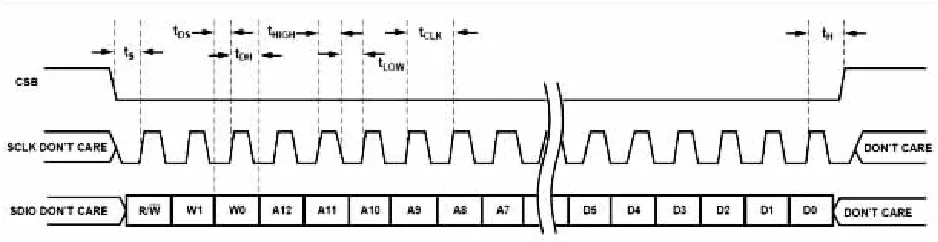

結合高速電路設計,測試系統整體分為模擬部分和數字部分。從采樣頻率、采樣時間、系統低功耗、小體積等方面考慮,模擬部分對信號調理電路設計和高速ADC芯片的選型以及電路原理設計,不僅提高了采樣精度與速度,而且解決了時鐘抖動引起的低信噪比問題[3]。數字部分以FPGA為控制核心,將采樣到的數據緩存到SSRAM,采集完成后再轉存到Flash,完成FPGA,SSRAM以及Flash的芯片選型和功能仿真。系統硬件框圖如圖1所示。

圖1 系統硬件框圖Fig.1 System hardware block diagram

系統工作流程:系統上電后處于待觸發狀態,當接受到外部觸發信號后,系統進入采集狀態,為滿足A/D轉換輸入信號的幅值要求,待測信號首先經過衰減電路,再經差分電路后信號轉換為高速LVDS信號并送至A/D轉換芯片,A/D轉換后輸出的數字信號經FPGA處理后寫入SSRAM緩存,為使采集到的數據不易掉電丟失,一次采集結束后再將緩存數據全部轉存至Flash,此時完成一次完整的采集存儲。再用USB3.0專用讀數口將回收裝置與計算機連接,利用讀數軟件將數據信號讀取到LabVIEW上位機進行顯示,并完成進一步的數據分析和處理。

2.2 測試裝置硬件電路設計

2.2.1信號的衰減

接入采集電路的引信裝置輸出阻抗為1.2 kΩ,輸出信號集中在30 MHz,最高頻率分量為50 MHz,最大幅值為7 V,示波器采集到的原始引信信號如圖2所示。從圖2中明顯得知最大幅值在7 V左右(縱軸每格2 V),最窄脈寬約為320 ns,上升時間約為30 ns。而設計要求A/D轉換電路的輸入電阻不小于1 MΩ,輸入電容不大于8 pF。由于輸入信號幅值較大需要設計專門幅值衰減電路以匹配后端ADC的輸入范圍。

圖2 原始引信信號Fig.2 Original fuze signal

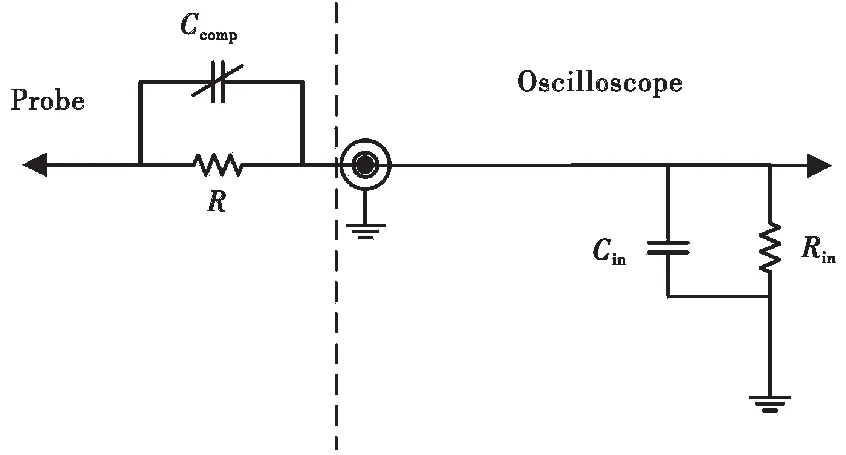

由于待采信號頻率高,設計衰減電路必須考慮電阻和電容的分布參數對信號的影響,故設計衰減電路參考示波器帶電容補償的高阻無源探頭的衰減原理,如圖3所示。探頭端由可調補償電容Ccomp和電阻R并聯構成,示波器內部等效為電容Cin和Rin的并聯結構,補償電容用來調整示波器探頭的輸出電容值使其總電容值匹配示波器內部電容[4]。

圖3 示波器無源探頭結構Fig.3 Oscilloscope passive probe structure

對以上電路結構做如下分析:

(1)

式(1)中,A為(低頻信號的)衰減比例。從示波器的輸入端口來看:

(2)

(3)

根據示波器上帶補償的高阻無源探頭信號衰減理論,要使此電路對高頻輸入信號有同樣的衰減比例,須保證ZL上的電壓幅值與輸入信號的幅值之比等于A,即:

(4)

對式(4)進行化簡整理可得:

(5)

若要使式(5)對于不同的ω恒成立,即衰減比例與輸入信號的頻率ω無關,則需要:

RinCin=RCcomp

(6)

又設計要求采集電路輸入端電阻不小于1 MΩ,輸入電容不大于8 pF。故設計電路中脈沖編碼信號通過屏蔽線進入系統,通過可調電容來補償屏蔽線的分布電容,其輸入阻抗為1 MΩ,輸入電容約為5 pF。

2.2.2阻抗變換與優化仿真

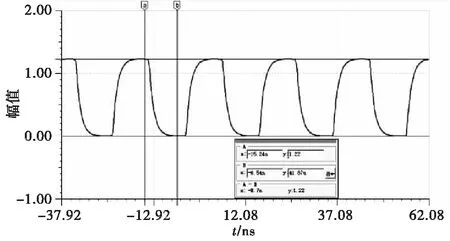

之前研制的500 MHz采樣速度高頻脈沖編碼信號測試儀,引信輸出編碼信號衰減后直接送入單端轉差分運放電路,沒有做阻抗匹配設計,導致差分運放的兩個反饋回路不平衡,造成輸出信號共模電壓被抬高出現消頂現象。為隔離高頻脈沖測試裝置的信號輸入端和ADC的驅動運放,從而實現阻抗匹配,故選擇ADI公司高速低噪聲的寬帶運放ADA4817-1實現阻抗變換[5],為了匹配ADC轉換器對輸入電平的要求,將ADA4817的放大倍數設置為3.5倍。輸入方波信號上升沿為1 ns,頻率為50 MHz,峰峰值為350 mV,仿真結果如圖4所示。幅值為1.22 V,上升沿變慢。被測信號集中在30 MHz附近,對原始信號幾乎沒影響。匹配電路如圖5所示。

圖4 ADA4817輸出的方波信號Fig.4 ADA4817 output square wave signal

圖5 ADA4817原理圖Fig.5 ADA481schematic diagram

ADA放大倍數是1+R26/R25=3.5,電容C38和電阻R29是用來降低或者消除運放閉環增益在接近增益衰減處可能出現的增益尖峰。同時R29也作為信號源的輸出阻抗和50 Ω傳輸線相匹配。NPD是ADA4817的掉電引腳,通過FPGA的控制可以實現ADA4817的低功耗。

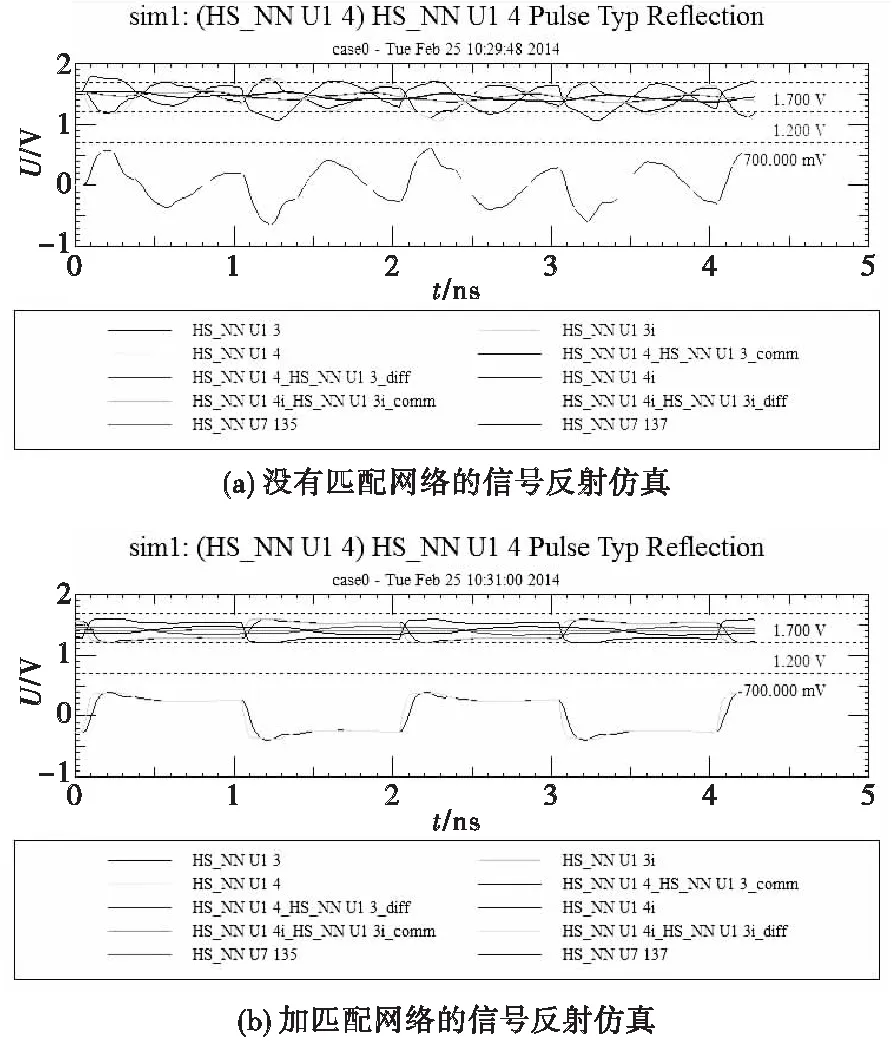

AD9434的輸入信號必須為差分信號,而衰減后的信號仍為單端模擬信號,必須對其差分化后才能送至后級A/D轉換器。考慮到噪聲引入A/D轉換的可靠性與準確性以及信號采集的完整性,選用集成調理芯片AD8138實現輸入信號的差分化[6]。結合后端電路,為降低AD9434開關電容的影響,在AD8138輸出端接一對33 Ω電阻。AD8138連接衰減電路的輸出端并聯50 Ω電阻以驅動同相輸入端500 Ω端接電阻。設置AD9434輸出信號為上述方波信號,分別對加匹配網絡和沒有加匹配網絡的電路信號進行反射仿真,結果如圖6所示。

圖6 反射仿真結果Fig.6 Reflection simulation results

由圖6可知,加了匹配網絡的仿真結果信號完整性較好,輸出基本上為方波信號,而沒有加匹配網絡的電路信號波形明顯失真,出現嚴重反射現象。

2.2.3高速ADC

ADC是數據采集系統的核心,ADC的性能參數往往決定著整個采集系統的性能[7]。為了提高分辨率,降低共模誤差,綜合考慮目前市場上常見的500 MSPS的ADC位數、信噪比、有效位數、信納比等性能指標,輸入信號、輸出信號類型、功耗和供電等參數選擇ADI公司12位的AD9434,它是基于BiCMOS制程工藝的流水線型開關電容ADC,內部集成差分輸入緩沖器,且使用LVDS(ANSI-644)差分信號輸出采樣數據。

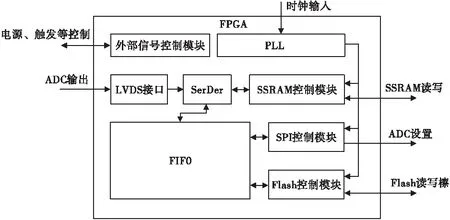

AD9434可以通過SPI接口配置內部寄存器從而實現特定的功能或操作。AD9434有三條SPI控制線,SCLK/DFS(串行時鐘)用于同步與ADC的讀寫通信。SDIO(串行數據輸入輸出)是一個雙向引腳,可以將數據發送到內部寄存器并從中讀取。CSB是低有效的片選,用于允許或禁用讀寫操作。SPI的時序圖如圖7所示,當CSB有效時,在SCLK的下降沿通過SDIO引腳將數據輸出或輸入,其中起始位是讀寫標志位,緊接著是寄存器相關的地址信息。

圖7 SPI時序圖Fig.7 SPI sequence diagram

2.2.4FPGA主控電路設計

裝置選用廣泛應用于設備控制領域的FPGA作為主控芯片,其內部邏輯資源豐富,編程靈活多樣,易操作,且內部采用并行執行結構,在處理不同事件時不會出現資源競爭[8]。FPGA內部由外部信號控制模塊、PLL、LVDS接口、SerDer串行器解串器、SSRAM控制模塊、SPI控制模塊、Flash控制模塊以及FIFO組成。PLL利用外部時鐘輸入進行倍頻分頻等操作分別給SSRAM、SPI以及Flash的操作提供時鐘。外部信號控制模塊主要用于對部分電源的使能、觸發信號的響應和低功耗的實現。系統工作時將ADC輸入出的數據暫存SSRAM之中,存滿即停止數據采集工作并將緩存的數據寫入Flash,隨后進入低功耗狀態。在FPGA內部通過Verilog HDL語言以及IP核設計相應的子模塊來完成。圖8所示為系統總體邏輯框圖。

2.2.5存儲器選型及時序仿真

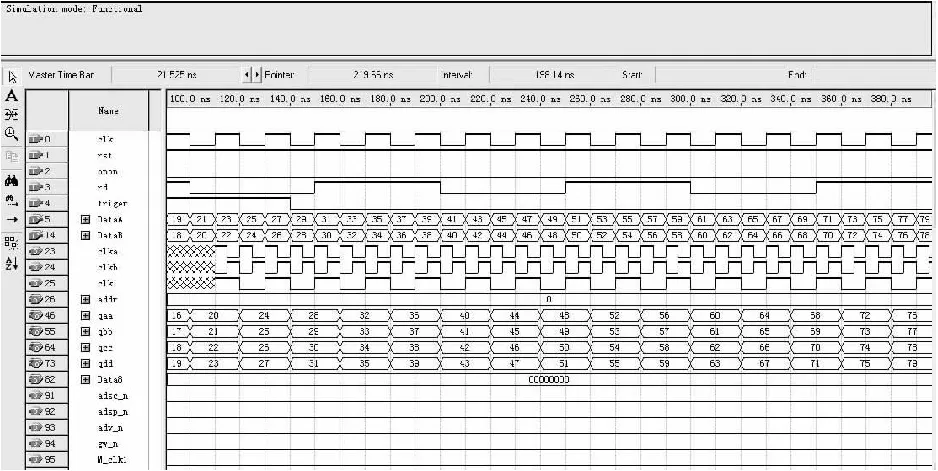

按設計要求存儲容量是30.52 Mb,因測試儀存儲容量要求不大,故采用SSRAM+FLASH的存儲方法。SRAM速度快、效率高、功耗低、操作簡單[9],考慮低成本低功耗SSRAM采用ISSI公司36 Mb存儲容量的IS61LPS102436B實現采集數據的緩存,其最高時鐘頻率達到250 MHz,在一個CLK下可以寫入4 Byte數據。IS61LPS102436B的管腳中與數據傳輸有關的引腳主要有32個數據線、4個數據奇偶校驗引腳以及18根地址線組成,其他是控制功能和時鐘功能引腳[10]。

圖8 系統總體邏輯框圖Fig.8 System overall logic block diagram

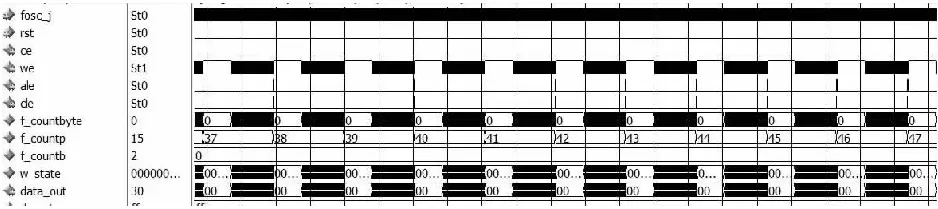

根據設計中存儲器的特點和存儲容量的需求,Flash選擇SAMSMNG公司SLC結構的K9F1G08M0M存儲芯片,其存儲容量為 (128 M+4096 K)×8 bit。SSRAM讀寫時首先需要保證片選信號有效,在控制信號有效前也需要保證數據位和地址位有效。本設計系統選用的SSRAM緩存芯片IS61LPS102436B,寫周期在時鐘上升沿時有效,寫數據需要一個時鐘周期,讀操作需要三個時鐘周期,且不能使用同一個時鐘信號,因為三個時鐘周期的功能不相同,第一個時鐘周期主要用于地址的鎖存,第二個時鐘周期用來鎖存內部讀取數據,第三個時鐘周期主要用于數據輸出。寫時序仿真如圖9所示。圖中DataA和DataB分別存放緩存數據,之后順序寫入SSRAM的數據引腳中。

圖9 SSRAM讀寫時序仿真Fig.9 SSRAM read-write timing simulation

Flash編程時序功能仿真如圖10所示。其中ce是Flash的使能端,f_countbyte[10∶0]表示一頁2K計數器,f_countp[5∶0]為64頁計數器,f_countp[9∶0]表示Flash的1 024塊計數器。仿真圖中顯示f_countp從37頁到40頁的頁操作過程,由于一塊是64頁,圖中f_countb信號仍為第一塊,仿真過程與Flash的編程操作時序一致,能夠將緩存在SSDRAM中的數據正確轉存在Flash中。由于篇幅有限,其余Flash的讀取、壞塊檢測操作功能均能實現,不再贅述。

圖10 Flash寫操作時序功能仿真Fig.10 Flash write sequence function simul-ation

3 實測采集數據結果分析

在對彈載高頻脈沖測試裝置調試完成以后,要置于彈體內采集彈丸飛行過程中接收的引信編碼信號,在炮口位置安裝磁環形成強磁場,采用磁敏感霍爾元件作為觸發信號源,裝置在出炮口被觸發,開始采集。

利用信號發生器作為信號源,輸出不同頻率的正弦波信號對本裝置進行功能驗證。

數據采集完成后,通過USB3.0專用讀數接口保存至PC機,并通過LABVIEW編寫的上位機軟件觀測采集到數據。

本測試裝置硬件電路尺寸3.6×6.8 cm用環氧樹脂灌封在直徑4.8 cm高9 cm的中空鋁材圓柱體內,隨彈丸運動時抗沖擊性強。采集信號發生器產生的50 MHz正弦波信號如圖11所示,橫軸是采樣點數,縱軸是比特值。圖11中橫軸游標差值知當以500 MHz采集速率對50 MHz正弦波信號進行采樣時,一個周期采集到10個點,采集到的正弦波信號比特值在500~3 000之間對應于183.1~1 098.6 mV(ADC滿量程為1.5 Vp_p),符合測試裝置的設計要求。

將該測試裝置置于彈丸內采集彈丸接收的引信編碼信號,圖12所示為實測原始引信脈沖信號,圖中游標顯示最窄脈寬橫坐標差值約為160點,對應于時間是342 ns,這與圖2示波器采集到的最窄脈寬320 ns基本一致。圖12中噪聲比特值約為250 b,對應于電壓為523 mV(250÷4 096×1.5×20÷3.5=523 mV)。圖13是之前實測數據,圖13中噪聲比特值約為20 b,對應于電壓為586 mV(20÷256×1.5×5=586 mV)。相比于圖13本文高頻脈沖測試裝置實測波形明顯得到改善,沒有消頂現象,提高了信噪比,能很好地反映原始編碼信號波形。

圖11 采集50 M正弦波信號Fig.11 Acquisition of 50 M sine wave signal

圖12 本裝置實測數據Fig.12 Actual measured data of this device

圖13 之前裝置實測數據Fig.13 Actual measured data of previous device

4 結論

本文提出了基于高速數據采集存儲技術的高頻脈沖編碼信號采集存儲測試裝置,該裝置通過阻抗匹配設計解決了消頂現象,對高速ADC綜合選型,提高了采樣精度,并且解決了時鐘抖動引起的低信噪比問題。以FPGA作為主控制器,控制模數轉換芯片AD9343進行數據采集和轉換,將采到的數據緩存到SSRAM中,采集完成后再轉存入Flash避免了存儲過程中數據丟失,保證了數據完整性。經實測實驗驗證,該測試裝置采樣速度可達500 MHz,采樣精度為12 b,且能穩定采集,信號完整性良好,滿足測試裝置對脈沖信號的采集存儲要求,具有一定的使用價值。該裝置對信號的串擾,EMI等仍需進一步分析研究,以降低采樣中出現的噪聲。