一種新型可修調高精度低功耗RC振蕩器設計

林雨佳,范 超

(中國電子科技集團公司第四十七研究所,沈陽110032)

1 引 言

隨著半導體行業發展,CMOS 工藝的不斷提高,芯片的尺寸越來越小。對芯片內部的各個功能模塊低功耗、高穩定、高精度等要求越來越高[1]。在集成電路領域,無論是數字集成電路中還是混合集成電路中,都使用振蕩器電路,如半橋驅動器、MCU 等電路。振蕩器模塊作為系統時鐘產生的關鍵部件,廣泛應用于電子及通信系統中,尤其在鎖相環電路、時鐘恢復電路中更是重中之重[2]。所以,以CMOS 工藝為基礎的可修調RC 振蕩器[3-5]成為近年的研究重點。

一般的RC 振蕩器輸出頻率容易受環境溫度影響,溫度特性較差。為了得到更好的溫度特性,提出一種新型可修調高精度RC 振蕩器,通過修調手段提高溫度特性,使輸出頻率變化控制在0.5%以內。

2 現有技術中的一種振蕩器

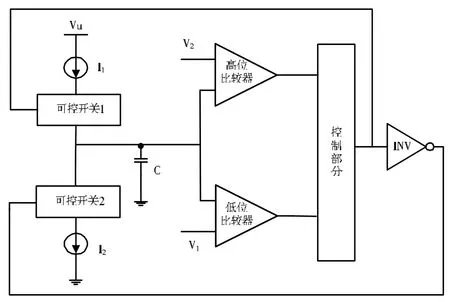

振蕩器通過邏輯控制器使能可控開關對電容器進行充放電來完成振蕩波形輸出。如圖1 所示為現有技術中的一種振蕩器的簡化示意圖,振蕩器主要由比較器、電容、可控開關和邏輯控制器構成。由開關通斷控制電容充放電的工作狀態,比較器的兩個輸入端分別是電容電壓和所設置的閾值電壓,當電容電壓高于比較器閾值電壓時,邏輯控制器輸出的方波信號將會使可控開關1 斷開,可控開關2 導通,此時電容電壓下降。當電容電壓低于比較器閾值電壓時,邏輯控制器輸出的方波信號將會使可控開關2 斷開,可控開關1 導通,此時電容電壓上升。此過程不斷反復產生連續不斷的振蕩波形。

圖1 現有技術中的一種振蕩器

振蕩器的每個時鐘周期由三部分時間組成:電容的充電時間tcharge,電容的放電時間tdischarge和比較器和邏輯控制器的延遲時間tdelay,則最終時鐘的頻率為:

由公式(1)可以看出,這種方式產生的時鐘頻率不僅與電容的充放電時間有關,而且還與比較器和邏輯控制電路的延時有關。隨著電容充放電的電壓變化,比較器輸出信號經過邏輯控制器觸發可控開關的時間,與電容電壓達到跳變值的時間相比要延后一段時間。在延后的時間段內電容電壓仍然在上升或下降,因此輸出電壓帶有誤差,電壓頻率也產生誤差。圖1 振蕩器結構中的比較器和邏輯控制器存在的延時現象,即使選擇高速器件或簡易邏輯控制方式也不可避免延時帶來的影響。

通常工程上認為比較器和邏輯控制電路的延時時間tdelay 是振蕩器頻率溫度系數差的主要誤差來源。當時鐘頻率較高時,tdelay 的影響會更加突出,所得到的時鐘頻率受溫度影響也就越大。理論上減少這項誤差的絕對值會降低誤差的溫度變化量,但實際中任何電路結構都存在不同程度的延遲。不同溫度情況延時的程度不同,使得環境溫度不同時電容充放電時間不同,導致電壓頻率受到溫度影響。

因此,需要提供一種可對延遲時間進行溫度補償的振蕩器,以解決上面提到的問題。

3 新型可修調高精度RC振蕩器設計

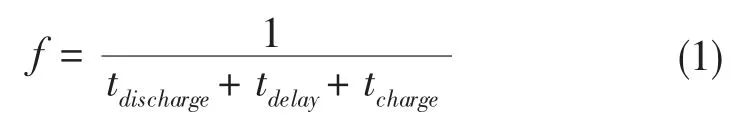

新型可修調高精度低功耗RC 振蕩器的結構如圖2 所示,包括兩個比較器、邏輯控制器、兩個電容器和修調陣列等。其中振蕩器模塊電源VDD 是由系統內部LDO 輸出提供。Rtrim1、Rtrim2 為可修調電阻陣列,通過修調電阻比例,可調節比較器閾值電壓VB,從而調節時鐘頻率。Ctrim1、Ctrim2 為可修調電容陣列,通過修調電容可調節充電速度,改變時鐘頻率。PTC、NTC 分別為正溫度系數電阻和負溫度系數電阻,用來補償充電電流溫度變化對輸出時鐘的影響。

圖2 新型可修調高精度RC 振蕩器

3.1 振蕩器中的比較器電路

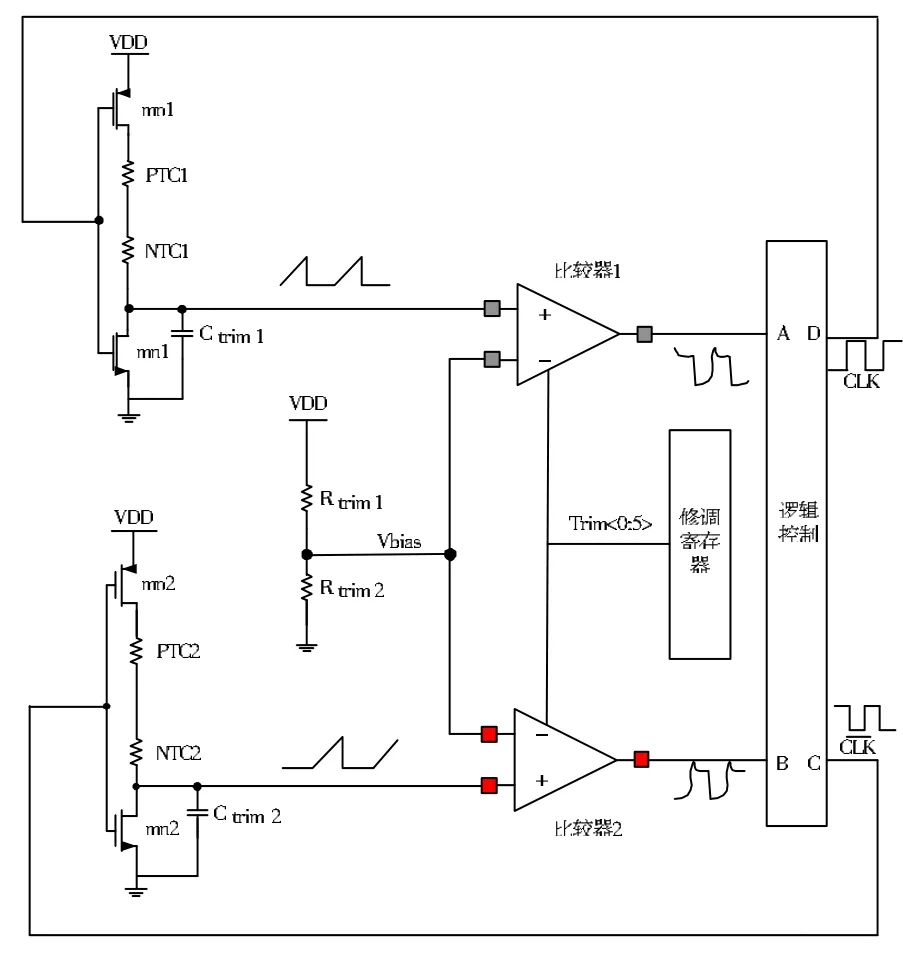

圖3 為新型振蕩器中的比較器電路,通過調節比較器輸出阻抗,引入一個或正或負輸入失調電壓,通過調節比較器延遲的極性和大小,改變其溫度系數,補償后級數字邏輯延遲時間的溫度特性。

編程寄存器修調碼,比較器[6-8]將會產生的輸入失調電壓ΔV 時。如果ΔV 為正,當VP 端電壓大于VN 端電壓至少一個時,mp2 導通,mp1、mn1、mn2 關斷,比較器輸出為高,否則輸出為低。如果ΔV 為負,當VP 端電壓小于VN 端電壓至少一個時,mp1、mn1、mn2 導通,mp2 關斷,比較器輸出為低,否則輸出為高。

圖3 新型振蕩器中的比較器電路

輸入失調電壓ΔV 的正負和大小由修調碼控制,修調碼可分為低三位Trim<0:2>和高三位Trim<3:5>, 碼數越小,有源負載阻抗越大,需要注意的是,無論是低三位還是高三位均不能出現000 碼,因為這樣不能形成通路,比較器將無法正常工作。

mp1 和 mp2 為放大管 ,mn1、mn2、mn3、mn4、mn5、mn6、mn7、mn8 組成比例電流源作為有源負載,mn3~mn8 的器件寬長比依次為 1:2:4:4:2:1,編程6 位寄存器修調碼,可分別控制mn3~mn8 的開關狀態,這些管子導通之后的阻抗與他們的寬長比成反比。這樣通過修調寄存器調節比較器輸出阻抗,引入一個或正或負輸入失調電壓,通常比較器延遲的極性和大小,直接決定其溫度系數,例如,比較器延遲為正值,那么其溫度特性為正,反之亦然。這樣的話無論后級數字邏輯的延遲時間呈現出怎樣的溫度特性,都可以通過寄存器給出的修調碼進行調節。

對修調寄存器進行編程,控制放大器有源負載的輸出阻抗,引入一部分輸入失調電壓,調節比較器延遲的絕對值,改變其溫度系數,補償后級數字邏輯延遲時間的溫度特性。

3.2 振蕩器中的邏輯控制電路

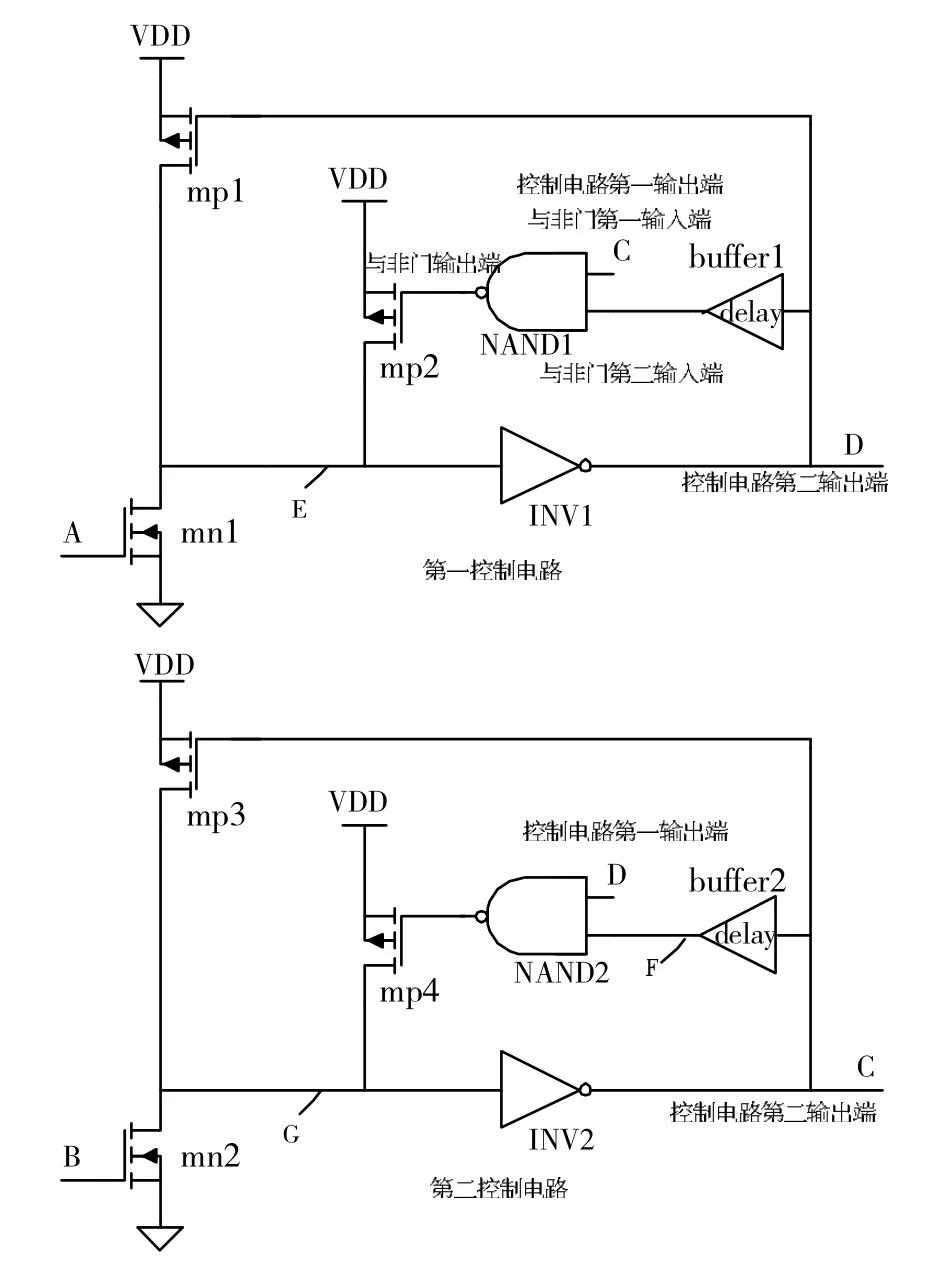

圖4 為新型振蕩器中邏輯控制電路,信號A 與信號B 互為反相信號,當A 由低變高、B 為由高變低時,信號A 將mn1 導通,E 點電壓為低,經過反相器 INV1,輸出信號 D 為高;信號 B 將 mn2 關斷,此時,F 點信號由于延遲電路buffer2 的存在,仍保持上一狀態高電平,與信號D 做與非邏輯,與非門NAND2 輸出一個瞬間低脈沖,將mp4 導通,G 點電壓為高,經過反相器INV2,輸出信號C 為低,將mp3導通,將G 點信號鎖在高電平狀態,直到B 信號高電平到來。這樣的邏輯處理,使振蕩器脈沖寬度只與電容的充電時間有關,且占空比為50%。

圖4 新型振蕩器中的邏輯控制電路

3.3 電路仿真

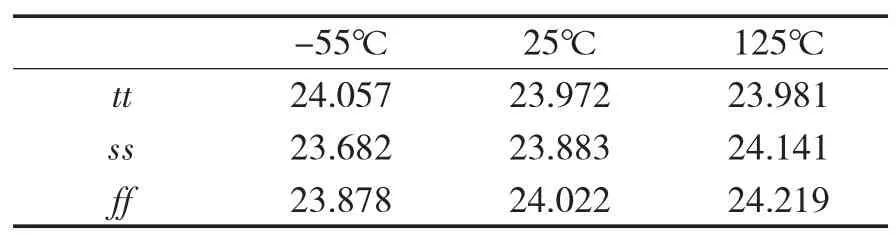

電路采用0.5μm CMOS 工藝進行設計,使用Spectre 軟件進行電路仿真,仿真結果如表1 所示。

表1 電路仿真數據 單位:MHz

4 結束語

本論文給出了一種0.5μm CMOS 工藝下設計的可修調高精度RC 振蕩器電路,該電路采用雙斜坡與偏置電壓輪流比較的工作方式實現高頻時鐘。這種做法的優勢是振蕩頻率只與充電時間有關,而與放電時間無關,不考慮放電時間延遲對頻率的影響。并且對修調寄存器進行編程,控制放大器有源負載的輸出阻抗,引入一部分輸入失調電壓,通過調節比較器延遲的極性和大小,改變其溫度系數,補償后級數字邏輯延遲時間的溫度特性。該電路已應用在某8 位微處理器中作為24MHz 內部振蕩器,該電路在溫度范圍為-55℃~125℃時,未進行修調的振蕩器受溫度影響,頻率變化范圍為1%,經過修調之后的頻率變化可控制在0.5%以內。