雙通道跳頻通信系統同步捕獲方法

孫慧賢,張玉華,唐友喜,全厚德

(1.陸軍工程大學電子與光學工程系,河北 石家莊 050003;2.電子科技大學通信抗干擾國家級重點實驗室,四川 成都 611731)

0 引言

跳頻通信以其較強的抗干擾能力、抗截獲能力和保密性能,在現代電子戰爭中具有獨特的優勢,己成為通信抗干擾技術中應用最廣泛、最有成效的技術之一[1-2]。跳頻同步技術是跳頻通信系統中最為關鍵和核心的技術,同步建立的快慢和同步系統的可靠性,直接影響系統的性能。為了進一步提高跳頻通信抗干擾能力,近年來已有多種雙通道或多通道接收的跳頻通信方法被提出[3-9]。現有的多通道跳頻通信系統大多采用單通道串行捕獲或多通道并行捕獲方法。文獻[6]中采用單通道匹配濾波方法進行跳頻同步,系統結構復雜度低,但是信號的平均捕獲時間增加。文獻[7]采用多支路并行同步捕獲方式進行跳頻同步,縮短了同步時間,提高了檢測概率,但是增加了系統的復雜度。

針對傳統跳頻通信接收機單通道串行接收捕獲時間長,多通道并行接收系統復雜度高的問題,本文設計了一種基于同步字頭法的雙通道跳頻通信同步捕獲方法,將同步字頭法與并行捕獲相結合,在兩個接收通道上進行并行捕獲,縮短同步時間,提高同步的隱蔽性和抗干擾能力。

1 雙通道跳頻通信系統結構

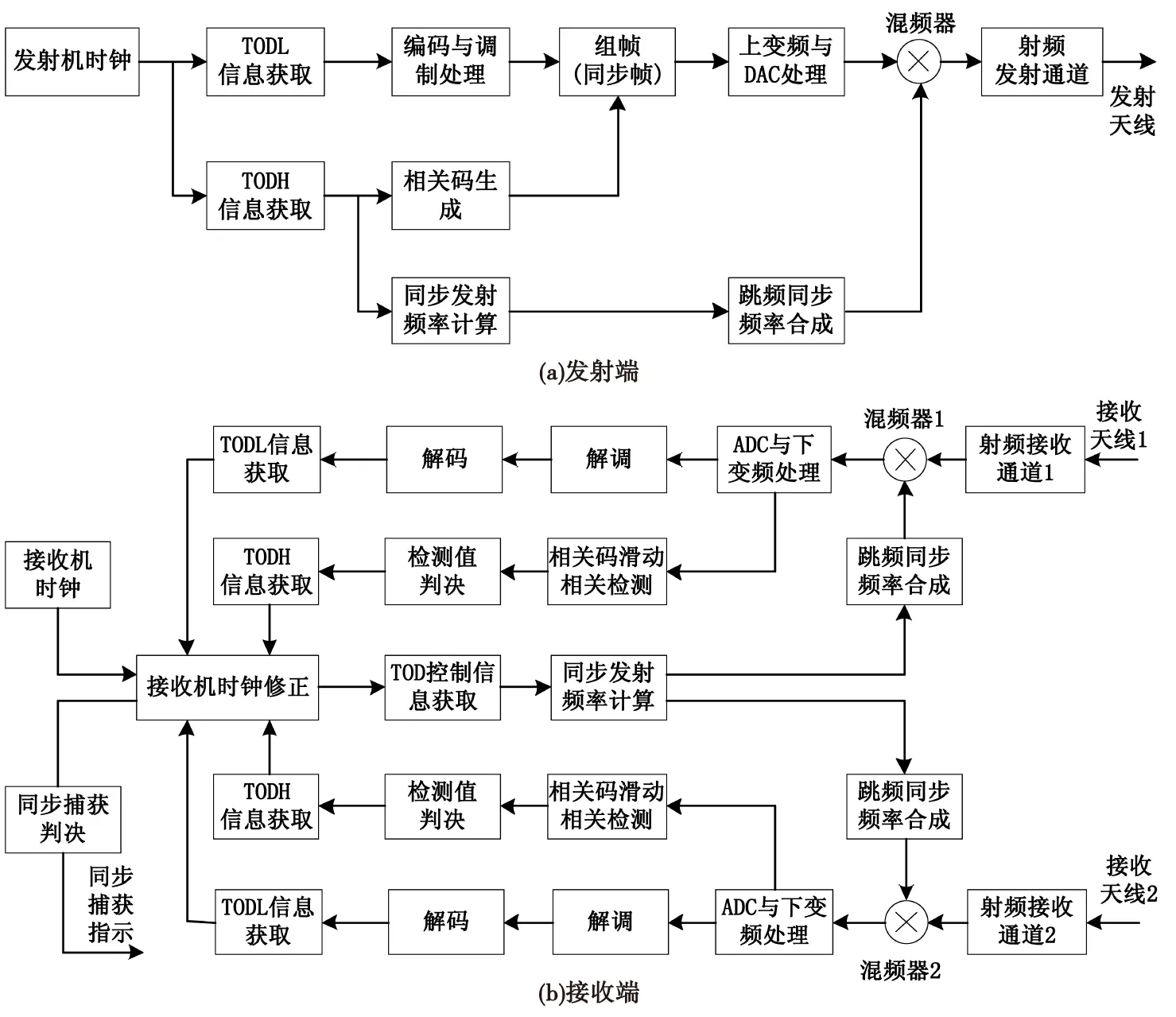

雙通道跳頻通信系統整體基于軟件無線電平臺進行設計與實現,其收發信機整體結構如圖1所示。發射機由信源接口單元、數字處理單元、數模轉換器(DAC)、射頻單元構成。接收機主要由信宿接口單元、數字處理單元和2個接收通道組成,每個接收通道由1個模數轉換器(ADC)和1個射頻單元構成。

其中,發射機從信源接口單元獲得待發送數據,送至數字處理單元,進行CRC編碼、信道編碼、交織、調制、組幀、上變頻等處理,同時信號處理單元完成跳頻頻表單元產生頻率控制字,由發射機頻率合成單元生成載波頻率,與經過ADC轉換的已調待發送信號進行混頻,進而通過射頻發射通道上的濾波、放大等處理后送至天線。

圖1 雙通道跳頻通信系統結構框圖Fig.1 Dual channel frequency hopping communication system structure

接收機的射頻接收通道1和射頻接收通道2同時從天線上獲取接收信號,分別與頻率合成1、頻率合成2進行混頻,然后分別經過ADC1、ADC2后送至數字處理單元,數字處理單元將2路接收信號進行下變頻、頻偏糾正、定時/抽樣、解調后進行綜合判決,將解調后的信號進行信道譯碼、CRC校驗等處理,最后送至信宿接口單元,其中,跳頻同步控制單元負責跳頻同步過程的控制,與接收信號混頻的本振信號受控于本地跳頻頻表單元生成的頻率控制字。

2 雙通道接收的跳頻同步捕獲方法

2.1 總體方案

同步字頭法中,發送端根據本地時鐘計算出同步頻率,在該頻率上發送同步信息,接收端用同樣的方法計算同步頻率進行慢搜索,捕獲發送端的同步信息并利用該信息實現跳頻同步。

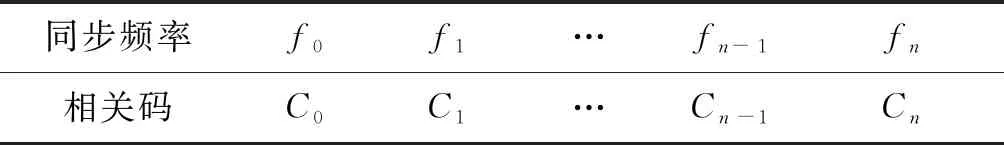

基于雙通道接收的同步字法中,發射端發出調制有TOD信息的同步信號,接收端在兩個獨立的接收通道上,同時對同步信息進行捕獲,之后再進行解調獲得發射端的TOD信息,然后對本地的時鐘進行修正,進而實現跳頻系統的同步。基于雙通道接收的跳頻同步捕獲原理圖如圖2所示。

傳統同步字頭法中,同步頻率是固定的,為了提高同步頭的抗偵察性,在本文所述的方法中,將同步字頭法和TOD信息相結合,使同步頻率隨著TOD的改變而改變。

從圖2中可以看出,在發射端,發射機時鐘信息的低位部分(TODL)作為待發送TOD信息,經過編碼、調制后,與由發射機時鐘信息高位部分(TODH)作為控制信息確定的相關碼進行組幀,經過上變頻、DAC轉換后,送入混頻器進行混頻,最后經過射頻發射通道后,由發射天線發射出去。跳頻同步的頻率由TOD控制信息確定,經過同步發射頻率計算單元生成頻率控制字,跳頻同步頻率合成單元生成跳變載波信號。

圖2 雙通道跳頻通信系統同步捕獲總體方案Fig.2 Synchronization scheme of dual channel hopping communication system

接收端主要由2個同步信息獲取通道,1個同步頻率合成通道和同步捕獲判決單元構成。每個同步信息獲取通道由射頻接收通道、混頻器、ADC與下變頻處理單元、解調單元、解碼單元、TODL信息獲取單元、相關碼滑動相關檢測單元、檢測值判決單元、TODH信息獲取單元構成。其中,相關碼滑動相關檢測單元和檢測值判決單元用于檢測同步幀中的相關碼,進而確定TODH信息。解調單元和解碼單元用于提取同步幀中的TODL信息。

在同步頻率合成通道中,利用同步信息獲取通道獲取的TODL信息和TODH信息對接收機時鐘進行修正,然后基于TOD控制信息計算同步發射頻率,兩個同步信息獲取通道的跳頻同步頻率合理分配。

同步捕獲判決單元通過對接收機時鐘修正值大小判決,輸出同步捕獲指示。

2.2 同步字頭信息設計

2.2.1 同步字頭信息定義與作用

跳頻同步中的同步字頭信息就是跳頻圖案實時時鐘信息。實時時鐘信息包括年、月、日、時、分、秒、毫秒、微秒等。通過讀取本地時鐘可以獲得本端TOD信息,其精度亦由本地時鐘決定,可精確到毫秒甚至微秒級。在基于TOD的同步字頭法中,TOD信息與跳頻序列的計算密切相關,在整個通信過程中起著至關重要的作用。

在基于TOD的同步字頭法中,同步頻率與通信頻率(用于傳送除同步信息以外的數據信息的頻率)均由TOD、原始密鑰、網號經過非線性運算而決定。為了保證當收發雙方時鐘存在一定差異的情況下,仍可實現同步,將TOD信息中的高位信息提取出來作為TOD高段(TODH),比如分鐘及其高位信息,系統根據TODH而不是全部的TOD信息來計算同步頻率,由此可保證,當收發雙方時鐘存在一定差異的情況下仍存在相同的同步頻率。為了提高同步的可靠性,通常采用多個頻率作為一組同步頻率。在跳頻通信過程中,同步頻率隨著TOD不斷變化,每隔一定時間自動更換其中一個,這樣有利于增強同步的抗偵察和抗干擾能力。經過一段時間后,多個同步頻率就全部更換一遍。當然,不能一次同時更換所有的同步頻率,必須一個一個地更換,否則,會因為接收機與發射機之間存在的時間誤差使得接收機產生的多個同步頻率與發射機產生的多個同步頻率沒有一個是相同的,從而無法實現同步。一個一個地更換同步頻率,可確保接收機和發射機在同步的最大時差范圍內,接收機產生的同步頻率與發射機產生的同步頻率大部分相同,從而確保接收機能夠接收到初始同步信息。

2.2.2 TOD信息格式

本方案中完整TOD同步字頭包括高位TODH和低位TODL信息。TODH由年、月、日、時、分等信息構成,其中年用7位二進制數表示、月用4位表示、日用5位表示、時用5位表示、分用6位表示,TODH共27位。TODL由秒、毫秒、微秒組成,其中,秒用6位表示、毫秒用10位表示、微秒用8位表示,TODL共24位。

跳頻通信過程中,要求發射端與接收端的TODH信息一致,因此,利用TODH信息計算用于同步的跳頻頻率。在跳頻同步完成首,再利用TODL信息計算用于通信的跳頻頻率,增強跳頻通信的抗干擾性能。

2.3 同步幀格式設計

2.3.1 同步序列設計

同步字頭中除包含TOD信息外,還包含前導序列、幀同步信息和網號信息,其格式如表1所示。

表1 基于TOD的同步字頭法同步序列格式Tab.1 The synchronization sequence synchronization head based on TOD format

前導序列為一組相關性比較好的相關碼序列,其主要作用為完成接收端TODH的矯正,該組相關碼序列在同步頻率上循環發送,且與同步頻率一一對應。

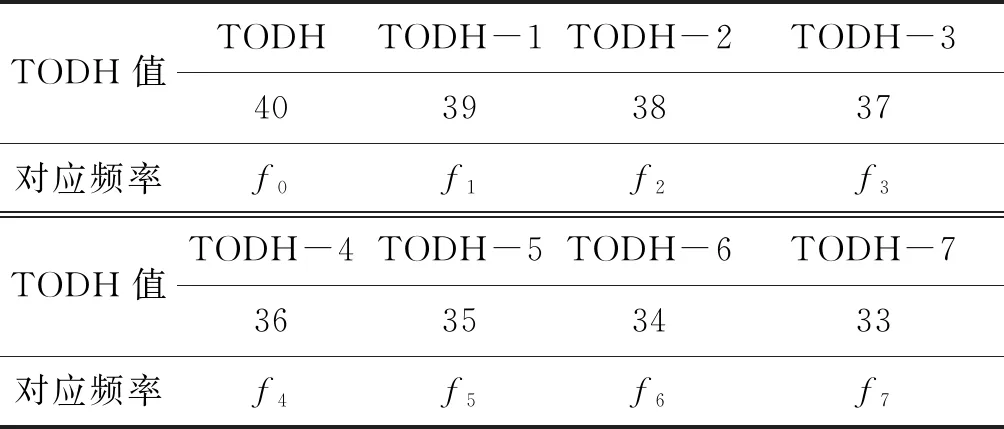

假設在跳頻通信系統中,同步頻率的個數為n,分別為f0,f1,f2,…,fn,則該組相關碼中共有N個碼序列,分別為C0,C1,C2,…,Cn,則其對應關系如表2所示,即在頻率fi上發送相關碼Ci。

表2 發送端同步頻率與相關碼序列對應關系Tab.2 The Correspondence between Synchronization Frequency of Sender and Related Code Sequence

幀同步序列同樣為相關性比較好的碼序列,標志著前導序列的結束,TODL信息的開始;TODL信息則用于對本地TODL信息的矯正,以使收發雙方的TOD信息相同;網號即組網信息。由于TODL信息和網號信息的重要性,一般要先對其進行編碼然后進行傳輸,以降低錯誤概率。

2.3.2 同步幀設計

本方案中的跳頻同步幀按照“一跳一幀”的思想設計,同步幀的生成過程如圖3所示。同步幀的生成過程具體描述如下:

1) 在每一跳中,待傳送的同步信息為48 bit,其中TODL信息占24 bit,組網等信息占24 bit;

2) 選擇8 bit CRC序列,CRC編碼后同步幀長度為56 bit;

3) 經過1/2卷積編碼后,幀長度為128 bit;

4) 采用隨機交織法進行交織編碼,編碼后幀長度仍為128 bit;

5) 采用QPSK調制,調制后幀長度變為64 symbol;

6) 在調制后的同步數據中插入2 symbol的引導,用于位同步,再在同步數據前加上64 symbol長的相關碼,同步幀長度變為130 symbol;

7) 在同步幀前加上8 symbol的功率控制字,再同步幀前后各加上11 symbol的換頻時間,一幀長度為160 symbol,按跳頻速率為200 hop/s計算,則符號速率為32 ksps。

圖3 跳頻同步幀設計與生成Fig.3 Design and generation of frequency hopping synchronized frames

2.4 捕獲控制方案設計

在基于TOD信息的同步字頭法中,當前跳頻頻率是由TOD、原始密鑰等信息決定的,其中,除TOD信息外,其他信息都是雙方事先約定的,唯一的不確定因素是TOD信息,因此在同步字頭法中,跳頻同步即為收發雙方TOD的同步。

在該方法中,發送端首先在同步頻率發送同步序列,接收端根據該同步序列矯正本地TOD,從而實現同步。按照跳頻通信系統設計,初始同步時間不得超過0.6 s。在同步字頭法中,初始同步時間即為同步頭占用的時間,因此,同步頭時間應小于0.6 s。

本方案中跳頻速率為200 hop/s,同步頻率共有8個,允許收發兩端最大時間差為8 min。

在同步開始時,發送方首先讀取本地系統時鐘,計算出TODH,然后根據TODH-i(i=0,1,2,…,7)計算出同步頻率fi。隨著時間的進行,TODH每改變一次,其中的一個同步頻率就會被替換掉。

本方案中我們采用雙通道的接收,即接收端讀取系統的時鐘得TODH后,計算出兩組同步頻率,第一組根據TODH-j(j=0,1,2,3)計算出同步頻率fj,第二組根據TODH-j(j=4,5,6,7)計算出同步頻率fj,接收端在這兩組同步頻率上同時進行慢掃描,掃描速率是發射端跳頻速率的1/9,當接收端在同步頻率fj上檢測到相關碼序列Ck時,系統則根據兩者索引的差值調整本地TODH,即:

TODH′R=TODHR+k-j

(1)

式(1)中,TODH′R為接收端調整之后的TODH,TODHR為調整之前的TODH。

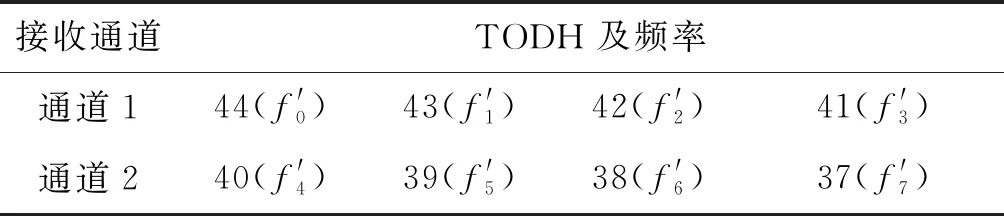

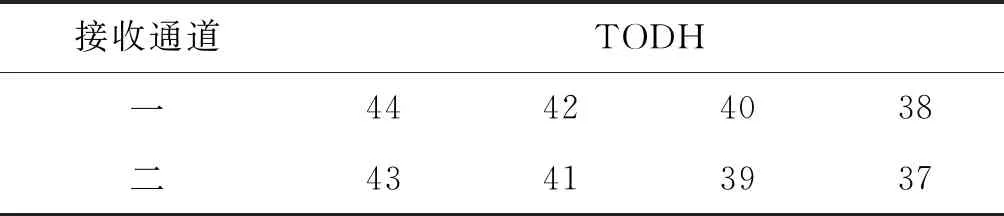

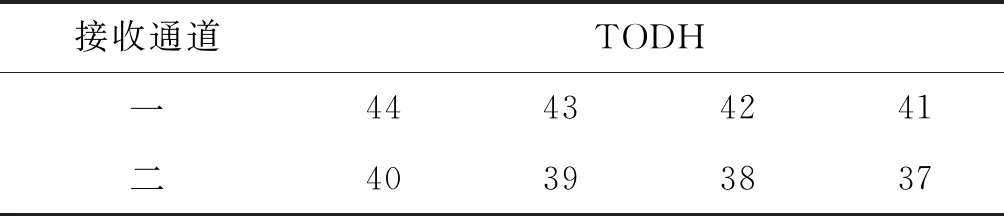

例如,若某一時刻時發射端TODH為40,則此時發射端的TODH和頻率計算實例如表3所示。

表3 發射端TODH及頻率計算實例Tab.3 The transmitter TODH and frequency calculation example

假設接收端此時刻的TODH=44,則此時接收端的TODH和計算的頻率計算實例如表4所示。

接收端調整TODH之后,重新計算同步頻率,然后進行同步跟跳,進入同步確認階段,即若在接下來的K跳中連續收到L個相關碼,且這些相關碼與接收端的跳頻頻率一一對應,則認為同步捕獲成功,否則捕獲失敗,返回到掃描狀態繼續掃描。

表4 接收端TODH及頻率計算實例Tab.4 The receiver TODH and the frequency calculation Example

捕獲成功后,接收端檢測幀同步序列,接收其后的TODL信息和網號,并利用接收到的TODL信息對本地TODL信息進行校正,使之與發送端相同。至此,接收端的TODH與TODL均與發送端相同,系統完成了收發雙方的跳頻同步。

3 跳頻同步捕獲仿真與性能分析

3.1 仿真與分析

采用Matlab/Simulink對跳頻同步捕獲鏈路進行仿真,仿真頻率范圍在30~88 MHz,跳頻的速率為200 hop/s,一張頻表包含256個頻點,信道間隔為25 kHz。

3.1.1 仿真鏈路設計

1) 發射鏈路設計

發射端仿真鏈路如圖4所示,發射端主要包括:時鐘模塊(send_clocker)、頻率合成模塊(FH_Pattern_send)、TOD信息發送模塊(TOD_send)、數字上變頻模塊(DUC)、混頻模塊(Mix_UP)、信道模塊(AWGN Channel)。下面將對其進行介紹。

本地時鐘模塊的主要功能是模擬產生發射機本地時鐘及時間,由觸發模塊產生觸發信號。因項目所采用的軟件無線電平臺數字處理單元時鐘為10 MHz,因此本地時鐘計數10次為1 us,us信號觸發1 000次為1 ms,ms信號觸發1 000次為1 s,s信號觸發60次為1 min,min信號觸發60次為1 h,h信號觸發24次為1 day,day信號觸發30次為1 month,month信號觸發12次為1 year,用計算器進行相應的計數觸發進位,進而產生相應的時間信息。

圖4 發射端仿真鏈路Fig.4 Transmitter simulation link

TOD信息發送模塊用于對待發送的TODL、組網等信息進行CRC編碼、信道編碼、交織編碼、調制、上變頻等處理,然后將其混頻并到同步頻率上發送出去。

頻率合成模塊的主要功能是生成發射載波所用的信號,在同步字頭法中,發送端發送的信息分為兩種:數據信息和同步信息。發送端在發送這兩種信息時采用不同的頻率。同步頻率計算模塊的作用為根據本地時鐘的TODH信息計算產生用于發送同步信息的同步頻率。在仿真中,首先讀取本地的時鐘并根據轉換規則得到TODH信息,然后利用(TODH-i)計算出同步頻率fi(i=0,1,2,…,7),進行同步信息的捕獲。數據頻率計算模塊的作用為根據TOD信息計算產生用于發送數據信息的頻率,該模塊首先根據轉換的方法得到TODL信息,然后在根據計算方法計算得到用于發送數據的頻率。

此外,數字上變頻模塊完成待發送TOD信號的48倍上變頻。混頻模塊完成已調整TOD信號與載波頻率的混頻。信道模塊采用高斯白噪聲(AWGN)信道模型,仿真中設置信噪比為10 dB。

2) 接收鏈路設計

接收端的仿真鏈路如圖5所示,該鏈路主要由接收端時鐘模塊(receiver_clocker)和兩個同步捕獲通道組成。兩個同步捕獲通道并行接收,進行同步捕獲。每一路同步捕獲通道由同步頻率合成模塊(syn_FH_Pattern_0、syn_FH_Pattern_1)、數據頻率合成模塊(data_FH_Pattern_0、data_FH_Pattern_1)、混頻模塊(Mix_Down_0、Mix_Down_1)、數字下變頻模塊(DDC_0、DDC_1)、TODH獲得模塊(get_TODH_0、get_TODH_1)、解調器模塊(demod_0、demod_1)、TODL獲得模塊(get_TODL_0、get_TODL_1)、同步捕獲標志模塊(syn_flag_0、syn_flag_1)。下面將對其中部分的模塊進行介紹。

同步頻率合成模塊在仿真剛開始的時候根據接收端時鐘轉換的TODH計算出同步頻率對發射端的同步信息進行同步捕獲,之后根據后面模塊對接收端時間的修正在進行計算接收端的同步頻率,直到最后實現與發射端的同步為止。

圖5 接收端的仿真鏈路Fig.5 Receiver simulation link

數據頻率合成模塊用于計算數據頻率,當實現同步捕獲后,接收端就會切換成此頻率進行發射端數據的接收,完成信息的傳遞。

混頻模塊在同步的過程中將接收端計算出來的同步頻率與發射端的同步頻率進行混頻,然后進行低通濾波把噪聲給濾除掉,保留有用的同步信息,進行之后的同步信息捕獲。

TODH獲得模塊用于獲得發射端的TODH,8路滑動相關模塊用于同步幀的獲得,之后進行一系列的計算得到分鐘的修正值,返回到之前同步頻率的計算當中去,在進行同步捕獲。

TODL獲得模塊接收到解調模塊解調的信息后,進行TODL的解算,并按照相應的方式計算出s,ms,μs的修正值,返回到之前進行數據頻率的計算。

同步捕獲標志模塊進行同步過程是否已經完成的判斷,仿真中設定,如果已同步幀的數量大于等于7,則其判斷值就會跳變為1,表示已達到同步的標準,該模塊的返回值還用于判斷選擇雙通道的通道進行信息的傳遞,即該通道的同步捕獲判斷值先變為1,完成同步捕獲。

3.1.2 仿真結果與分析

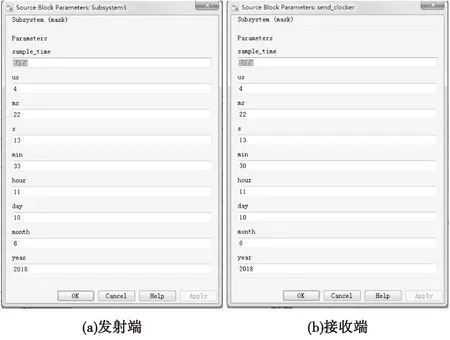

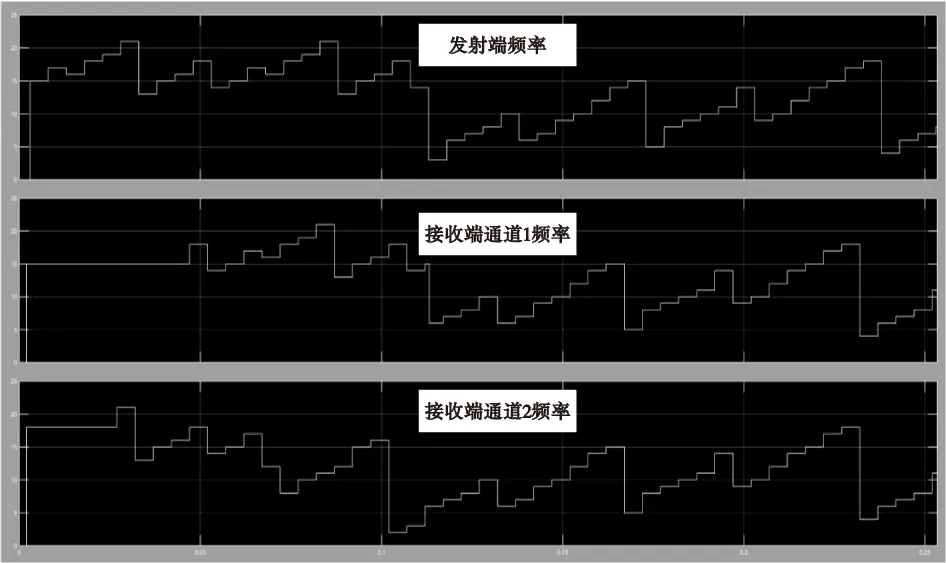

雙通道跳頻同步系統的參數設置如圖6所示。當發射端的時間為2018年6月10日11點30分13秒22毫秒4微秒,接收端的時間為2018年6月10日11點33分13秒22毫秒4微秒時。仿真結果圖如圖7所示,此圖中接收端通道1頻率相當于基于TOD信息單通道跳頻同步系統同步捕獲時的結果,接收端通道1和接收端通道2共同構成基于TOD信息雙通道跳頻同步系統同步捕獲時的結果。此圖中接收端通道2在0.025 s時實現同步,通道1在0.045 s時實現同步,通道2比通道1率先實現同步,這也說明雙通道跳頻系統同步捕獲方法較之單通道跳頻系統同步捕獲方法能夠減少同步捕獲的時間,上文中的理論分析在仿真中得到了印證。

圖6 發射端與接收端的時鐘Fig.6 Clocks at transmitter and receiver

圖7 仿真結果圖1Fig.7 Simulation results 1

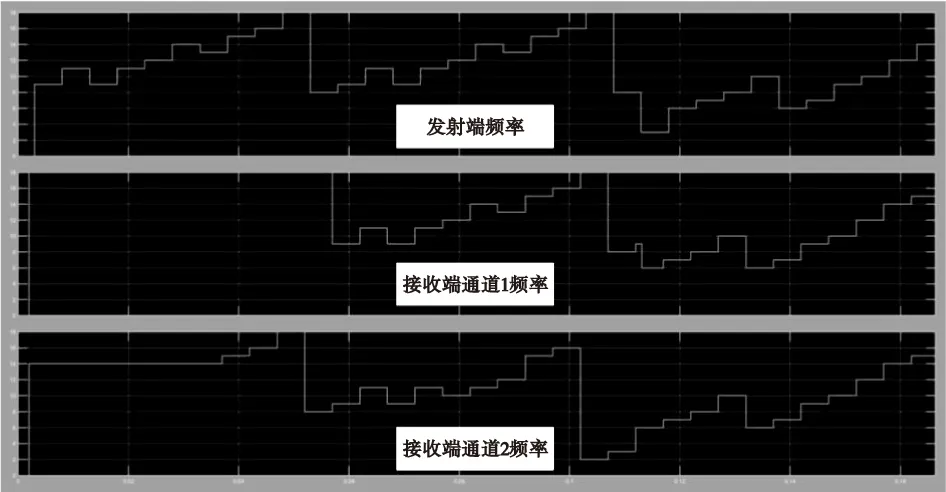

當發射端時間為2018年6月10日11點10分13秒22毫秒4微秒,接收端時間為2018年6月10日11點15分13秒22毫秒4微秒時,仿真結果如圖8所示。此圖中接收端通道2在0.037 s時實現同步,接收端通道1在0.062 s時實現同步,通道2比通道1率先實現同步這也能證明理論分析的結論。

圖8 仿真結果圖2Fig.8 Simulation results 2

3.2 同步性能分析

跳頻同步捕獲性能主要反映在同步時間和同步概率兩方面,下面具體分析。

3.2.1 同步時間

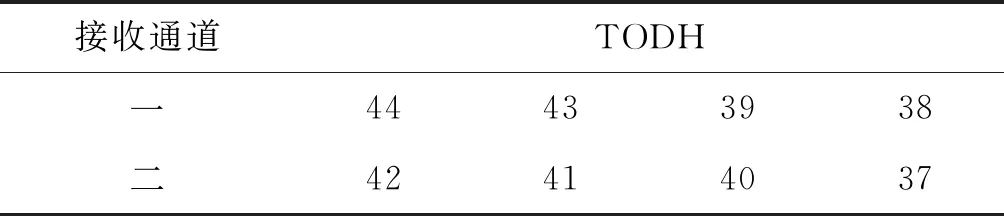

在跳頻同步字頭捕獲時,各通道的同步頻率分配可以有多種的方案,下面進行簡單的舉例分析。假設屬臺TODH為44,主臺TODH從44到37變化。比較屬臺的同步頻率分配的四種方案。

方案一 采用雙通道進行同步捕獲,屬臺頻率分配為等間隔(間隔為2)分配,具體分配方法見表5。

方案二 采用雙通道進行同步捕獲,屬臺頻率分配為等間隔(間隔為1)分配,具體分配方法見表6。

方案三 采用雙通道進行同步捕獲,屬臺頻率分配為隨機分配,具體分配方法見表7。

表5 雙通道接收屬臺同步頻率分配方案1Tab.5 Synchronous frequency allocation plan 1 for dual channel receiver

表6 雙通道接收屬臺同步頻率分配方案2Tab.6 Synchronous frequency allocation plan 1 for dual channel receiver

表7 雙通道接收屬臺同步頻率分配方案3Tab.7 Synchronous frequency allocation plan 3 for dual channel receiver

方案四 采用單通道進行同步捕獲,屬臺頻率分配為等間隔(間隔為1)分配,具體分配方法見表8。

表8 單通道接收屬臺同步頻率Tab.8 Synchronous frequency allocation plan for single channel receiver

在理想條件下,不考慮信道干擾,計算不同方案下各種情況的同步所需跳數如表9所示。

表9 不同方案下各種情況同步所需跳數Tab.9 Hops required for synchronization in different scenarios

各種情況的屬臺同步時跳的次數的期望值如下:

E1=((1+1+2+2+3+3+4+4)×9)/8=22.5

E2=((1+2+3+4+1+2+3+4)×9)/8=22.5

E3=((1+2+1+2+3+3+4+4)×9)/8=22.5

E4=((1+2+3+4+5+6+7+8)×9)/8=40.5

按照跳頻速率為200 hop/s計算,在采用雙通道接收時,方案一、方案二、方案三的同步時間統計平均值均為112.5 ms,采用單通道接收的方案四同步時間統計平均值均為202.5 ms。

由以上分析可知,雙通道同步字頭捕獲方案比單通道同步捕獲方案能夠縮短大概一半的同步時間,且雙通道同步字頭捕獲各通道的同步頻率分配對同步的時間沒有影響。本文中采用方案二的雙通道同步捕獲方案。

3.2.2 捕獲概率

1) 相關碼檢測概率計算

相關碼用于完成接收端TODH的糾正,又稱前導序列。該組相關碼序列在同步頻率上循環發送,且與同步頻率一一對應。相關碼由Walsh碼與偽隨機序列異或構成。

假設相關碼的長度為M,相關碼的檢測門限設為m,只要M個比特中傳輸正確的比特數等于或者大于m個,接收方就可以正確檢測到相關碼。設傳輸信道的誤比特率為Pb,則相關碼的正確檢測概率Pt為:

(2)

本方案中相關碼長度M=64,m=56,信道的誤比特率為Pb=0.1,將其代入式(2),計算可得相關碼的正確檢測概率Pt=0.813 4=81.34%。

2) 捕獲概率計算

發送端在發送同步信息時,接收端能夠捕獲到同步信息并與發送端建立起同步的概率稱為捕獲概率。

假設初始同步信息幀中的相關序列有N1跳,同步頭頻率有N2個,即同步頭頻率循環一次需要N2跳。因為捕獲到相關碼以后,還需要進行同步確認,至少需要N2跳,則可用來捕獲的相關序列只有N1-N2跳。每跳捕獲到相關碼的概率相等,則在這N1-N2跳中捕獲到相關碼的概率Ps為:

(3)

捕獲到相關碼以后,需要進行同步確認,同步確認采用大數判決方式進行,假設同步確認的跳數為K,如果有超過K/2的跳數捕獲到相關碼,則認為同步成功,同步確認成功的概率Pc為:

(4)

由概率的獨立性可知,得到捕獲概率為Pd=Ps×Pc。

由式(3)得在相關碼的正確檢測概率Pt一定時,用于相關捕獲的跳越多,捕獲到相關碼的概率Ps就越大。由式(4)得相關碼的正確檢測概率Pt一定時,同步確認的跳數為K越小,同步確認成功的概率Pc就越大,但此時出現錯判的概率較大;同步確認的跳數為K越大,同步確認成功的概率Pc就越小,但此時出現錯判的概率較小,所以應該合理的設置K的值。

本方案中N1=72,N2=8,可用來捕獲的相關序列有64跳,根據上文計算出來的相關碼正確檢測概率Pt=81.34%,將其代入式(3),計算可得,捕獲到相關碼概率Ps=1。

本方案中K=8,將K、Pt,代入式(4),計算可得,同步確認成功的概率Pc=0.992 3=99.23%。

由Pd=Ps×Pc式,可計算出Pd=99.23%。即捕獲概率為99.23%,符合規定的要求。

4 結論

本文提出了一種雙通道跳頻通信系統同步捕獲方法。該方法將同步字頭法與并行捕獲相結合,利用同步過程中的載波頻率與被調制時間信息共同確定頻率跳變時間,在兩個接收通道上進行并行捕獲,縮短同步時間,提高同步的隱蔽性和抗干擾能力。仿真結果表明,相比單通道捕獲,所提出的雙通道同步捕獲方法在捕獲概率基本不變的情況下,初始同步時間縮短為原來的1/2,且有效利用了接收機資源,對于具有多通道的跳頻通信系統同步捕獲具有一定參考價值。