DSP+FPGA的串行通信在PWM中的應(yīng)用

左兆文

摘要:隨著電力電子技術(shù)的發(fā)展,單DSP已經(jīng)無法滿足例如MMC拓?fù)浣Y(jié)構(gòu)的開關(guān)管控制。故DSP+FPGA的控制器結(jié)構(gòu)成為了研究熱點。本文主要介紹了DSP和FPGA的串行通信方法,DSP發(fā)揮其數(shù)字處理的優(yōu)勢計算開關(guān)管的占空比,而FPGA完成占空比移相的功能。其中,串行通信方法利用DSP的GPIOA作為I/O口發(fā)送數(shù)據(jù)。文中給出了串行通信軟件實現(xiàn)的流程圖,并對FPGA通信程序進(jìn)行了仿真。通過仿真以及實驗,驗證了串行通信方法的可行性。

關(guān)鍵詞:DSP;FPGA;串行通信

在電力電子領(lǐng)域中,一般情況下DSP都作為核心控制器,負(fù)責(zé)整個系統(tǒng)的正常運行[1]。但是DSP在要求高可靠性的電路驅(qū)動方面卻不如將驅(qū)動算法以電路邏輯方式固化的現(xiàn)場可編程門陣列(FPGA)[2];同時DSP的輸出功能引腳數(shù)量一定,在一個需求多路PWM驅(qū)動的系統(tǒng)中,DSP無法獨立完成系統(tǒng)的控制[3]。而FPGA的I/O口數(shù)量眾多,極大的擴(kuò)展了PWM輸出的數(shù)量。因此,利用DSP+FPGA作為核心控制器成為發(fā)展趨勢[4]。

一、串行通信的軟件設(shè)計

本文使用TI公司的TMS320F2812芯片,實現(xiàn)其與FPGA之間的串行通信。由于控制精度的要求,DSP每次發(fā)送的數(shù)據(jù)都為16位二進(jìn)制數(shù)。在串行通信中,DSP每2us發(fā)送16位數(shù)中的一位數(shù)據(jù)送至FPGA,并等待18usFPGA讀數(shù)據(jù),即50us發(fā)送一個16位二進(jìn)制數(shù)。

(一)硬件設(shè)計

TI公司的TMS320F2812DSP芯片晶振為30MHZ,最大倍頻150MHZ,且有56 個可編程通用輸入/輸出引腳,其中GPIOA和GPIOB可以設(shè)置為PWM輸出引腳。由于DSP需要串行發(fā)送數(shù)據(jù)到FPGA,所需引腳數(shù)量較少,因此選擇GPIOA6-15與FPGA的輸入輸出(I/O)引腳相連接。

(二)軟件實現(xiàn)

核心控制板中,用于串行發(fā)送數(shù)據(jù)的是GPIOA。所以,串行發(fā)送的時基是使用2812EVA中的T1定時器,中斷也為T1定時器中斷。T1定時器設(shè)計為每2us產(chǎn)生一次中斷,并訪問中斷子程序,開始發(fā)送數(shù)據(jù)。當(dāng)?shù)谝粋€16位的數(shù)據(jù)發(fā)送結(jié)束以后,定時器繼續(xù)計時,但并不發(fā)送數(shù)據(jù),等待FPGA讀取數(shù)據(jù)。由于EVA中的計數(shù)模式設(shè)置為遞增模式。

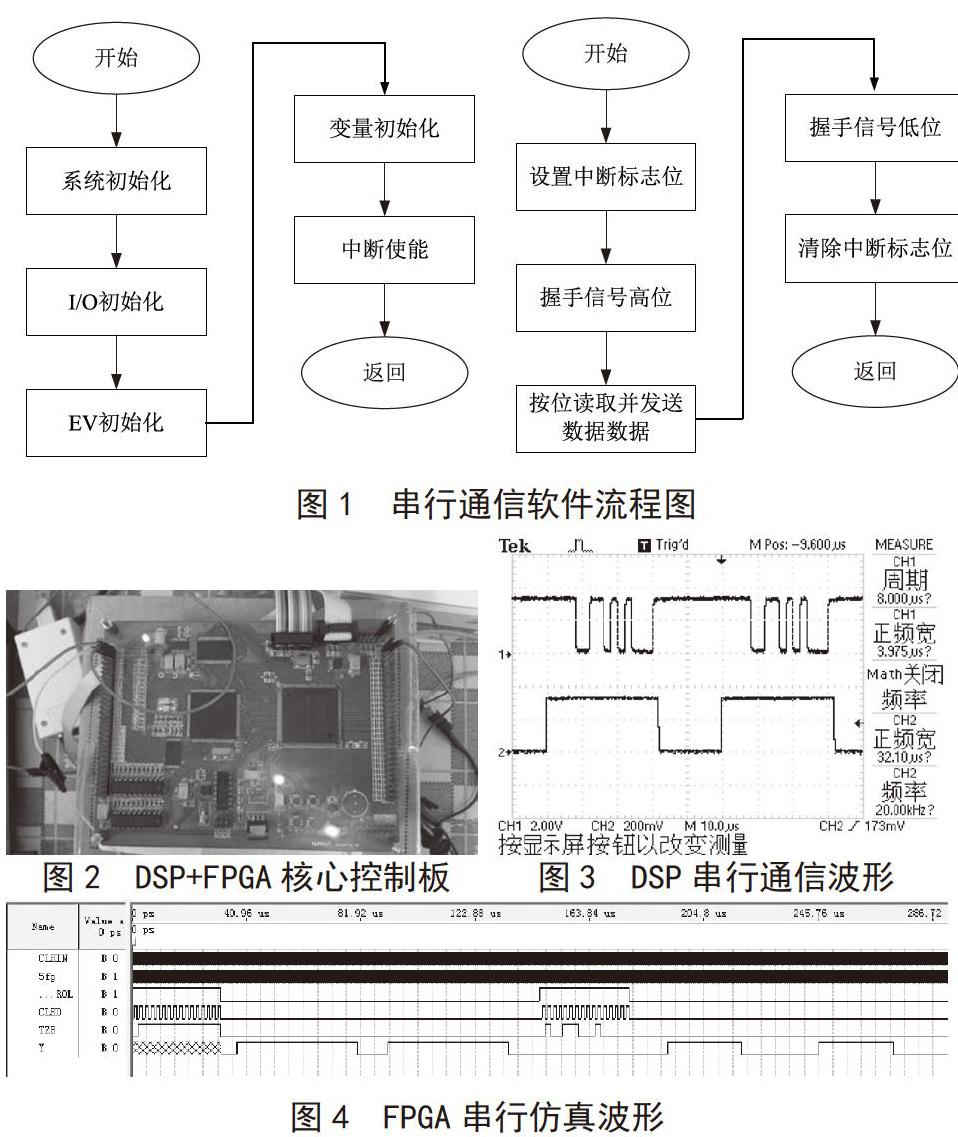

在SPWM調(diào)試中,調(diào)制波為50HZ正弦波,設(shè)計PWM頻率為20kHZ,因此在一個調(diào)制波周期需要發(fā)送400個16為數(shù)據(jù)每0.9°選取一個點,將正弦波數(shù)組定義為a[i](i=1,2…,400),當(dāng)下一個周期正弦波到來時,該數(shù)字又重新開始計數(shù)。即在20ms內(nèi)發(fā)送400個數(shù)據(jù)送至FPGA,因此每一個數(shù)據(jù)發(fā)送周期為50us,而每個數(shù)據(jù)為16位,所以每一位數(shù)據(jù)發(fā)送時間為2us,等待時間為18us。同時,F(xiàn)PGA需要一個握手信號表示DSP開始發(fā)送數(shù)據(jù)。所以,選定GPIOA7為握手信號發(fā)送的I/O口,GPIOA8為數(shù)據(jù)發(fā)送口。GPIOA7在0~32us內(nèi)為高電平表示DSP正在向FPGA發(fā)送數(shù)據(jù),在32~50us內(nèi)為低電平表示停止發(fā)送數(shù)據(jù),同時FPGA開始讀取數(shù)據(jù)。軟件流程圖見圖1。

在FPGA收到DSP發(fā)送的數(shù)據(jù)信號和握手信號以后,F(xiàn)PGA開始工作。當(dāng)控制信號高位時,F(xiàn)PGA晶振100分頻產(chǎn)生一個時鐘信號,目的是為了每2us讀取一次DSP發(fā)送的調(diào)制波信號。在讀取數(shù)據(jù)時,F(xiàn)PGA還進(jìn)行了串行轉(zhuǎn)并行的操作。當(dāng)控制信號低位時,調(diào)制波信息保持不變,繼續(xù)產(chǎn)生PWM信號。FPGA通過晶振的分頻操作,產(chǎn)生了三角波,接收的調(diào)制波與三角波進(jìn)行比較操作,最終產(chǎn)生PWM信號。

二、仿真及實驗結(jié)果

為了驗證上述理論的正確性,本文進(jìn)行了FPGA的仿真實驗和DSP+FPGA實際操作。核心控制板如圖2所示。

本文首先驗證了DSP在串行通信中軟件程序的正確性。由于DSP發(fā)送調(diào)制波信息以及控制信號,所以DSP發(fā)送波形如圖3所示。通道1顯示的是調(diào)制波信息,從左至右為一個數(shù)據(jù)的低位到高位。通道2顯示的是DSP發(fā)送至FPGA的控制信息,即握手信號。

圖4中顯示的是FPGA的仿真波形,CLKIN位FPGA的晶振頻率,CLK0為FPGA的時鐘信號,TZB為調(diào)制波,輸出Y為PWM波形。

三、結(jié)論

本文主要介紹了DSP+FPGA的串行通信方法,并利用PWM調(diào)試驗證了通信算法的可行性。串行通信采用GPIO引腳實現(xiàn)。大多的電力電子系統(tǒng)要求的開關(guān)的頻率為20kHZ以內(nèi),且需要多路調(diào)制波信號發(fā)送至FPGA。因此結(jié)合工程實際,為了節(jié)省通信引腳,系統(tǒng)控制策略選擇串行發(fā)送。最后經(jīng)過仿真和實驗的驗證,證明了串行通信方法的正確性。

參考文獻(xiàn):

[1]2016世界能源發(fā)展報告[R].北京:社會科學(xué)文獻(xiàn)出版社,2016.7-10

[2]魏一鳴.中國能源報告[M].科學(xué)出版社,2014:2-8

[3]曾正,趙榮祥,湯勝清等.可再生能源分散接入用先進(jìn)并網(wǎng)逆變器研究綜述[J].中國電機(jī)工程學(xué)報,2013 (24):1-12.

[4]聶華,劉開華,孫春光等.DSP和FPGA之間串口通信研究[J].電子測量技術(shù),2006,29 (6):112-114.