動車組WTBC編解碼器設計

劉晨曦, 杜振環, 王 鋒

(中車大連電力牽引研發中心有限公司, 遼寧大連 116052)

國內某型動車組,單列車拓撲可分為“動力車+8輛拖車+控制車”短編組的動車組或“動力車+16輛拖車+動力車”長編組的動車組,配置十分靈活。不同廠家的控制車、動力車通過重聯網關互聯互通。

FPGA(現場可編程門陣列)作為 ASIC(Application Specific Integrated Circuit)領域中的一種半定制電路,解決了定制電路的不足,可以實現多種邏輯功能。WTB幀數據是曼徹斯特碼,它是一種常用的基帶信號編碼。IEC61375[1]規定,列車間WTB通信數據以曼徹斯特碼傳輸,實現列車間的互操作。

1 WTB幀

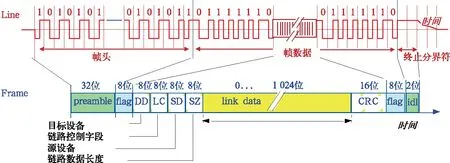

絞線式列車總線WTB(wire train bus)幀格式如圖1所示,包括幀頭(文中研究32 bits幀頭)、幀數據、和幀尾(終止分界符)。

(1)幀頭:即前導碼preamble,由高電平“1”起始,接著若干個‘0’‘1’對(文中為15對)并以“1”結束,用于WTB幀數據同步;

(2)幀數據:標準HDLC數據;

(3)幀尾:兩個時間單位寬度的高電平。

圖1 WTB幀

2 硬件測試平臺

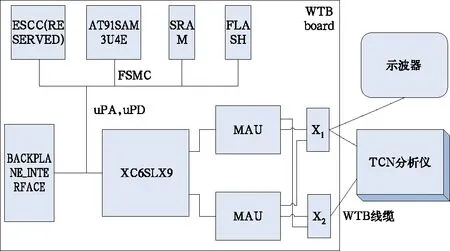

硬件測試平臺如圖2所示(X1和X2為DB9對外連接器),用于測試WTB編解碼器。ARM處理器AT91SAM3U4E,主頻96 MHz,內存256 kB,SRAM是52 kB。FPGA是XILINX公司的Spartan-6系列芯片,型號XC6SLX9,用來實現WTBC編解碼器。用WTB線纜把TCN分析儀串聯在發送通道與接收通道之間。

ARM處理器通過可變靜態存儲控制器FSMC接口訪問配置FPGA,通過WTB鏈路層接口從應用層控制WTB數據發送和接收。初始化成功后,在WTB通信板卡X1接口定時發送變化的WTB幀數據,通過TCN分析儀在接口X2接收,應用層軟件對接收數據進行統計,可判斷接收數據與期望是否相符。對于不同類型請求/響應幀數據(包括狀態請求/狀態響應幀、檢測請求/檢測響應幀、命名請求/命名響應幀、存在請求/存在響應幀等),通過TCN分析儀進行數據統計和分析,達到測試WTB編解碼器的目的。

圖2 硬件測試平臺

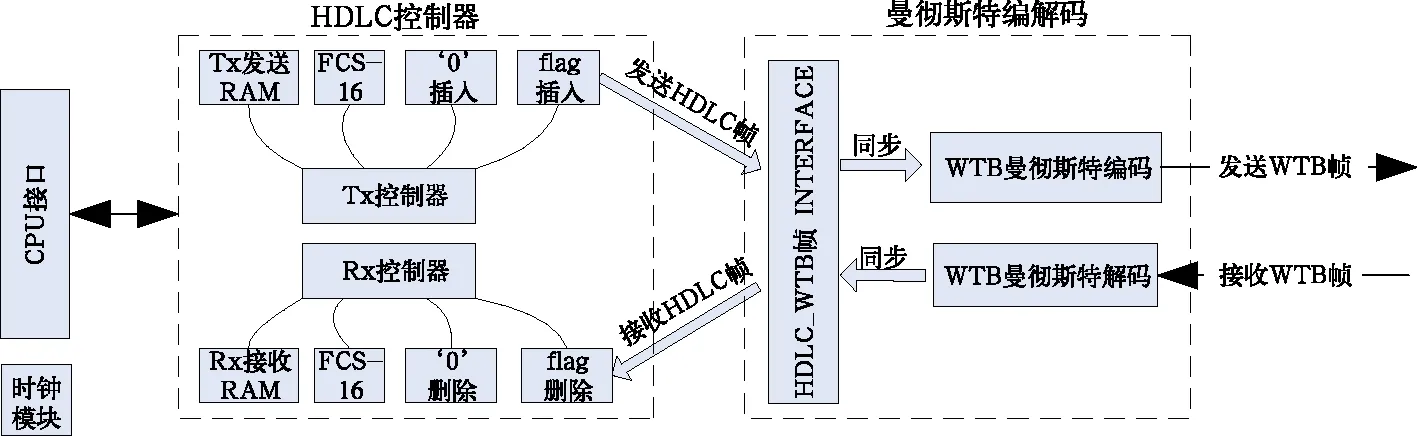

3 WTBC編解碼器

WTBC編解碼器核心是編碼器和解碼器。編碼是完成WTB數據編碼并進行CRC校驗;解碼是實現接收波形的位同步和數據解析,如果計算的CRC與接收到的CRC結果不符,則放棄此幀數據。其原理如圖3所示。主要分為以下幾個部分:CPU接口模塊,HDLC控制器模塊及曼徹斯特編解碼模塊。

圖3 WTBC編解碼器

(1)CPU接口模塊

CPU接口模塊包括數據線(uPD)、地址線(uPA)、寫(uPWR#)、讀(uPRD#)、片選(uPESCCCS#)、中斷(ESCC_INT#)等信號(如圖4所示)。CPU接口模塊作為WTB編解碼器與外部處理器CPU的接口,是WTB編解碼器與CPU的數據傳輸通道,CPU通過訪問編碼器和解碼器的內部寄存器,控制WTB數據發送接收。

圖4 WTBC編解碼器CPU接口信號示意圖

(2)HDLC控制器模塊

HDLC數據是串行數據幀格式,與時序邏輯緊密聯系,包括HDLC發送控制器和HDLC接收控制器。

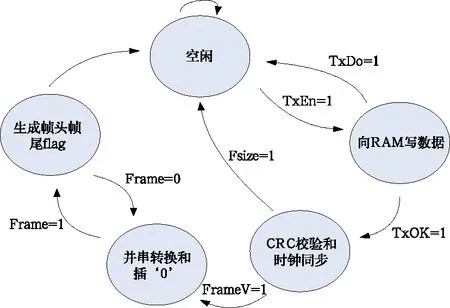

①HDLC發送控制器。即HDLC編碼器,是功能和時序復雜的時序邏輯電路,可抽象成有限狀態機。其狀態轉換與數據處理包括HDLC數據的0比特插入,CRC校驗等都可以按照ISO 3309標準實現。根據HDLC編碼協議,得到HDLC編碼器有限狀態機:CPU發送數據時首先要讀取發送寄存器狀態,當TxDo=1時,HDLC控制器緩存CPU發送的數據到RAM中,CPU發送完一包數據后向發送寄存器寫入TxEN=1命令。發送緩存接收到TxEN=1指令后跳轉至read狀態,TxOK=1;緩存的數據經CRC校驗和時鐘同步后,再把并行數據轉換成串行數據,同時檢驗每位數據信息,即串行數據出現連續5個‘1’時在其后插入1個‘0’;并行數據轉換串行數據的起始生成幀頭flag,轉換完成生成幀尾flag。HDLC發送控制器狀態轉換如圖5所示。

圖5 HDLC發送控制器狀態機

②HDLC接收控制器。即HDLC解碼器,和編碼器一樣是時序邏輯電路,同樣可抽象成有限狀態機,包括幀頭幀數據檢測、CRC校驗、0比特刪除等部分。HDLC接收是發送的逆過程,需要對接收的每一個數據位進行判斷。HDLC接收模塊檢測總線上的數據,當識別到“01111110”即flag,則FlagDetect=1,并進行串行數據到并行數據轉換,與此同時執行0比特刪除操作,即檢測到連續5個‘1’則自動將其后面的‘0’刪除;再經過時鐘同步和CRC校驗,當WR=1時向雙口RAM寫入1個字節的數據,當數據長度大于等于31字節產生FULL中斷,CPU從RAM讀取31個字節數據并把CPU_ACK置1,直到產生EOF幀尾中斷(若幀長度小于31字節則只產生幀尾中斷),CPU從RAM讀取剩余數據并把CPU_ACK再置1,狀態機恢復到空閑。HDLC接收控制器狀態轉換如圖6所示。

圖6 HDLC接收控制器狀態機

(3)曼徹斯特編解碼模塊

曼徹斯特編解碼模塊具有同步HDLC幀與WTB幀,和對數據進行曼徹斯特編碼和解碼。幀同步是通過程序中的移位寄存器暫時存放HDLC數據并與WTB曼徹斯特編碼模塊進行信號交互來實現。幀同步的狀態轉換如圖7所示。曼徹斯特編碼模塊生成WTB幀32 bits幀頭、2 bits終止分界符,及HDLC數據的曼徹斯特編碼;曼徹斯特解碼模塊用來識別WTB幀頭幀尾并將其刪除,同時對數據進行曼徹斯特解碼。

圖7 幀同步狀態機

4 設計實現

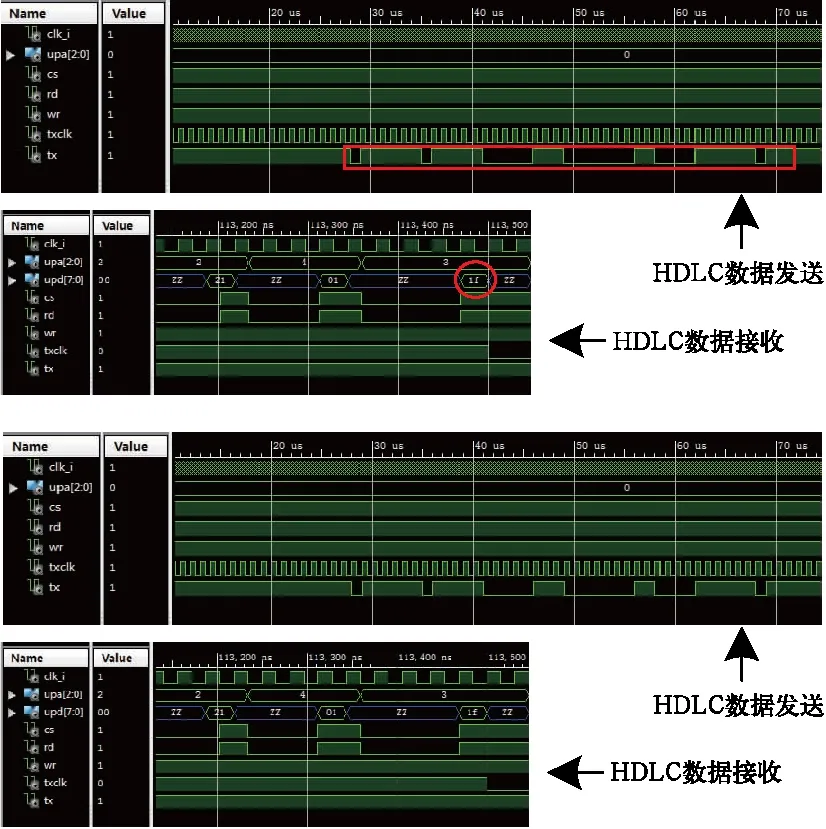

根據上面所描述的方法,采用自頂向下的設計理念,使用VHDL硬件描述語言和ISE14.7開發工具,仿真綜合實現并下載到FPGA芯片(FPGA仿真如圖8所示,從圖中可以看出,CPU發送數據為0x1f,接收數據為0x1f,接收與發送數據相同),使用ChipScope軟件監測波形如圖9所示。

圖8 功能仿真

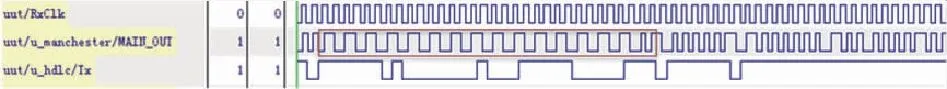

圖9 WTB幀波形

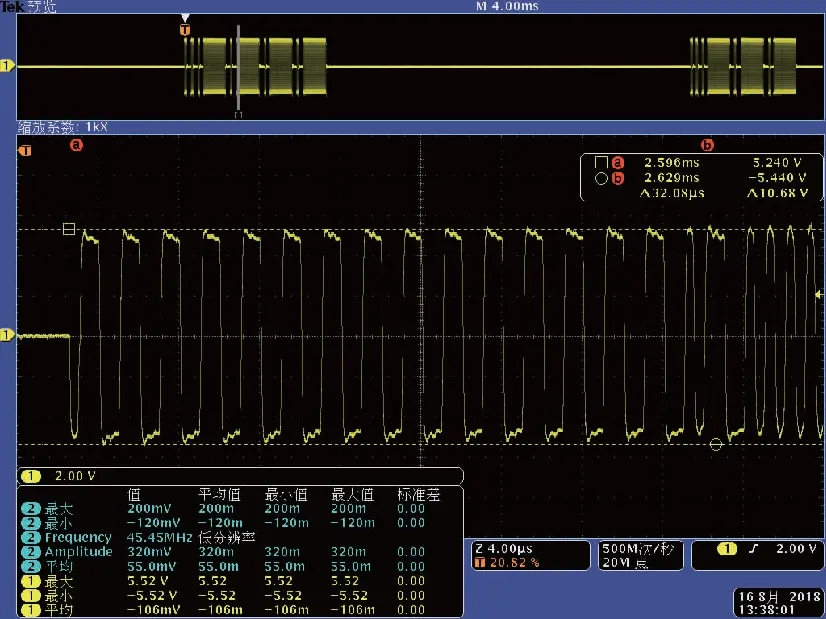

圖9中,RxClk是接收時鐘,Tx是HDLC數據幀,MAIN_OUT為WTB數據幀,幀頭32 bits,這里以HDLC數據是0x1,1個字節為例。分析WTB波形,與標準要求一致。圖10、圖11是通過示波器監測的實際波形,符合WTB一致性要求。通過TCN分析儀多次長時間測試,所設計的WTBC編解碼器能夠被分析儀很好地識別,不存在丟幀和錯幀(如圖12、圖13所示),符合IEC 61375標準規定。

圖10 測試波形(WTB幀頭)

圖11 測試波形(WTB幀)

圖12 TCN分析儀測試結果

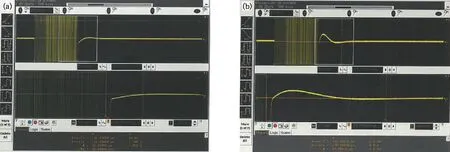

WTB一致性測試檢驗依據是GB/T 28029.2-2011《列車通信網絡一致性測試》,檢驗項目包括WTB設備節點的插入損失測試,WTB設備中間設置的輸入阻抗測試,WTB設備發送器測試,WTB設備發送器幀尾測試,WTB設備發送器噪聲測試,WTB設備發送器容錯測試,WTB設備接收器測試,WTB鏈路層接口測試和穩定性測試。檢驗項目全部測試通過,B線發送幀尾測試如圖14所示。

(1)網關發送幀尾,輸出信號第一次達到1.100 V電平之后20.0 μs后的波動范圍-B線

(2)網關發送幀尾,輸出信號第一次達到1.100 V電平之后64.0 μs后的波動范圍-B線

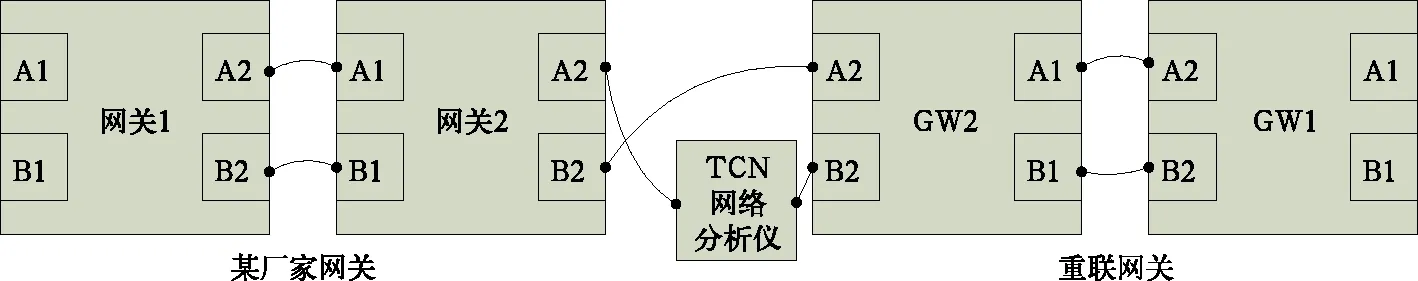

該WTBC編解碼器已應用于某型動車組WTB重聯網關,并通過了與其他廠家網關的互聯互通測試,實現不同廠家設備的互控。為了驗證重聯網關WTBC編解碼器功能和可靠性,在某型動車組列車進行通信試驗,試驗拓撲如圖15所示,TCN網絡分析儀串聯在主從控車中間(以測試線路B為例),在動車組運行過程中監測WTB通信數據。在監測期間,未發生WTB初運行,WTB通信正常。

圖14 WTB一致性測試

圖15 測試拓撲圖

5 結 論

WTBC編解碼器是重聯網關的重要組成部分,數據格式符合IEC 61375的要求,目前已應用于某型動車組上。實踐結果表明,帶有該WTBC編解碼器的重聯網關能夠和其他廠家網關互聯互通,并通過運營考核,可靠性高。