一種基于FPGA的LVDS數據接收方法

王政 張賓

摘要:LVDS傳輸方式越來越多的用于高速信息傳輸中,基于FPGA的LVDS數據接收的應用越來越廣泛。本文介紹了一種接收ADS5263芯片輸出的LVDS數據的方法,以及在實現過程中需要注意的重點。通過測試,該方法能夠適應不同LVDS數據率的需求。

關鍵詞:ADS5263;LVDS;FPGA

中圖分類號:TP274 文獻標識碼:A 文章編號:1007-9416(2019)07-0115-02

0 引言

數據的傳輸是電子系統與外界設備進行信息交換及數據融合的基礎,LVDS采用高速差分信號通訊,電壓擺幅較低,可以應用于長距離通信也可用于板內通信,是當今高速數據傳輸的主流解決方案[1]。

ADS5263是德州儀器(TI)推出的四信道16位模數轉換器 (ADC)。該芯片采樣頻率高達100MSPS,數據輸出采用LVDS電平形式。本文介紹了一種基于FPGA的LVDS電平數據接收方法,在工程中驗證了該方法是穩定可行的。

1 硬件平臺說明

FPGA與ADS5263的互聯中需要注意的是,ADS5263芯片的輸出信號DCO、FCO和數據信號(OUT0P/N~OUT7P/N)均連到FPGA的局部管腳(GC),并做等長處理。

1.1 LVDS數據格式

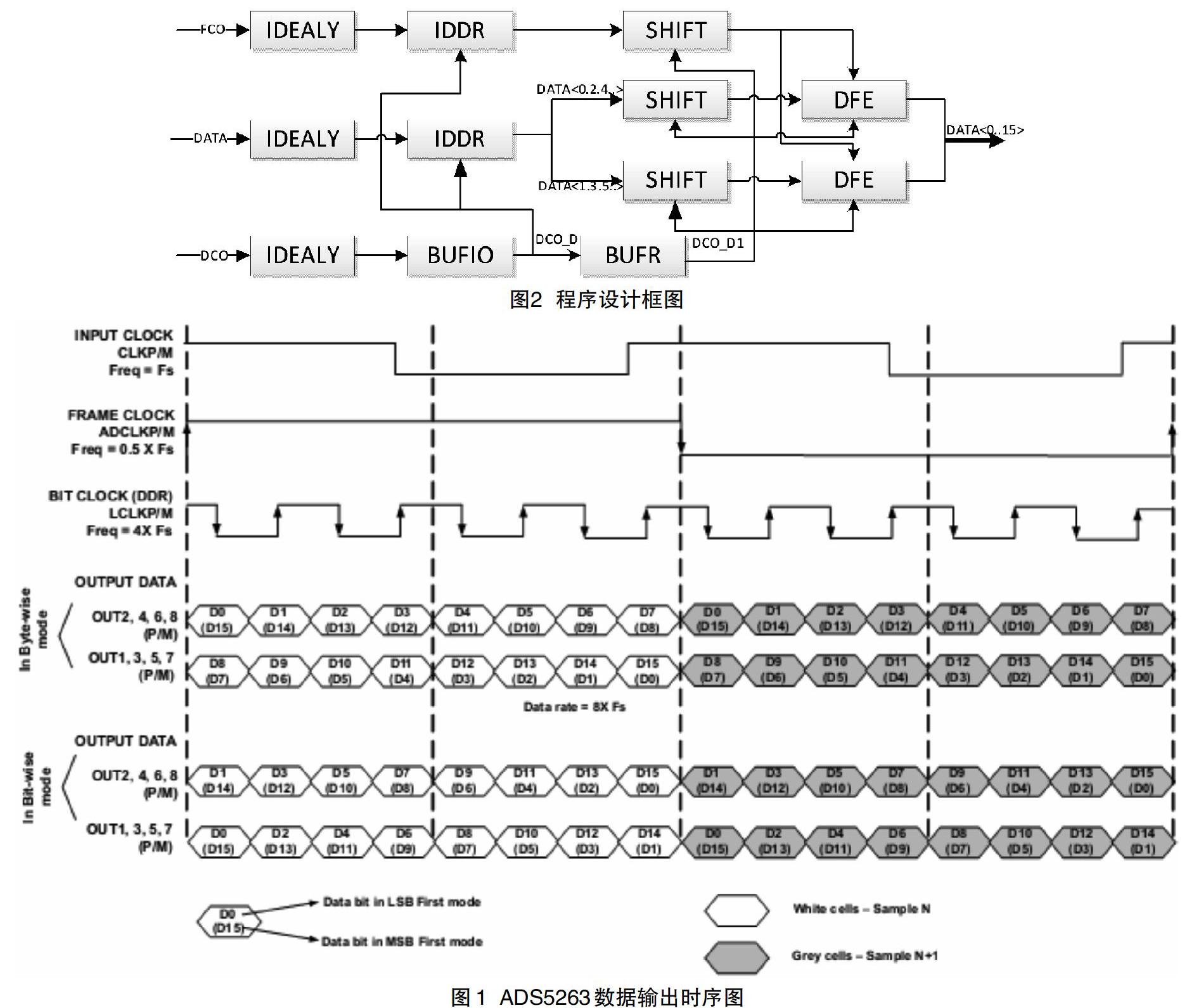

ADS5263有兩種工作模式:單差分對輸出模式和兩差分對輸出模式[2]。本文就兩差分對輸出模式(即雙線模式)做介紹。圖1表示ADS5263輸出數據的時序。

1.2 FPGA簡介

FPGA為XILINX公司的Virtex4系列芯片XC4VLX25-11SF363,該芯片具有25K個門邏輯單元、1260Kb的RAM、48個DSP48E Slices。該芯片可靠性高、功耗低及環境適應性等方面都滿足設計要求。

2 接收程序設計與實現

2.1 程序設計思路

從數據的時序上可以看出DCO的上升沿代表數據鎖存時機,FCO的沿代表每幀數據的始末,以此分辨AD采樣數據。

在FPGA程序設計中將DCO作為敏感時鐘,將FCO作為與其同步的數據信號作為待處理的數據,只要是在FCO的上升沿或者下降沿鎖存與其同步的數據,就可以得到準確穩定的AD采樣數據,因此只需要保證在DCO、FCO和數據在鎖存器之前經過的延時是同樣的,就可以確保每次獲得數據的準確性。

為了確保延時的一致,在FPGA內部保證信號從FPGA管腳到鎖存器的延時一致,因此使用IDELAY來做調整,并盡量使各個路徑經過的模塊盡量一致。

2.2 程序模塊說明

2.2.1 IDELAY和IDELAY_CTL

IDELAY可以設定為固定延時模式和可變延時模式,可以通過IOBDELAY_TYPE可配置。在固定延時模式下,通過配置參數IOBDELAY_VALUE確定延時的值,0-63可選,當設置為0時,模塊固有延時為400ps。CE,C,INC,RST均無效。在可變延時模式下,通過與C(clk)同步的CE、INC、RST控制延時值的大小。

IDELAYCTRL模塊初始化配置時,REFCLK必須使用200M時鐘;RST為50ns以上異步高電平復位;RDY為REFCLK穩定指示,一旦REFCLK連續兩個以上時鐘周期不跳變,RDY信號無效。

在本例中,IDELAY采用可變模式,通過使用FPGA內部的VIO模塊在線調整延時值,達到穩定準確接收ADS5263數據的目的。

2.2.2 IDDR

IDDR例化時采取SAME_EDGE_PIPELINDE模式,在這個模式下,時鐘C的上升沿對應的數據在Q1輸出,下降沿對應的數據在Q2輸出,這樣可以在C的上升沿讀取Q1和Q2的狀態,就可以分別得到需要的雙沿數據。這樣可以達到LVDS數據解析的目的。

2.2.3 BUFIO和BUFR

BUFIO和BUFR均屬于IO內部資源,它們只能同一個時鐘區域的時鐘管腳驅動,輸出的信號可以驅動相鄰的三個時鐘區域。BUFIO特別適用于同源數據的鎖存。BUFIO的輸出只能直接驅動IO內部資源,如果需要輸出到FPGA內部邏輯資源,必須經過BUFR輸出。

2.3 程序設計流程

整個LVDS接收的程序框圖如圖2所示。

通過分析AD數據輸出時序可以看出,FCO的上升沿和下降沿使用DCO的上升沿完全可以捕獲,因此在FCO對應的路徑中,IDDR只使用了其中一個輸出,即Q0。在Q0進入移位寄存器后判斷Q0的狀態是否為上升沿或者下降沿,在FCO的上升沿或者下降沿時,移位寄存器輸出鎖存使能信號,并發送到數據通路。

這種方法只要采用相同的硬件平臺,不需要調整程序的參數可以接收不同的采樣率對應的數據。

在測試中調整ADS5263的采樣時鐘,對于10M-100M的采樣時鐘,接收模塊都可以正確輸出采樣數據。

3 結語

詳細介紹了一種基于FPGA的LVDS電平數據接收方法的設計與實現,對軟硬件設計中的若干問題作了說明和分析。通過測試,該方法有較好的適應能力,可滿足了工程應用中多種采集速率的需求。

參考文獻

[1] 張聰.基于LVDS的數據收發系統研究與實現[D].西安電子科技大學, 2017.

[2] TI.德州儀器推出首款支持更快、更小醫療影像設備的四信道16位100 MSPS ADC[J].電子與電腦,2011(06):75.