FPGA硬核處理器系統(tǒng)的數(shù)字化集成電路設(shè)計

摘 要:為最大程度降低系統(tǒng)成本,提高工作效率,提出FPGA硬核處理器系統(tǒng)的數(shù)字化集成電路設(shè)計。通過對電源電路、接口電路以及主控電路進(jìn)行設(shè)計,完成電路整體設(shè)計。結(jié)合電路抗干擾設(shè)計,實現(xiàn)數(shù)字化集成電路設(shè)計。仿真實驗證明,設(shè)計的集成電路相比常規(guī)電路,使得FPGA硬核處理器系統(tǒng)的工作效率更高,并且降低29.5%能耗。

關(guān)鍵詞:硬核處理器;數(shù)字化;集成電路;電路設(shè)計

中圖分類號:TH744文獻(xiàn)標(biāo)識碼:A

我國多數(shù)機械裝置常常應(yīng)用FPGA硬核處理器來降低裝置成本、功耗,從而提高裝置性能。FPGA硬核處理器系統(tǒng)能夠集成分立處理器,具有可編程邏輯的靈活性。[1]系統(tǒng)中常規(guī)電路設(shè)計雖然可以滿足裝置各項性能要求,但是會產(chǎn)生面積較大的電路板,嚴(yán)重影響機械裝置的成本,同時產(chǎn)生不必要的電能消耗,因此提出FPGA硬核處理器系統(tǒng)的數(shù)字化集成電路設(shè)計。

1 FPGA硬核處理器系統(tǒng)的電路整體設(shè)計

根據(jù)FPGA硬核處理器系統(tǒng)的功能特征,首先對系統(tǒng)的主控電路進(jìn)行設(shè)計。為滿足多種類型信號的處理要求,設(shè)計的主控電路如圖1所示。

設(shè)計的主控電路在確保FPGA硬核處理器系統(tǒng)的穩(wěn)定性之外,還增加了抗復(fù)位功能,最大程度降低系統(tǒng)功耗。[2]

同時,為減少不必要的電能消耗,將FPGA硬核處理器系統(tǒng)的接入電源設(shè)計成5V。電源電路是FPGA硬核處理器系統(tǒng)從外界獲得電源的唯一途徑,因此設(shè)計電源轉(zhuǎn)換電路,實現(xiàn)220V電源到5V電源的轉(zhuǎn)變。將電源接口電路設(shè)計成F接口,[3]采用I/O接口,I/O接口芯片,通過輸入不同的命令和參數(shù),使得I/O電路動作,成為信號高速交換的通道。通過對主控電路、電源電路以及接口電路進(jìn)行設(shè)計,完成電路整體設(shè)計。

2 數(shù)字化集成電路的實現(xiàn)

在FPGA硬核處理器系統(tǒng)中,信號分為模擬信號、數(shù)字信號、高頻信號以及低頻信號,常常受到外界信號干擾,大大降低電路中信號處理精度,使得FPGA硬核處理器系統(tǒng)工作效率降低。因此為了增加電路抗干擾能力,對電路進(jìn)行抗干擾設(shè)計。

在FPGA硬核處理器系統(tǒng)的主控電路中加入差分放大器,對電信號放大處理。差分放大器通過F接口,使得輸入頻率為25HZ的電信號,轉(zhuǎn)換成以正弦和余弦兩路電信號,應(yīng)用互聯(lián)網(wǎng)技術(shù)對兩路電信號進(jìn)行隔絕,確保了信號的原始性。由于差分放大器輸出為高壓電信號,需利用220Ω的電阻將高壓電信號調(diào)制成5V,形成低壓電信號,從而實現(xiàn)數(shù)字化集成電路的設(shè)計。

通過對主控電路、電源電路以及接口電路進(jìn)行設(shè)計,完成電路整體設(shè)計。結(jié)合電路抗干擾設(shè)計,實現(xiàn)數(shù)字化集成電路設(shè)計。

3 仿真分析

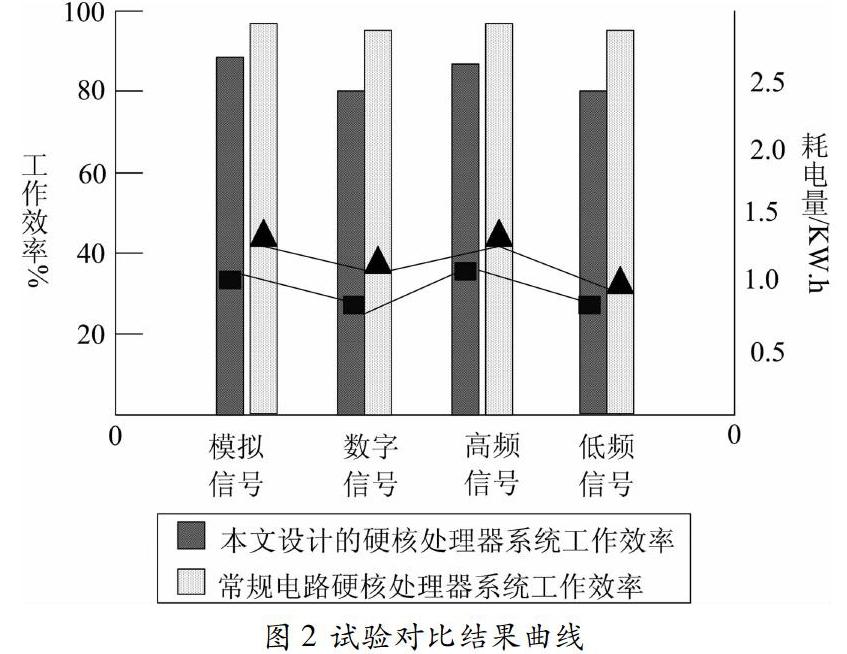

仿真試驗需準(zhǔn)備的設(shè)備及參數(shù)包括:搭載simulation仿真軟件的計算機兩臺套、兩種設(shè)計電路的FPGA硬核處理器系統(tǒng)(常規(guī)的以及本文提出的數(shù)字化集成電路)、仿真參數(shù)變量。試驗過程中,多次改變輸入的信號形式,對兩種不同電路的FPGA硬核處理器系統(tǒng)進(jìn)行工作效率對比實驗。同時記錄FPGA硬核處理器系統(tǒng)單位時間的耗電量,繪制試驗結(jié)果圖表,如圖2所示。

由圖2可知,本文設(shè)計的集成電路,無論處理哪種類型信號,工作效率幾乎不變,穩(wěn)定性極高。同時采用算術(shù)平均值計算法,計算能耗比率,得出本文設(shè)計的集成電路相比常規(guī)電路,使得FPGA硬核處理器系統(tǒng)的能耗比率降低29.5%。

4 總結(jié)

本文提出FPGA硬核處理器系統(tǒng)的數(shù)字化集成電路設(shè)計,基于電路整體設(shè)計、數(shù)字化集成電路設(shè)計,完成了提出的電路設(shè)計。實驗證明,本文設(shè)計的集成電路,能夠降低PGA硬核處理器系統(tǒng)功耗,提高工作效率。

參考文獻(xiàn):

[1]李冰,周岑軍,陳帥,等.用于SRAM PUFs的偽隨機數(shù)發(fā)生器的FPGA實現(xiàn)[J].電子學(xué)報,2017(9).

[2]張琳,梅雪松,陳勇.基于SoCFPGA的光伏電力通信管理機系統(tǒng)[J].電子技術(shù)應(yīng)用,2018.

[3]李正杰,張英.一種千萬門FPGA芯片中DSP硬核的設(shè)計[J].微電子學(xué),2018,48,276(04):60-65.

作者簡介:王肖巍(1977-),男,漢族,陜西乾縣人,碩士,工程師,研究方向:集成電路設(shè)計。