基于FPGA的多路Cameralink數字圖像光纖傳輸系統

白金成

(中國科學院 長春光學精密機械與物理研究所,吉林 長春 130033)

1 引 言

隨著無人機行業的快速發展,航空光電吊艙作為機載的重要偵查設備,在目標捕獲、跟蹤、識別等領域得到了廣泛的應用[1]。航空光電吊艙的跟蹤[2]、識別是通過對高可靠性的數字圖像實時處理實現的,因此高速可靠的圖像傳輸是影響其跟蹤、識別等性能優劣的重要指標之一。

傳統的航空光電吊艙大多采用導電環進行Cameralink協議[3]的數字圖像傳輸,存在傳輸帶寬低、抗干擾性差、配線復雜等問題,后期的錯誤排查也非常困難[4]。數字圖像的傳輸問題一定程度上制約了光電吊艙的發展。光纖傳輸由于抗干擾能力強、帶寬高、易敷設、壽命長等特點被廣泛應用于數據傳輸方面,利用光纖傳輸數字圖像,可以克服傳統導電環傳輸數字圖像的諸多缺點,很大程度提高了數字圖像傳輸的抗干擾能力和可靠性[5]。

目前,許多航空光電吊艙的數字圖像都采用光纖傳輸的方式,例如基于MAX9259/MAX9260的光纖傳輸,雖然開發速度快,但是靈活性不強且傳輸帶寬有一定的限制[6],并且目前很多光電吊艙的數字圖像光纖傳輸都是單通道的,無法滿足多路圖像的同時傳輸[5,7],隨著數字相機的頻率越來越高,傳輸的數據量越來越大,航空光電吊艙對數據傳輸的要求越來越高[8],本文設計了數字圖像光纖傳輸系統,利用單根光纖傳輸多路Cameralink數字圖像,以FPGA為核心處理芯片,采用Aurora 8 B/10 B協議,并結合HTW0402HTW4002光模塊實現多路Cameralink數字圖像的光纖傳輸。

2 FPGA光纖傳輸系統設計

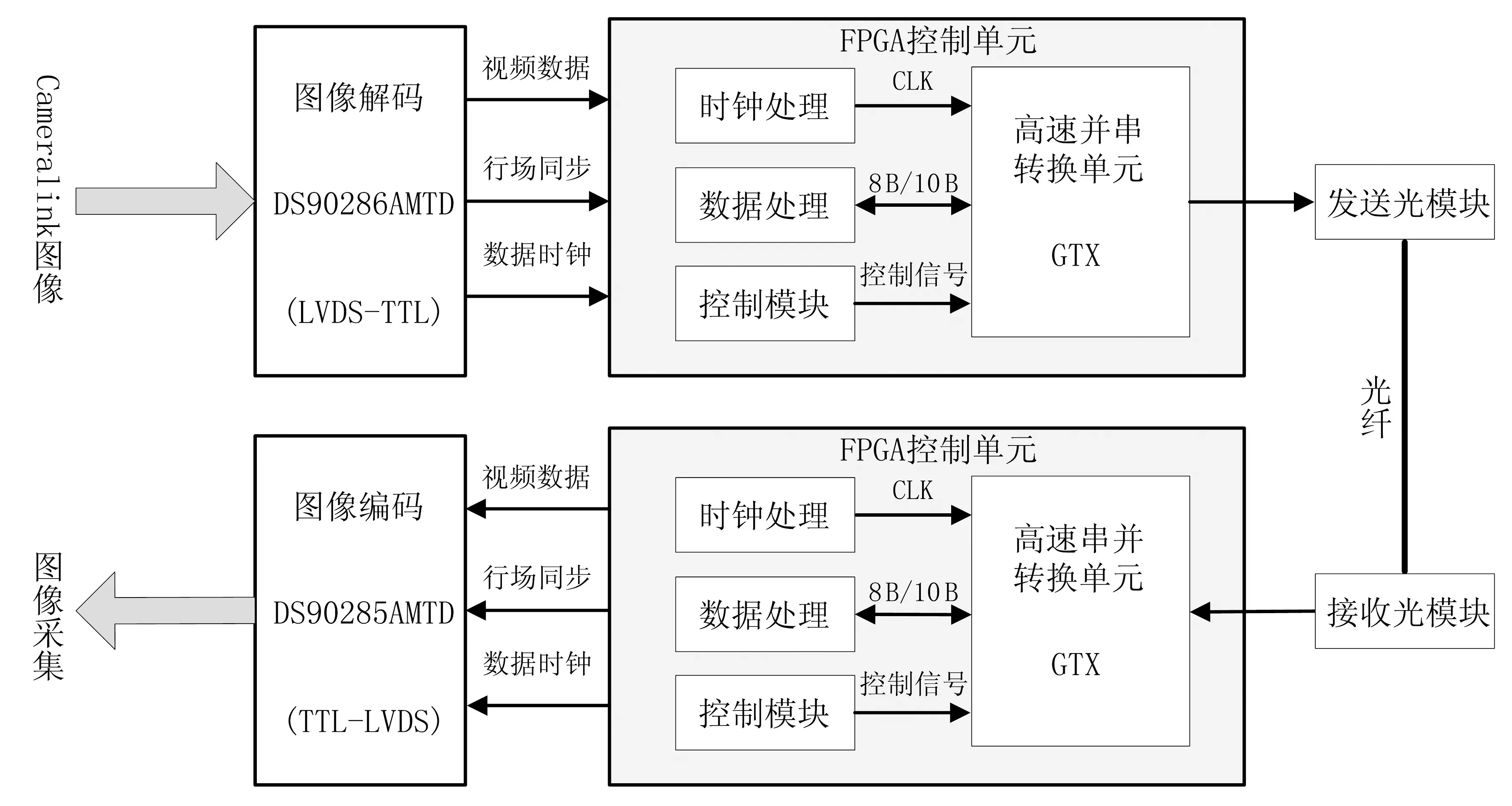

2.1 系統硬件結構設計

系統硬件結構如圖1所示。本系統選用FPGA作為系統控制處理核心,結合圖像編解碼芯片及光模塊實現多路Cameralink數字圖像的光纖傳輸。

圖像編解碼:輸入的圖像為LVDS的Cameralink數字圖像,利用解碼芯片DS90CR286MTD將LVDS信號轉化為28位并行TTL信號,其中包括24位數據、1位幀同步和1位像素時鐘信號、2位行場同步信號。在接收端,采用編碼芯片DS90CR285MTD完成相反的工作,將FPGA輸出的28位并行TTL信號轉換為LVDS圖像信號,還原輸入的原LVDS的Cameralink數字圖像。

FPGA控制處理器:FPGA作為光纖傳輸系統的核心處理器件,實現整個系統時鐘的控制、數據處理、串并轉換的信號控制等功能。在發送端,FPGA接收經解碼單元轉換后的并行數據,根據相機輸出時鐘的具體情況,對數據做相應處理,并產生控制信號,將處理后的數據及控制信號進行并轉串的操作;在接收端,FPGA根據串并轉換單元的信息,解出相機的時鐘信號,并還原數據及行、場同步信號傳輸給視頻采集設備。

圖1 系統結構硬件框圖Fig.1 Hardware block diagram of system structure

收發光模塊:光模塊負責光信號與電信號的相互轉換。本系統選用的是中航光電的型號為HTW4002(發送)/HTW0402(接收)的光模塊,該型號光模塊是一款高性能的4路CWMD光模塊,單通道最大傳輸速率為10.312 5 Gb/s,可用于10 km內光互聯數據通信。該模塊通過一根光纖可完成4路信號的傳輸,操作簡單,使用方便,且滿足寬工作溫度范圍,性能穩定。

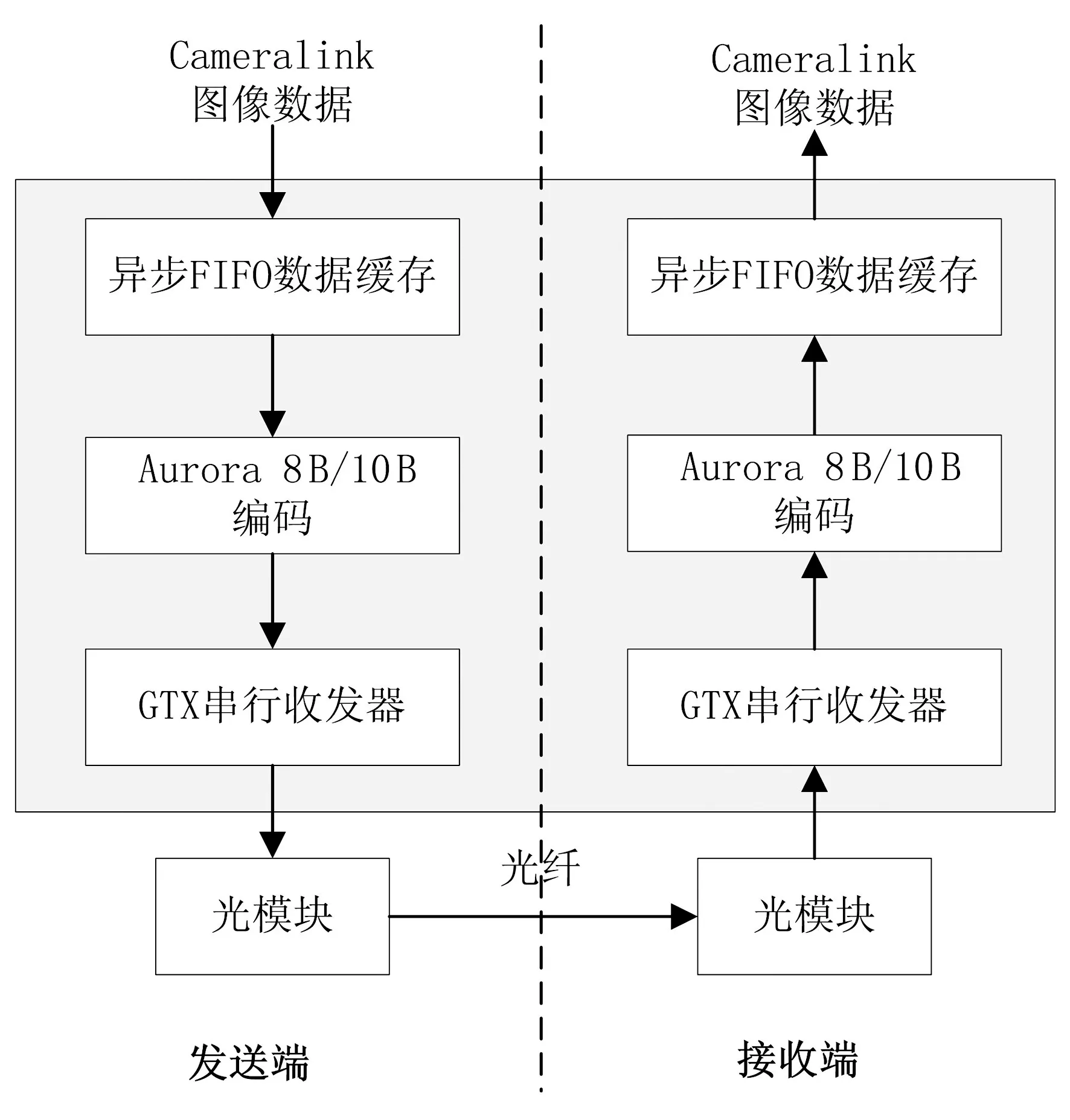

2.2 光纖傳輸方案設計

Cameralink數字圖像光纖傳輸設計方案如圖2所示。在發送端,通過異步FIFO將轉換后的TTL并行圖像數據信號進行數據緩存,將相機時鐘域轉換到Aurora協議的用戶時鐘域;按照Aurora 8 B/10 B協議將異步FIFO緩存后的數據進行編碼,編碼后的數據經GTX串行收發器轉換為高速串行的數據送入到發送光模塊,經光纖導線傳到接收端;在接收端,串行收發器將光模塊接收到的串行數據按照協議轉換成并行數據并解碼,再經異步FIFO進行數據重建,將并行圖像數據從Aurora協議用戶時鐘域轉換到相機時鐘域,完成了Cameralink數字圖像的光纖傳輸。

圖2 光纖傳輸設計方案框圖Fig.2 Block diagram of optical fiber transmission

2.2.1 異步FIFO數據緩存

異步FIFO數據緩存是為了解決相機時鐘域與Aurora協議用戶時鐘域的匹配問題。Aurora協議根據配置的工作時鐘會產生固定的用戶時鐘,而不同的相機往往輸出的像素時鐘不同,兩者之間存在時鐘域不匹配的問題,所以本系統通過異步FIFO數據緩存來解決像素時鐘域與Aurora協議用戶時鐘域的匹配問題。異步FIFO數據緩存原理框圖如圖3所示。

圖3 異步FIFO原理框圖Fig.3 Principle block diagram of asynchronous FIFO

異步FIFO首先在FPGA內部建立兩個FIFO存儲塊,分別為FIFO1和FIFO2,寫FIFO控制模塊以相機輸出的像素時鐘作為FIFO的寫入時鐘,根據Fvalin和Lvalin同步信號將奇數及偶數行圖像數據分別寫入到FIFO1和FIFO2中。讀FIFO控制模塊根據寫FIFO控制模塊的狀態及FIFO塊的存儲狀態產生相應的讀FIFO控制信號,以Aurora協議的用戶時鐘作為讀時鐘,讀出的數據經圖像重建后產生新的行場數據。

2.2.2 Aurora 8 B/10 B協議

Aurora協議是Xilinx公司針對高速傳輸開發的一種鏈路層協議[9],該協議可根據需要靈活的進行多通道綁定,擴展光纖鏈路數量,提高傳輸帶寬,同時還能保證傳輸的高速同步和穩定。本系統采用Aurora 8 B/10 B協議,通過8 b/10 b的編碼方式,實現并串轉換的高速差分傳輸。具體實現過程是通過Xilinx公司開發的Aurora 8 B/10 B IP核,本系統中設置IP核的工作模式為4字節單通道流模式,傳輸的線速率為3.125 Gb/s,參考時鐘為125 MHz,通過外部高精度的晶振產生,由FPGA專用的高速時鐘引腳傳入到IP核,以保證傳輸速率的穩定;IP核外部數據寫入配置為32位的AXI接口形式。在發送端,可以直接將轉換為AXI格式的并行數據寫入到IP核的輸入端,IP核自動完成8 b/10 b的編碼,并完成并行數據到串行數據的轉換,并通過GTX模塊將串行數據通過差分信號傳輸到光模塊;在接收端,IP核將GTX接收到的差分信號自動進行串并轉換,并完成8 b/10 b的解碼,以AXI的格式將解碼后的并行圖像數據輸出,至此完成了由Aurora 8 B/10 B協議部分的單路數字圖像數據的傳輸。由于本系統采用的是4路波分復用的光模塊,多路圖像的傳輸相互獨立、互不影響,因此只需要復制單路圖像傳輸的方法,分別對多路圖像進行相應的處理,然后經光模塊的不同通道傳輸即可。

3 實驗結果及分析

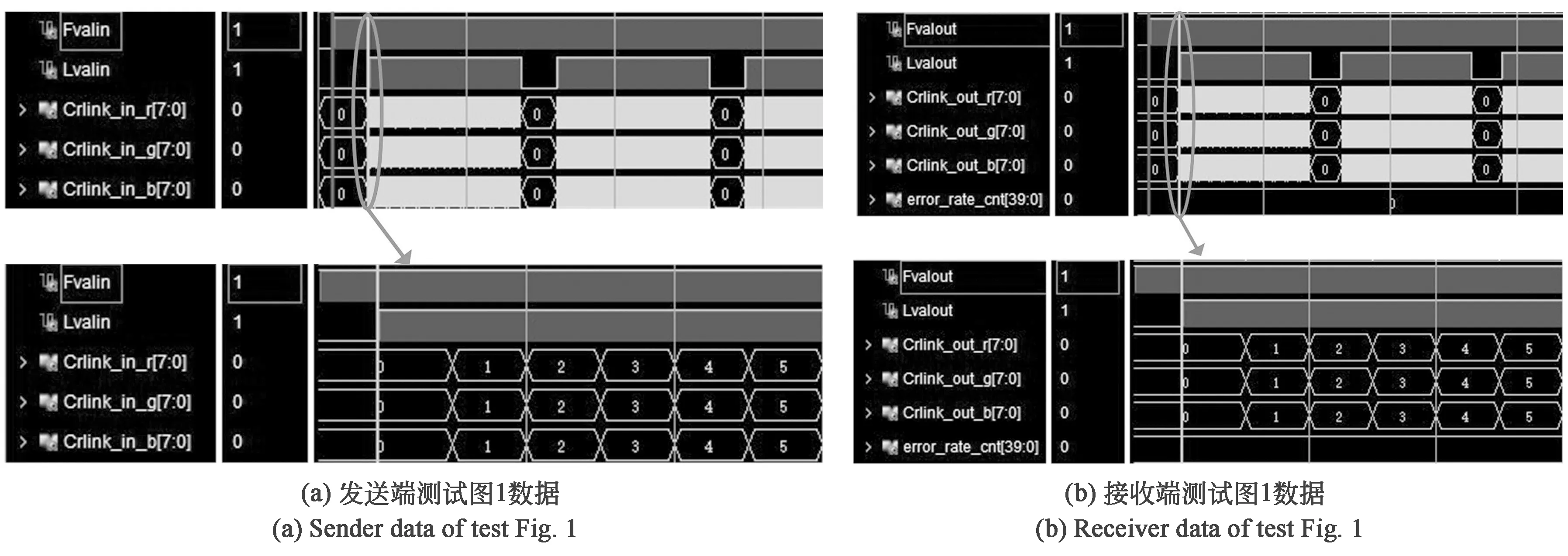

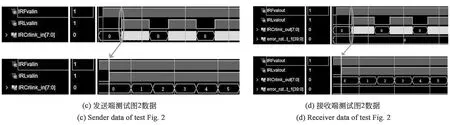

為驗證本文所設計系統的可行性及穩定性,進行了實驗驗證。為了驗證多路圖像的同時傳輸,在FPGA內部根據實際Cameralink相機的時序生成兩路30 Hz的測試圖,測試圖的數據規律性變化,這樣有利于調試。測試圖1大小為1 024×768,每個像素由8 bit的RGB分量組成。每行圖像像素值的變化相同,每行圖像的第一個像素的RGB分量均從0開始,以后每個像素的RGB分量依次累加1;測試圖2大小為640×512,每個像素位寬為8 bit,每行像素變化與測試圖1相同。并通過編寫誤碼率檢測模塊,檢測接收端的數據誤碼率,由于測試圖的每個位置上的像素固定,所以只需遍歷每幀圖像的像素值與生成的測試圖像素值是否匹配,計數不匹配的像素個數即可得到每幀圖像的誤碼率。通過FPGA內部的集成邏輯分析儀(ILA)對光纖傳輸前后的測試圖數據進行分析,得到如圖4所示的實驗結果。

圖4 測試圖傳輸前后的數據Fig.4 Data before and after transmission of test image

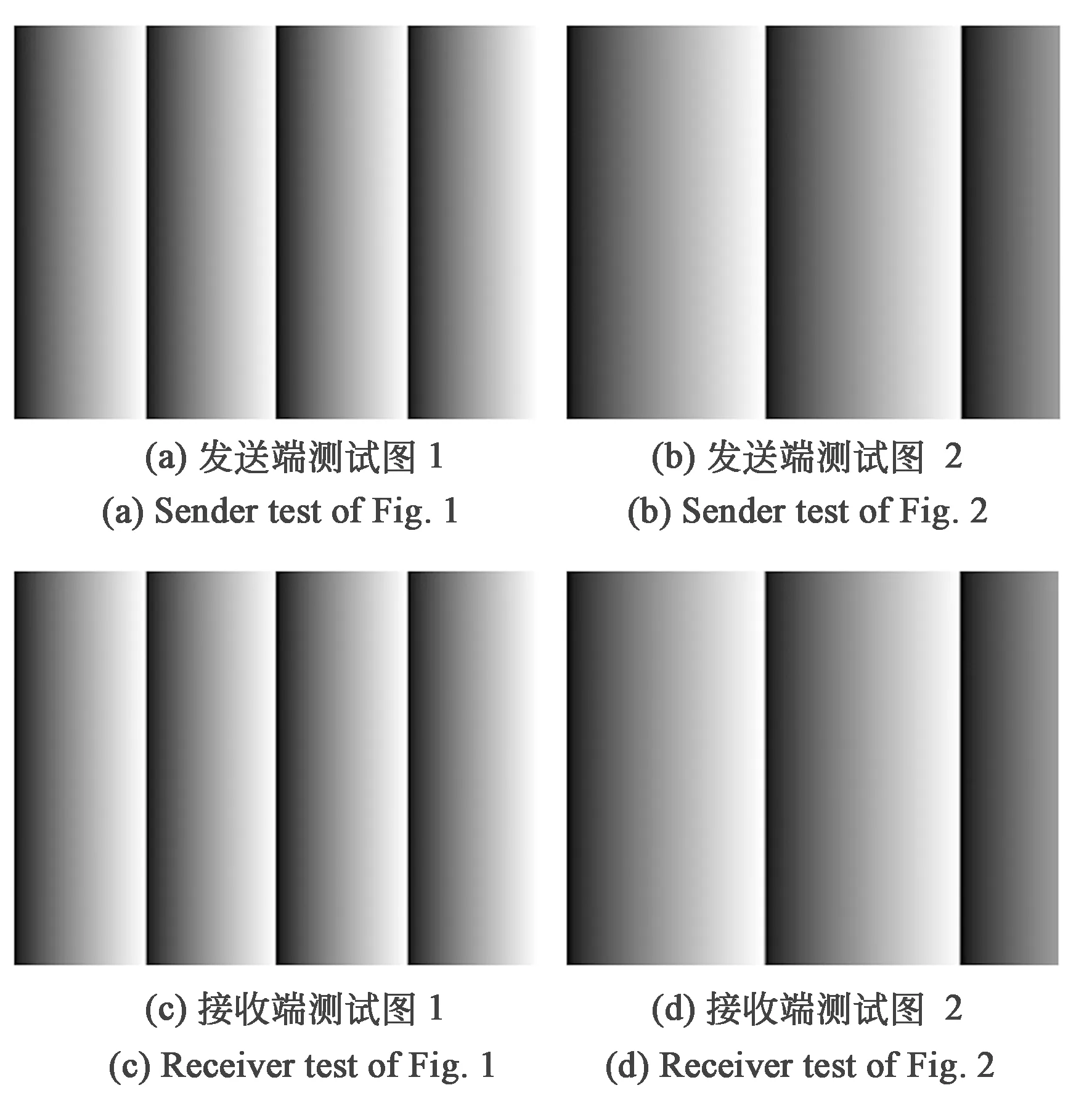

由圖4可知,兩路視頻接收端的測試圖數據與發送端的測試圖數據完全相同,由此可見,本系統接收端數據接收正確,能夠正常的進行2路圖像的收發數據。通過30 min的監測,共傳輸1.4×1012bit數據,2路誤碼率檢測模塊的計數結果均為0,未見誤碼,可知本系統傳輸的誤碼率低于10-12。在本文所設計的光纖傳輸系統的輸出端利用采集卡采集2路測試圖并顯示,測試圖傳輸前后的圖像如圖5所示。

從圖5中2路測試圖的原始圖像及經過光纖傳輸后的圖像對比可知,傳輸后的圖像清晰穩定。

圖5 傳輸前后的測試圖Fig.5 Testimage before and after transmission

4 結 論

本文以FPGA作為核心處理器,設計了多路Cameralink數字圖像的光纖傳輸系統。利用異步FIFO數據緩存、Aurora 8 B/10 B協議完成數字圖像的編碼、轉換等功能,結合4路波分復用的光模塊實現了多路數字圖像的同時傳輸,最多可同時傳輸4路數字圖像。實驗結果表明,所設計的系統能夠實現多路Cameralink數字圖像的光纖傳輸,傳輸圖像效果清晰穩定,傳輸通道誤碼率低于10-12,能夠應用于多路Cameralink數字圖像的光纖傳輸。