基于FPGA的Sobel邊緣檢測算法實現(xiàn)及VGA顯示

孫敬成 王正彥 張斌 李增剛 毛菲菲

摘要:? 針對已有的邊緣檢測算法存在的問題,本文采用Verilog語言對Sobel邊緣檢測算法進行研究。給出Sobel算法的現(xiàn)場可編程門陣列(FieldProgrammable Gate Array,F(xiàn)PGA)實現(xiàn)方案,分析了視頻圖形陣列(video graphics array,VGA)顯示圖像的工作機理,構(gòu)造了完整的電路模型,并在Altera的Cyclone II系列FPGA芯片上進行仿真及硬件調(diào)試,同時以實際算例進行仿真分析。仿真結(jié)果表明,基于FPGA的Sobel算法實現(xiàn)與VGA顯示技術(shù)相結(jié)合,不僅實現(xiàn)了在VGA上快速顯示圖像邊緣檢測結(jié)果,而且與串行相比,檢測速度提高了9倍,保證檢測結(jié)果的準(zhǔn)確性。該研究為應(yīng)用于嵌入式設(shè)計的圖像邊緣檢測提供了方法和策略,具有實際應(yīng)用價值。

關(guān)鍵詞:? Sobel算法; 邊緣檢測; FPGA; VGA顯示

中圖分類號: TP274+.5; TN911.73 文獻標(biāo)識碼: A

隨著機器視覺領(lǐng)域的廣泛應(yīng)用,邊緣檢測作為應(yīng)用基礎(chǔ),在處理過程中迎來更高的標(biāo)準(zhǔn)。邊緣是指像素灰度急劇變化的點的集合,是圖像最基本的特征。邊緣檢測的目的是標(biāo)識數(shù)字圖像中灰度變化明顯的點,在計算機視覺和圖形分析等應(yīng)用中起著重要作用。邊緣檢測的常見算法有梯度算子、Roberts、Laplacian、Kirsch、Sobel和Prewitt等算子[1]。目前,對這些常見算法的研究技術(shù)較為成熟,應(yīng)用領(lǐng)域也不斷擴大,在公安軍事方面,如公安業(yè)務(wù)圖片的判讀分析、指紋識別、人臉識別和圖片復(fù)原等都是成功應(yīng)用邊緣檢測的例子;在生物醫(yī)學(xué)方面,CT技術(shù)、X光肺部圖像增強和心電圖分析等也都應(yīng)用到圖像邊緣分析技術(shù)。這些應(yīng)用設(shè)計均采用Sobel算子,該算子可以利用卷積函數(shù)快速提取邊緣[2]。目前,該算法存在多種利用硬件描述語言實現(xiàn)的方式,但多數(shù)為串行輸入數(shù)據(jù),處理速度較慢,已不能很好地滿足實際應(yīng)用需求。基于此,本文采用Verilog語言,設(shè)計了Sobel算法的并行處理電路,并與VGA顯示控制相結(jié)合[3],實現(xiàn)了圖像的檢測和顯示,通過對比驗證了該模型的實用性和有效性。該研究為應(yīng)用于嵌入式設(shè)計的圖像邊緣檢測奠定了理論基礎(chǔ),具有一定的實際應(yīng)用價值。

1 Sobel算法

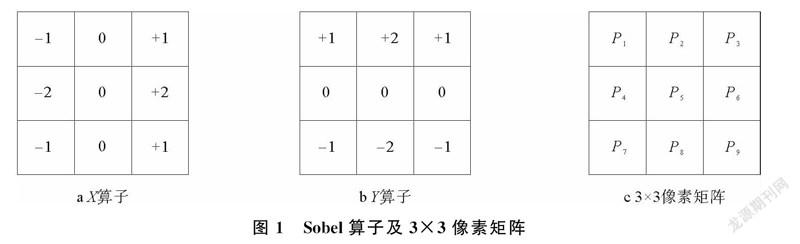

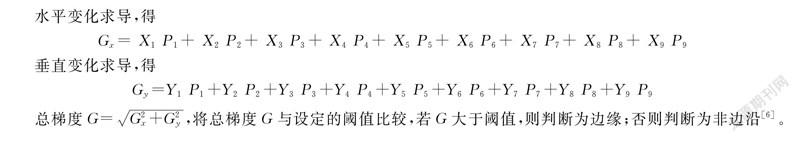

Sobel算法是計算機視覺領(lǐng)域重要處理方法之一,主要通過獲取數(shù)字圖像的一階梯度,實現(xiàn)邊緣檢測,以被處理像素為中心,對其鄰域進行灰度分析[4]。Sobel算法的核心在于像素矩陣的卷積,利用自身模板算子檢測水平邊緣和垂直邊緣,因此Sobel邊緣檢測通常帶有方向性。

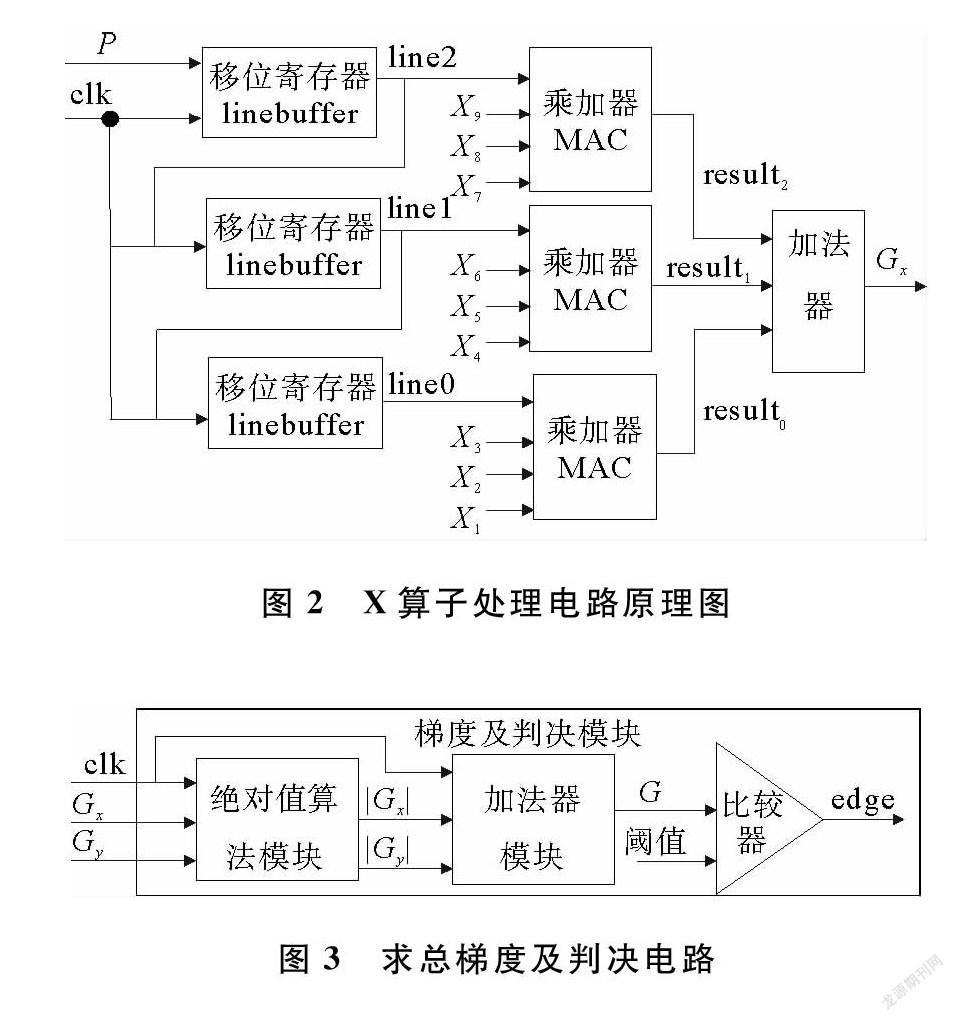

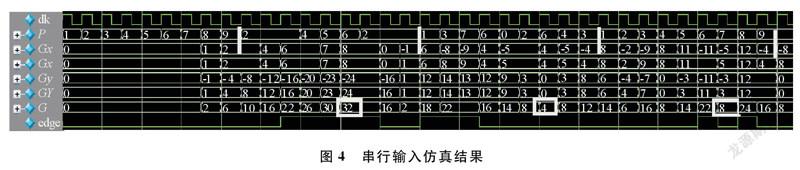

Sobel算法主要依靠兩個模板算子,X算子(水平算子)和Y算子(豎直算子),利用兩個算子與已知的圖像像素點矩陣進行卷積運算,圖像像素點與其鄰域像素點的灰度值組成3×3的像素矩陣[5]。Sobel算子及3×3像素矩陣如圖1所示。

2.2 并行輸入方案

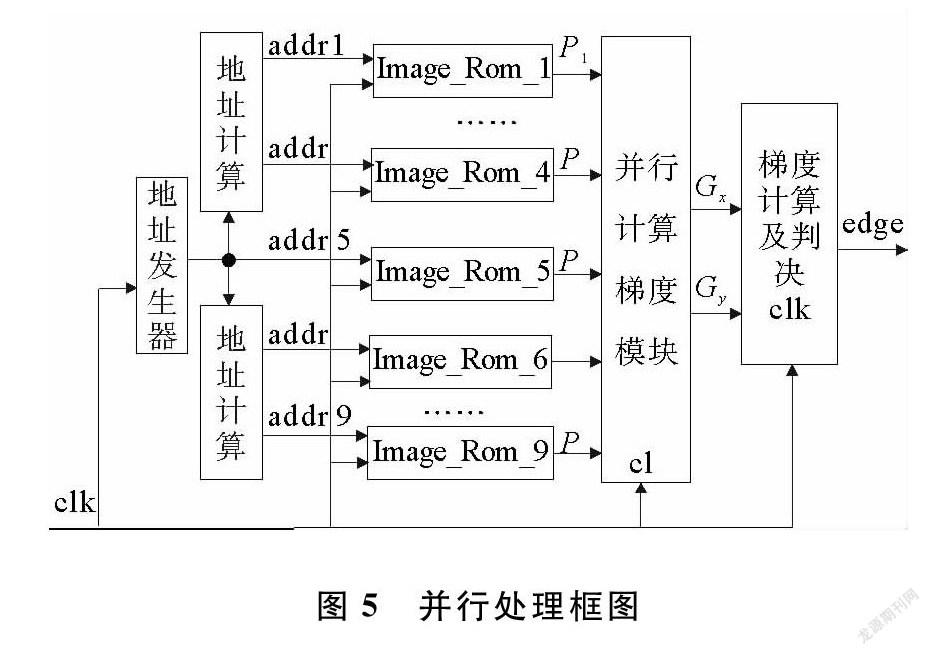

以上串行方案需要9個時鐘周期才能檢測1個像素點,速度較慢。為了提高檢測速度,本研究提出并行輸入方案,采用9個ROM存放圖像灰度數(shù)據(jù),每個時鐘可同時并行取出計算所需的9個像素值。

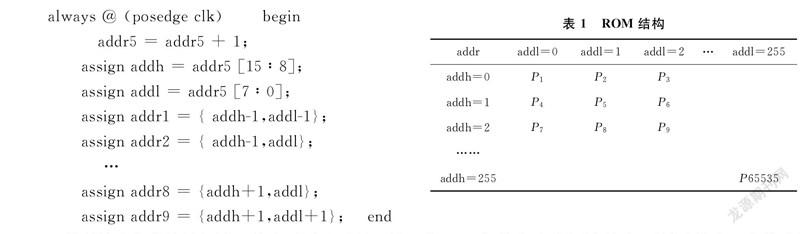

以256×256圖片為例,ROM結(jié)構(gòu)如表1所示。令addr為16位地址,中addl為低8位,addh為高8位。設(shè)P1~P9為3×3的中心像素點及其鄰域,經(jīng)分析可知,由P5的地址可推算出其余8個數(shù)據(jù)的地址。例如,若P5地址addr5為{addh,addl},那么addr2為{addh1,addl},addr4為{addh,addl1},依次類推出其余地址。因此只要在時鐘信號作用下遞增產(chǎn)生addr5,其余地址均可計算得到。若中心地址的鄰域數(shù)目不足8個,可令缺失的像素數(shù)據(jù)P輸入為零。并行處理框圖如圖5所示。

地址計算的Verilog代碼如下。

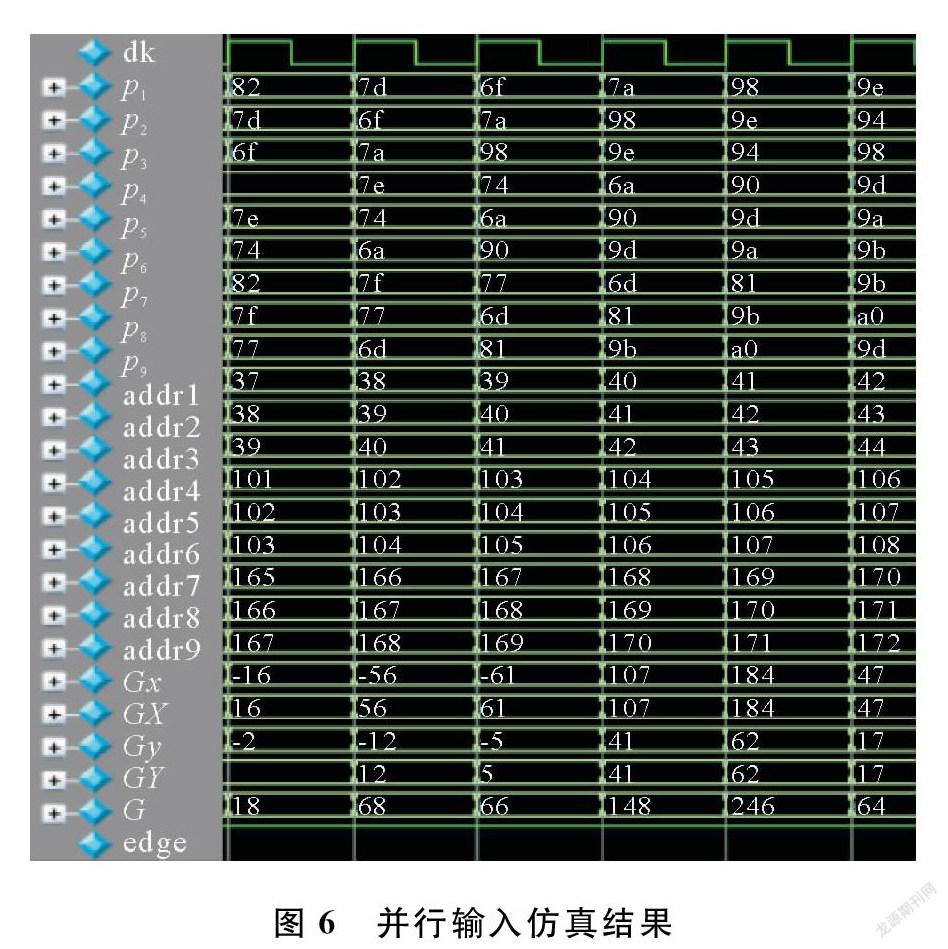

并行輸入仿真結(jié)果如圖6所示,當(dāng)中心地址addr5為102時,其余地址如圖所示,可同時提取9個像素數(shù)據(jù)P1~P9進行處理,并行計算出GX、GY、G、edge。而且每個時鐘可檢測1個像素點,檢測速度提高了9倍。

3 VGA圖像顯示控制

3.1 VGA顯示標(biāo)準(zhǔn)

視頻圖形陣列(video graphics array,VGA)使用模擬信號的電腦顯示標(biāo)準(zhǔn),支持640×480,1 024×768等多種分辨率,是目前常用的圖像標(biāo)準(zhǔn)之一[10]。VGA標(biāo)準(zhǔn)有5個標(biāo)準(zhǔn)信號,分別為行同步信號HS、場同步信號VS、紅、綠、藍顏色信號R、G、B,其中顏色信號是模擬信號[11]。

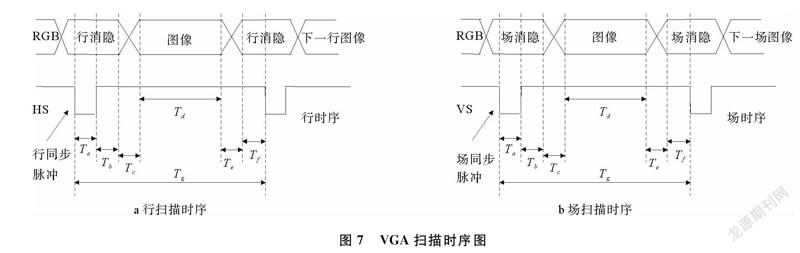

VGA顯示器以逐行掃描的方式顯示圖像,掃描順序從左到右,從上到下[12]。以640×480分辨率為例,時鐘頻率為25 MHz,從左上角開始往右掃描(稱為行正程),直到掃完640個像素點,再回到最左邊(稱為行逆程),開始第2行的掃描,如此往復(fù),掃完第480行即完成一幀圖像的顯示(稱為場正程),這時又回到左上角(稱為場逆程),開始掃描下一幀圖像。在行、場掃描的正程顯示圖像,逆程不顯示圖像,稱為消隱[13]。行、場掃描的逆程分別是在行同步、場同步信號的控制下進行,VGA掃描時序圖如圖7所示。其中,一個行同步周期(圖7a中Tg)為800個像素時間,一個場同步周期(圖7b中Tg)為525行時間[14]。

3.2 VGA顯示控制原理

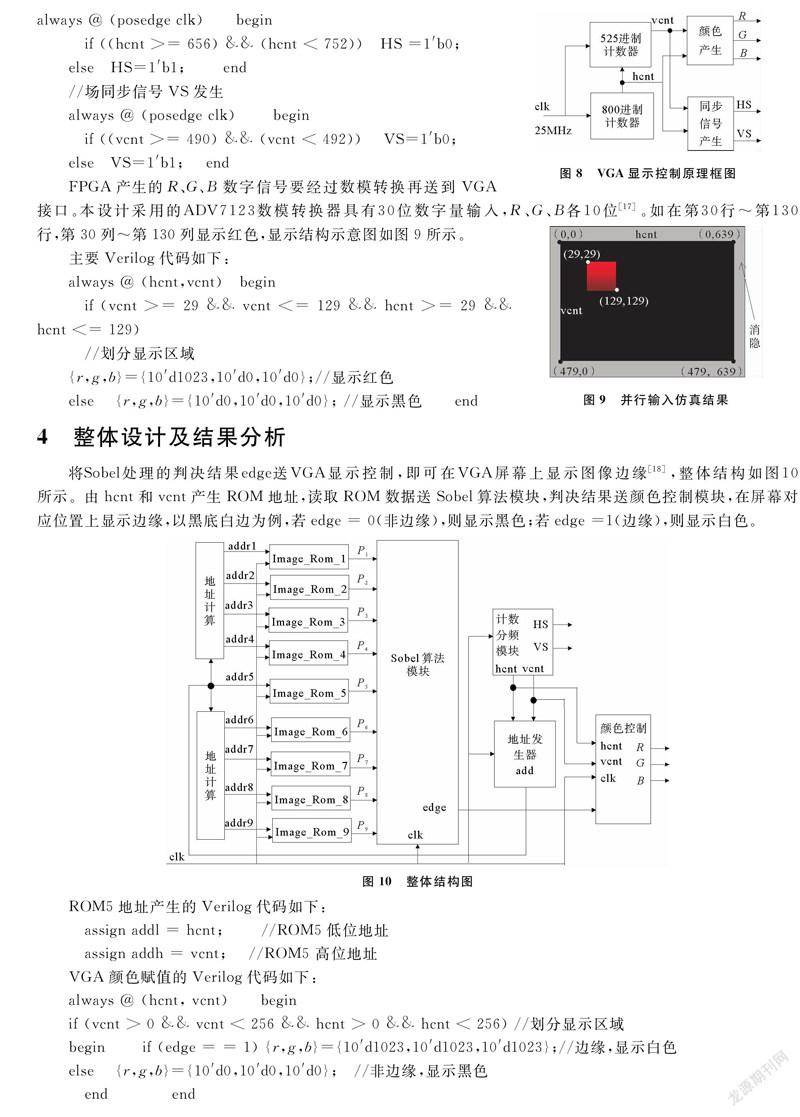

VGA顯示控制原理框圖如圖8所示,通過對25 MHz時鐘進行800進制計數(shù)分頻得到行同步HS,對行頻信號進行525進制計數(shù)分頻得到場同步信號VS[15]。計數(shù)值hcnt、vcnt與屏幕位置一一對應(yīng),hcnt=0,vcnt=0對應(yīng)屏幕左上角像素點[16],可根據(jù)此計數(shù)值確定屏幕位置控制R、G、B顏色值。產(chǎn)生行同步信號HS、場同步信號VS的Verilog代碼如下:

//行同步信號HS發(fā)生

always @ (posedge clk) begin

if ((hcnt >= 656) && (hcnt < 752)) HS =1′b0;

else HS=1′b1; end

//場同步信號VS發(fā)生

always @ (posedge clk) begin

if ((vcnt >= 490) && (vcnt < 492)) VS=1′b0;

else VS=1′b1; end

FPGA產(chǎn)生的R、G、B數(shù)字信號要經(jīng)過數(shù)模轉(zhuǎn)換再送到VGA接口。本設(shè)計采用的 ADV7123數(shù)模轉(zhuǎn)換器具有30位數(shù)字量輸入,R、G、B各10位[17]。如在第30行~第130行,第30列~第130列顯示紅色,顯示結(jié)構(gòu)示意圖如圖9所示。

主要Verilog代碼如下:

always @ (hcnt,vcnt) begin

if (vcnt >= 29 && vcnt <= 129 && hcnt >= 29 && hcnt <= 129)

//劃分顯示區(qū)域

{r,g,b}={10′d1023,10′d0,10′d0};//顯示紅色

else {r,g,b}={10′d0,10′d0,10′d0}; //顯示黑色 end

4 整體設(shè)計及結(jié)果分析

將Sobel處理的判決結(jié)果edge送VGA顯示控制,即可在VGA屏幕上顯示圖像邊緣[18],整體結(jié)構(gòu)如圖10所示。由hcnt和vcnt產(chǎn)生ROM地址,讀取ROM數(shù)據(jù)送Sobel算法模塊,判決結(jié)果送顏色控制模塊,在屏幕對應(yīng)位置上顯示邊緣,以黑底白邊為例,若edge = 0(非邊緣),則顯示黑色;若edge =1(邊緣),則顯示白色。

ROM5地址產(chǎn)生的Verilog代碼如下:

assign addl = hcnt; //ROM5低位地址

assign addh = vcnt; //ROM5 高位地址

VGA顏色賦值的Verilog代碼如下:

always @ (hcnt, vcnt) begin

if (vcnt > 0 && vcnt < 256 && hcnt > 0 && hcnt < 256) //劃分顯示區(qū)域

begin if (edge = = 1) {r,g,b}={10′d1023,10′d1023,10′d1023};//邊緣,顯示白色

else {r,g,b}={10′d0,10′d0,10′d0}; //非邊緣,顯示黑色

end end

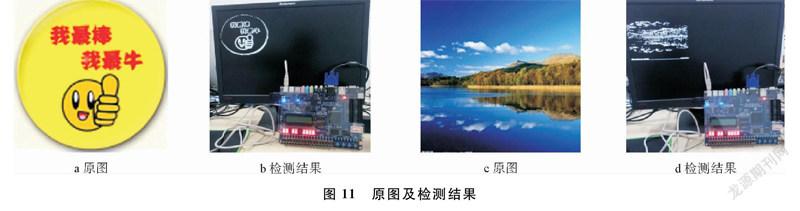

以上設(shè)計采用友晶公司的FPGA開發(fā)板DE270及VGA液晶顯示器進行硬件調(diào)試[19],開發(fā)板上的FPGA,其型號為Altera公司的 Cyclone II 系列EP2C70F896C6N芯片,利用Quartus II 130軟件對代碼進行編譯下載[20]。對256×256尺寸的兩幅圖片進行測試,原圖及檢測結(jié)果如圖11所示。由圖11可以看出,Sobel邊緣檢測算法能夠正確檢測圖像邊緣,并在VGA顯示器上顯示結(jié)果。

5 結(jié)束語

本文對Sobel邊緣檢測算法的FPGA實現(xiàn)進行研究,提出了圖像數(shù)據(jù)的并行輸入方案,相比串行輸入,處理速度提高了9倍,并采用Verilog進行編碼實現(xiàn),給出了基于ModelSim的仿真結(jié)果。同時,研究了基于FPGA的VGA顯示控制技術(shù),采用Verilog代碼,設(shè)計了顯示控制電路,并將Sobel的邊緣檢測結(jié)果送至VGA顯示電路,控制VGA顯示器顯示圖像邊緣,使處理結(jié)果更具直觀性。該設(shè)計基于Intel 公司的 Cyclone II 系列FPGA芯片EP2C70F896C6N進行了驗證,并在臺灣友晶公司的DE270開發(fā)板上進行了硬件測試,仿真結(jié)果驗證了該模型的實用性和有效性。該設(shè)計為實時、便攜式圖像邊緣檢測設(shè)備的研制提供了思路和方法。

參考文獻:

[1] 康牧.? 圖像處理中幾個關(guān)鍵算法的研究[D]. 西安:? 西安電子科技大學(xué),? 2009.

[2] 馬宇飛. 基于梯度算子的圖像邊緣檢測算法研究[D]. 西安:? 西安電子科技大學(xué), 2012.

[3] 官鑫, 王黎, 高曉蓉, 等. 圖像邊緣檢測Sobel算法FPGA仿真與實現(xiàn)[J]. 現(xiàn)代電子技術(shù), 2009, 32(8):? 109111.

[4] 高飛, 黃啟宏, 程衛(wèi)東, 等. Sobel邊緣檢測算子的改進研究[J]. 數(shù)字技術(shù)與應(yīng)用, 2016(1):? 143145.

[5] 沈德海, 侯建, 鄂旭. 基于改進的Sobel算子邊緣檢測算法[J]. 計算機技術(shù)與發(fā)展, 2013, 23(11):? 2225.

[6] 何毅, 葛日波. 關(guān)于圖像方向性邊緣檢測算法的研究[J]. 電氣自動化, 2006, 28(6):? 6870.

[7] 孫紅. 移位寄存器在實驗中的應(yīng)用[J]. 實驗科學(xué)與技術(shù), 2007(6):? 2426.

[8] 黃文舉, 陳卓佳, 李健創(chuàng), 等. Sobel與閾值相融合的邊緣檢測算法[J]. 企業(yè)技術(shù)開發(fā), 2016, 35(22):? 4647, 54.

[9] 孫百洋, 冷建偉, 趙嘉祺. 基于FPGA的Sobel邊緣檢測算法研究與實現(xiàn)[J]. 化工自動化及儀表, 2018, 45(3):? 180183, 231.

[10] 曹楊, 蘇麗娜, 沈琪, 等. 一種改進的Sobel邊緣檢測算法的設(shè)計及其FPGA實現(xiàn)[J]. 微電子學(xué)與計算機, 2012, 29(10):? 124127, 132.

[11] 李龍澍. VGA 256種顏色的顯示[J]. 計算機應(yīng)用研究, 1994(3):? 31.

[12] 杜宗展, 王振河, 馮迎春. 基于FPGA的VGA圖像顯示系統(tǒng)的設(shè)計[J]. 現(xiàn)代電子技術(shù), 2015, 38(16):? 9599.

[13] 馬思群, 李葒. VGA 彩色漢字圖像的消隱[J]. 中文信息, 1995(3):? 5860.

[14] 吳偉學(xué). 基于FPGA的圖像采集與處理系統(tǒng)設(shè)計[D]. 廣州:? 華南理工大學(xué), 2015.

[15] 朱奕丹, 方怡冰. 基于FPGA的圖像采集與VGA顯示系統(tǒng)[J]. 計算機應(yīng)用, 2011, 31(5):? 12581261, 1264.

[16] 吳婷婷, 石博雅. 基于FPGA的VGA接口技術(shù)[J]. 電腦知識與技術(shù), 2008, 3(20):? 240242.

[17] 喬建社, 楊寸明, 何灼容, 等. 基于FPGA和ADV7123的CCIR顯示接口的設(shè)計和應(yīng)用[J]. 半導(dǎo)體光電, 2010, 31(5):? 793796.

[18] 姜世杰, 余紅英, 洪永學(xué), 等. 基于FPGA的VGA接口驅(qū)動技術(shù)[J]. 電子測試, 2012(12):? 2932, 71.

[19] 惠為君, 沈兆軍. 基于Verilog的VGA控制器[J]. 計算機光盤軟件與應(yīng)用, 2014, 17(24):? 5556.

[20] 劉莉琛. QuartusⅡ11.0在《EDA技術(shù)》課程中的應(yīng)用[J]. 科技展望, 2015, 25(21):? 281.