ESD模擬器全波模型的仿真與驗證

舒曉榕,徐曉英,劉鵬宇,張成銘

(武漢理工大學 理學院,武漢 430070)

靜電放電 ESD(electrostatic discharge)的產生伴隨著瞬時大電流和強電磁場,會對電子設備或系統造成嚴重的干擾甚至損傷。為了解決實際中的靜電放電隨機性強和可重復性差的問題,根據不同情形下發(fā)生的靜電放電的主要特點,相應的靜電放電模型被建立起來,如人體模型、機器模型、人體-金屬模型等[1]。基于建立的靜電放電模型,ESD模擬器被設計和制作出來以模擬實際中發(fā)生的靜電放電現象,主要用于電子設備或系統的靜電放電抗擾度測試。

為建立靜電放電抗擾度測試通用的和可重復的基準,人們制定了一系列標準。針對人體-金屬模型,目前比較通用的標準是由國際電工委員會頒布的IEC 61000-4-2。相關標準的制定為靜電放電抗擾度測試提供了參考,也大大提高了測試結果的穩(wěn)定性和可重復性,然而由于ESD模擬器產生的電磁場可重復性差,同樣符合IEC 61000-4-2標準的ESD模擬器的測試結果會有所不同[2]。可重復性的問題也一直是靜電放電測試存在的主要問題之一。除了從實驗測試的角度提高可重復性[3-4],還可以考慮從仿真的角度解決可重復性的問題。

全波模型能夠有效模擬電磁場,因此可以建立ESD模擬器的全波模型進行靜電放電測試的仿真。

1 全波模型的建立

目前,關于ESD模擬器全波模型的研究已取得一定進展[5-7],研究人員也已將全波模型應用于相關靜電放電測試的仿真,全波模型的有效性得到了一定的驗證[8-12]。在此以建立ESD模擬器全波模型為基礎,并從PCB電磁場耦合規(guī)律的新角度進行全波模型的驗證,為ESD模擬器全波模型的實際應用提供參考。全波模型主要包括ESD模擬器和IEC 61000-4-2抗擾度測試平臺,模型的構建在CST中完成。

1.1 ESD模擬器全波模型的建立

建立的ESD模擬器全波模型是基于人體-金屬模型,并遵循IEC 61000-4-2標準。

在此以RC模塊為例進行介紹。RC模塊為150 Ω放電電阻和330 pF儲能電容,是人體-金屬模型的基本放電回路。其全波模型如圖1所示。

圖1 RC模塊全波模型Fig.1 Full wave model of RC module

圖中,儲能電容和放電電阻的基本幾何形狀參照實物大小進行建模,儲能電容的電容值和放電電阻的電阻值通過設置集總元件的電容值和電阻值進行模擬。同時,儲能電容模塊和放電電阻模塊通過集總元件連接起來,形成完整的RC模塊全波模型。

全波模型通過S參數離散端口進行激勵,激勵信號為上升時間為500 ps的階躍信號,其幅值和放電電壓大小相同。為了更好地模擬繼電器上的高電壓開關動作,S參數離散端口被放置于高壓繼電器模塊的2個觸點之間,如圖2所示。

圖2 S參數離散端口Fig.2 Discrete port of S parameter

完整的全波模型如圖3所示。為便于展示,圖中全波模型的接地帶未按照2 m的實際長度進行建模。在全波模型中,即使按照能夠產生標準放電電流的等效電路布置集總元件,仿真得到的放電電流也會與電路產生的放電電流有較大差別,這是因為3D模塊會對放電電流波形產生較大的影響。通過在全波模型各金屬部件間增加集總元件以及調整集總元件參數值,仿真得到了符合IEC 61000-4-2標準的接觸放電模式下的放電電流。同時,ESD模擬器全波模型的其他模塊也通過集總元件連接起來,并通過接地面構成完整的放電回路。

圖3 完整的ESD模擬器全波模型Fig.3 Complete full wave model of ESD simulator

使用連接放電尖端和接地面的2 Ω集總元件,來模擬IEC標準規(guī)定的用于校驗放電電流的電流靶,即全波模型仿真得到的放電電流為2 Ω集總元件上的電流。

1.2 ESD模擬器全波模型的電流驗證

全波模型能夠對放電電流和電磁場進行模擬,因此,對全波模型的驗證也需要從放電電流和電磁場兩方面進行。首先,將對放電電流進行驗證。在2~8 kV放電電壓下,全波模型仿真得到的放電電流波形如圖4所示。

大數據時代正在廣泛影響著社會、教育和發(fā)展,在諸多領域和諸多方面正掀起了變革和創(chuàng)新的浪潮,高等職業(yè)院校應該在教育改革中廣泛、全面、準確地使用大數據平臺,通過路徑創(chuàng)新、體系建設、載體建設等策略和方法,真正將大數據技術應用到高等職業(yè)院校教育改革進程之中,做到對教育變革進程、教育改革成果、教學創(chuàng)新質量的有效保障。

圖4 放電電流波形Fig.4 Discharge current waveforms

由圖可見,放電電壓和電流值呈現正比關系,表明全波模型能夠有效模擬實際ESD模擬器接觸放電模式下放電電壓和放電電流之間的正比關系。

以8 kV放電電壓下的放電電流波形為例。如圖5(a)所示,放電電流第1個峰的峰值為30.1 A,上升時間(從10%峰值至90%峰值)為(1.67-0.76)ns=0.91 ns,符合 IEC標準規(guī)定的30 A(±10%誤差)和上升時間0.7~1 ns的要求。

如圖5(b)所示,放電電流在30 ns和 60 ns處(即距離10%峰值處30 ns和60 ns)的值,分別為17.2 A和8.02 A,符合標準中規(guī)定的16 A(±30%誤差)和8 A(±30%誤差)。通過放電電流,全波模型得到了初步驗證。

圖5 8 kV放電電壓下的放電電流波形Fig.5 Discharge current waveform at 8 kV discharge voltage

1.3 抗擾度測試平臺全波模型的建立

由于靜電放電測試在IEC 61000-4-2抗擾度測試平臺上進行,因此將建立抗擾度測試平臺的全波模型,結合ESD模擬器全波模型進行了靜電放電測試的仿真。抗擾度測試平臺全波模型的主視圖和俯視圖如圖6所示。

圖6 抗擾度測試平臺全波模型的主視圖和俯視圖Fig.6 Front view and top view of full wave model of immunity test platform

圖中,對抗擾度測試平臺的全波模型進行了簡化,僅保留了水平耦合板、絕緣襯墊和接地面,連接水平耦合板和接地面的2個串聯的470 kΩ電阻采用1個940 kΩ集總元件來模擬。其中,水平耦合板為160 cm×80 cm×1.5 mm的鋁板,接地面為260 cm×180 cm×1.5 mm的鋁板,水平耦合板與接地面的間距為80 cm。在CST中水平耦合板和接地面均設置為理想導體PEC。

2 ESD模擬器全波模型的電磁場驗證

利用自制的PCB進行相關靜電放電測試,得到耦合電壓和電磁場耦合規(guī)律。對全波模型的電磁場驗證也分為對耦合電壓大小的“定量”驗證和對耦合規(guī)律的“定性”驗證。

PCB靜電放電測試分為對板放電測試和輻照效應試驗。對板放電測試是對PCB進行直接放電,以得到靜電放電在PCB上發(fā)生時的電磁場耦合情況。輻照效應試驗則按照IEC 61000-4-2標準中對間接放電測試的相關規(guī)定進行。

2.1 對板放電測試及驗證

對PCB進行了簡化以更好得到電磁場耦合規(guī)律。待測PCB基板為厚1.6 mm的FR4基板,銅厚35 μm,尺寸為100 mm×100 mm。底面為接地面,頂面布有1條軌線,軌線長60 mm,寬分別為0.635,1.27,2.54 mm;軌線末端端接 50 Ω電阻,另一端焊接SMA接口,用于測試耦合電壓,如圖7(a)所示。對板放電測試的放電點為PCB上的焊盤,且焊盤上有過孔,4組焊盤和過孔的位置在垂直距離軌線側端中點 20,40,60,80 mm 處,如圖7(b)所示。

圖7 待測PCB示意圖Fig.7 Schematic diagram of PCB to be test

測試時,將待測PCB放置于尺寸為60 cm×60 cm×5 mm的水平鋁板上,水平鋁板再放置在IEC 61000-4-2抗擾度測試平臺的絕緣襯墊上,鋁板邊沿距水平耦合板邊沿10 cm。將鋁板接地,即通過接地線連接到抗擾度測試平臺的接地面上;放電電流經過焊盤上的過孔和水平鋁板可流向接地面;放電尖端垂直于焊盤進行放電,放電電壓為2 kV,每個放電點重復放電15~20次,并取平均值進行說明。

放電時產生的電磁場會在軌線末端負載上引起感應電壓,即耦合電壓。SMA接頭的特性阻抗為50 Ω,示波器輸入阻抗設置為50 Ω時,示波器測得的電壓即為50 Ω阻抗上的電壓,文中耦合電壓測量值即為該電壓值。SMA接頭通過同軸電纜連接到示波器通道,以測量耦合電壓波形。所用示波器的型號為Agilent Infiniium DSO9254A,其帶寬 2.5 GHz,采樣頻率20 GS/s。測試前對ESD模擬器進行了校準,其放電電流滿足IEC 61000-4-2標準。

水平鋁板和待測PCB均在CST中進行建模,結合ESD模擬器和抗擾度測試平臺的全波模型進行仿真。對板放電測試的仿真如圖8所示。

圖8 對板放電測試仿真示意圖Fig.8 Schematic diagram of the simulation for discharge test to the board

由圖可見,PCB按照實物大小進行建模,使用50 Ω集總元件模擬SMA接頭和軌線端接電阻。與測量值進行比較的耦合電壓仿真值即為集總元件SMA上的電壓。不同軌線寬度下耦合電壓峰值的測量值與仿真值的比較如圖9所示。

圖9 耦合電壓峰值的測量值與仿真值的比較Fig.9 Comparison of measured and simulated peak values of coupling voltages

由圖可見,耦合電壓峰值的測量值和仿真值吻合較好,特別是耦合電壓的正峰值,且耦合電壓隨放電距離的變化趨勢基本一致。

測量與仿真得到的耦合電壓波形的吻合度也較好。寬度為2.54 mm的軌線不同放電點處的耦合電壓波形的比較如圖10所示。

圖10 不同放電點耦合電壓波形的比較Fig.10 Comparison of coupling voltage waveforms at different discharge points

以下從電磁場耦合規(guī)律的角度,對全波模型進行驗證。不同軌線寬度下耦合電壓峰-峰值的比較見表1,表中T1,T2和T3分別為軌線寬度0.635,1.27,2.54 mm。

表1 耦合電壓峰-峰值的比較Tab.1 Comparison of peak-to-peak values of coupling voltages

由表可知,隨著軌線寬度的增加,相同放電點測得的耦合電壓峰-峰值呈現出增大的趨勢,并且仿真值也表現出相同的耦合規(guī)律。這表明,在電磁場耦合規(guī)律方面,仿真結果和測量結果是相吻合的。

2.2 輻照效應試驗及驗證

輻照效應試驗按照IEC 61000-4-2標準進行。將PCB置于抗擾度測試平臺絕緣襯墊一側中心處,PCB邊沿距離水平耦合板邊沿10 cm,在水平耦合板邊沿處進行放電,如圖11所示。放電模式為接觸放電,放電電壓為2~8 kV,待測軌線為T1。為了更好驗證全波模型,PCB的放置位置還選擇了距離水平耦合板放電點邊沿20~60 cm處。同一放電電壓和放電距離重復放電15次。

圖11 輻照效應試驗配置Fig.11 Irradiation effect test configuration

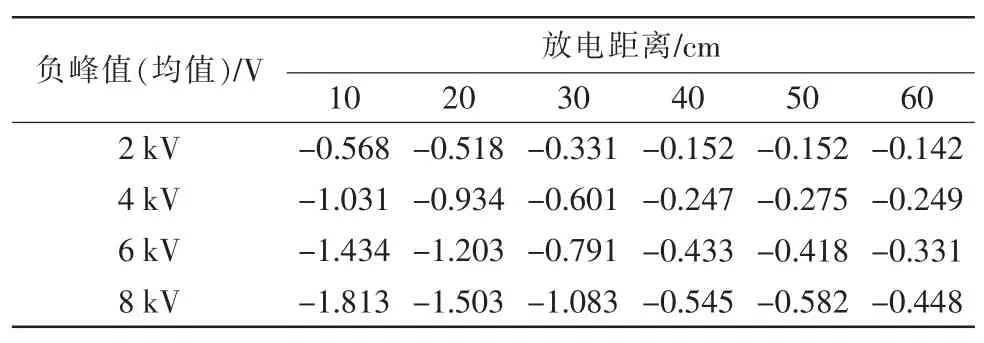

不同放電電壓和放電距離測得的結果見表2和表3。

表2 耦合電壓正峰值測試結果Tab.2 Test results of positive peaks

表3 耦合電壓負峰值測試結果Tab.3 Test results of negative peaks

由表2和表3可知,耦合電壓正峰值在20 cm處的值要大于10 cm處的值,隨后,其值開始減小,且減小趨勢變緩,但在60 cm處的值要略大于50 cm處,因此,其總體呈現出先增大,后減小,最后增大的趨勢。耦合電壓負峰值則表現出隨放電距離的增大而減小且減小趨勢變緩的趨勢。在不同放電距離處耦合電壓峰值和放電電壓基本上為正比關系。

對輻照效應試驗的仿真按照實際測試中的配置進行。其仿真如圖12所示。仿真時,Zmin邊界即接地面設為電邊界,其余邊界為open。ESD模擬器全波模型放電尖端在水平耦合板邊沿進行放電,且放電尖端垂直于水平耦合板。

圖12 輻照效應試驗仿真示意圖Fig.12 Schematic diagram of irradiation effect test

在仿真環(huán)境中,耦合電壓峰值和放電電壓呈現良好的正比關系,故在此取2 kV下的仿真結果與測量值進行比較,如圖13所示。

圖13 耦合電壓峰值的測量值與仿真值的比較Fig.13 Comparison of measured and simulated peak values of coupling voltages

由圖可見,測量值與仿真值在10 cm處的偏差較大,但在其它放電距離處,耦合電壓的測量與仿真值基本吻合,且偏差很小。然而,仿真中得到的耦合電壓正峰值和負峰值均隨著放電距離增大而減小,因此測試中耦合電壓正峰值隨距離的變化趨勢未能得到很好的模擬。

綜合對板放電測試和輻照效應試驗中的驗證結果,耦合電壓的測量值和仿真值總體吻合度較好,且對板放電測試中耦合電壓隨軌線寬度增大而增大的電磁場耦合規(guī)律,在仿真中得到了很好的驗證。由此ESD模擬器全波模型所產生的電磁場得到了驗證。

3 結語

在CST中建立了ESD模擬器的全波模型。該全波模型產生的放電電流相關參數符合IEC 61000-4-2中對標準放電電流的規(guī)定,全波模型得到了初步驗證。結合PCB靜電放電測試得到的耦合電壓和電磁場耦合規(guī)律對全波模型產生的電磁場進行驗證。結果表明,對板放電測試和輻照效應試驗中的耦合電壓測量值和仿真值吻合度整體較好,對板放電測試中耦合電壓隨著軌線寬度增大而增大的電磁場耦合規(guī)律在仿真中得到了很好的模擬。這在一方面驗證了全波模型的有效性,在另一方面,測試得到的耦合規(guī)律也通過仿真再次得到驗證。全波模型能夠獲得穩(wěn)定的結果,從仿真的角度解決了靜電放電測試的可重復性問題,并且耦合規(guī)律的相互驗證為ESD模擬器全波模型的實際應用提供了一定的參考。