一種通用信號處理模塊設計

謝 偉

(中國電子科技集團公司第十研究所,成都 610036)

傳統的電子系統設備中,各功能都是以分離式的設備完成其相應的功能,而現在的電子系統設備大多都是將多個功能作為整體進行設計,其特點就是軟硬件模塊化、通用化,達到降低成本、縮短研制周期的目的,本文介紹了一種通用信號處理模塊的設計方法。

1 總體設計

本設計以DSP作為處理器,DSP與FPGA協同工作,完成系統中頻及基帶信號的處理,模塊FPGA和DSP程序代碼可動態加載,根據主機任務需要實時配置成不同功能。同時具備FPGA和DSP代碼在線更新功能。模塊框圖如圖1所示。

圖1 模塊設計框圖

模塊主要由DSP、FPGA、LVDS高速串行總線接口組成。DSP和FPGA功能程序加載正確后,模塊的處理通道根據系統配置執行數字接收或者發送流程。在數字接收流程中,FPGA接收通過LVDS高速串行總線傳來的AD數據,經過處理后傳給DSP進行進一步處理,同時通過離散線接口和RapidIO總線接口和信道等單元交換控制參數,最終的處理結果由DSP通過RapidIO接口傳送系統。數字發送流程和接收流程相反。待處理的基帶信號由整機通過RapidIO接口送給信號處理模塊。DSP和FPGA對基帶信號進行處理后,通過LVDS高速串行總線發送給信道激勵模塊。

主機通過RapidIO總線下傳新版本程序進行FPGA和DSP代碼在線更新。主機在需要對信號處理模塊進行功能重構時,通過RapidIO總線向DSP發送功能重構指令。

2 硬件與軟件設計

2.1 LVDS高速串行總線接口電路設計

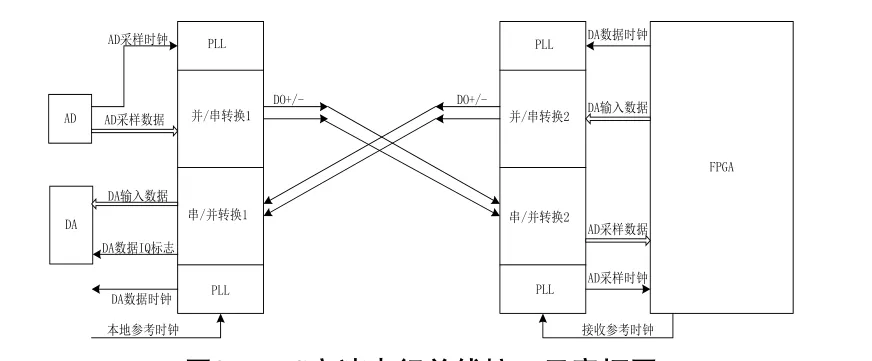

數字接收和發送流程是各功能算法對中頻信號的解調過程和對發送基帶信號的調制過程,LVDS高速串行總線接口用來傳輸AD/DA數據,其連接示意框圖見圖2。

圖2 LVDS高速串行總線接口示意框圖

AD采樣數據和采樣時鐘按照圖3所示時序送入信道模塊并/串轉換的同步并行數據輸入端,就會獲得如圖3所示的串行數據輸出Do。Do信號傳送到信號預處理模塊的某個接收通道串行輸入端。信號處理模塊產生和AD采樣頻率相同的時鐘信號送給該處理通道FPGA,FPGA將該時鐘信號作為本地參考時鐘輸入到串/并轉換的鎖相環,獲得如圖4Rout所示的并行數據輸出。DA數據的發送和AD數據的接收流程相似,傳輸方向相反。

圖3 數據發送時序

圖4 數據接收時序

2.2 程序在線更新設計

主機通過RapiIO總線向信號處理模塊DSP發送功能程序燒寫指令,并將需要更新的程序數據發送給模塊DSP。DSP收到功能程序燒寫指令后立即停止當前運行的程序,跳轉到底層管理程序,并開始執行底層管理程序。底層管理程序接收主機傳來的新程序,解析功能程序燒寫指令,然后將新版本程序固化到非易失性存儲芯片中相應的地址處,覆蓋原來的程序。功能程序更新流程框圖如圖5所示。

圖5 FLASH程序更新流程框圖

2.3 FPGA程序加載設計

FPGA上電后不能自行加載程序,要等到DSP運行底層管理程序時才開始加載FPGA程序。DSP底層管理程序通過外部存儲器接口總線從非易失性存儲芯片中讀出FPGA程序,接口控制CPLD實現DSP外部存儲器接口總線和FPGA加載端口的接口適配邏輯,然后通過接口控制CPLD寫入FPGA配置端口。DSP和FPGA加載端口之間接口電路原理如圖6所示。

圖6 DSP和FPGA加載端口之間接口電路原理圖

2.4 DSP程序加載設計

上電完成后,當DSP鎖相環穩定工作,DSP將立即啟動上電自舉流程。DSP上電自舉流程分下述三個步驟進行:首先進行底層引導程序加載,然后加載DSP底層管理程序,底層管理程序主要完成模塊硬件初始化、上電后程序加載、處理通道功能重構以及功能程序在線更新等任務,最后加載用戶功能程序。

3 結束語

本文介紹了一種信號處理模塊的硬件電路及軟件設計,能夠方便的實現應用程序的動態加載和代碼更新,開發者可以靈活的選擇DSP與FPGA的型號來實現功能。