基于Slave FIFO模式的光柵尺精度檢測系統接口程序設計

俞顯佳 ,韓 錦 ,任 湘

(1.廣東省佛山市質量計量監督檢測中心,廣東 佛山528225;2.廣東工業大學機電學院,廣東 廣州 510006)

0 引言

光柵尺在制造行業中具有極其廣泛的應用[1-3],因此光柵尺精度檢測系統對檢測增量式光柵尺產品是否滿足精度要求、保證出廠產品合格率具有重要意義。精度檢測系統的接口用于連接系統上位機和下位機兩個部分,構建兩者通信的橋梁,實現兩者之間數據傳輸。一些光柵尺生產制造公司針對其產品開發了光柵尺精度檢測的工具套件,但是這些套件往往難以兼容其他公司產品。也有研究探討設計通用光柵尺精度檢測系統[4-5],這些系統多數采用專用數據采集系統(如光柵尺數顯系統)進行數據采集,然后上位機進行精度檢測分析。但是,這些數據采集系統不能進行多任務處理,采集速度較慢,影響了精度測量效率。

為滿足系統數據傳輸的實時性、可靠性以及降低軟硬件開發難度,系統接口采用USB傳輸方式,接口芯片采用賽普拉斯公司的CY7C68013芯片[6],設計了一種基于Slave FIFO模式的光柵尺精度檢測系統的接口程序,涉及固件程序設計和上位機通信接口程序設計。

1 接口硬件設計及原理

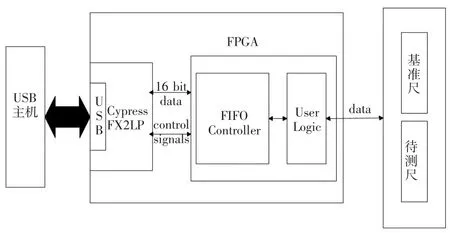

系統實現的總體方案如圖1所示。上位機軟件和FPGA通過USB接口建立連接來控制FPGA的工作方式。當上位機發送檢測命令時,固定基準尺和待測尺實時發送位置數據給FPGA,FPGA將采集的位置數據按照通信協議定義的數據格式通過USB接口發送給上位機,上位機接實時處理后得到待測尺誤差精度,并以圖形化的方式顯示誤差曲線。USB接口芯片和上位機之間的數據傳輸采用Slave FIFO模式。

圖1 系統實現方案框圖

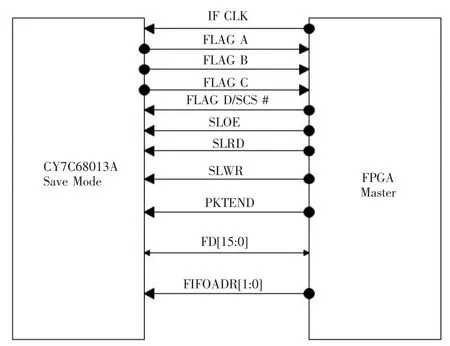

芯片在Slave FIFO模式下,外部邏輯和USB芯片之間接口引腳連接如圖2所示。接口芯片作為從設備(Slave),而外部邏輯則作為主設備(Master)。主設備可以使用8位或者16位的數據總線FD,和芯片的內部端點FIFO進行通信。外部邏輯主設備通過FIFOADR[1:0]引腳用來選擇哪個片內FIFO連接到FD數據總線上,并被外部主設備控制。芯片內部有4個FIFO可供選擇,分別對應端點2、端點4、端點6和端點8。USB接口芯片的數據總線FD是雙向的,SLOE引腳來控制輸出。

圖2 Slave FIFO模式接口引腳

2 系統接口軟件設計

2.1 固件程序設計

光柵尺精度檢測系統通過配置USB CY7C68013芯片內的多個寄存器來實現Slave FIFO工作模式。主要包括配置IFCONFIG寄存器選取工作模式和同步或異步工作方式的選取、配置接口時鐘寄存器IFCLK確定是使用內部時鐘或者是外部時鐘、配置EP2和EP6相應的寄存器EPxFIFOCFG確定數據傳輸寬度等。USB接口芯片的Slave FIFO模式是通過SLOE(Slave的輸出使能)、SLRD(Slave讀信號)、PKTEND(包結束)和 FIFOADR[1:0](FIFO 選擇)引腳來進行讀寫控制[7]。

將端點EP2和端點EP6均設置為同步Slave FIFO工作模式,EP2采用Auto Out方式傳輸數據,EP6采用Auto In方式傳輸數據。Slave FIFO模式的初始化一般在TD_Init()函數中執行,該函數在USB上電后只執行一次。程序的部分代碼如圖5所示。在該段代碼中,主要設置了EP2和EP6端點的工作模式和清空各端點數據。

2.2 上位機通信接口程序設計

圖3給出了光柵尺精度檢測系統的上位機檢測通信程序流程。上位機和USB芯片通信借助Cypress為開發者提供的軟件開發包,采用CyAPI控制函數類進行程序開發,實現系統上位機軟件和數據采集器之間的通信。

圖3 通信流程圖

本方案采用USB塊傳輸方式傳輸數據,因此上位機開發采用USB塊傳輸端點控制類CCyBulkEnd Point完成 USB塊傳輸操作。使用庫函數中的XferData()完成USB數據傳輸工作,進而建立上位機與FPGA之間的通信。

3 實驗結果與分析

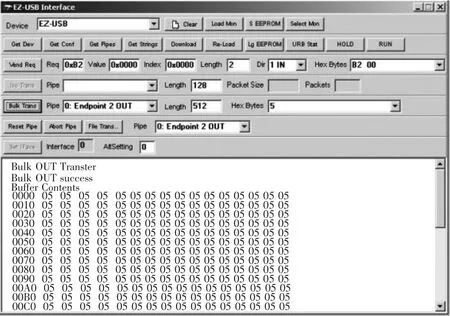

固件程序功能的測試采用了Cypress的固件調試工具EZ-USB Interface進行仿真操作,驗證USB端口能否滿足數據上傳或下發的功能。以驗證USB的EP2端口功能實現為例,仿真軟件的端點選擇EP2端點,傳輸方向為OUT,傳輸的數據為512個字節的0x05。單擊“Bulk Trans”按鈕執行塊傳輸操作,軟件工作界面顯示成功將指定數量的數據傳輸到USB端點2的緩沖區中,緩沖區的數據可被其他外圍設備讀取,說明EP2端點能滿足功能要求。如圖4所示。

圖4 塊傳輸數據發送

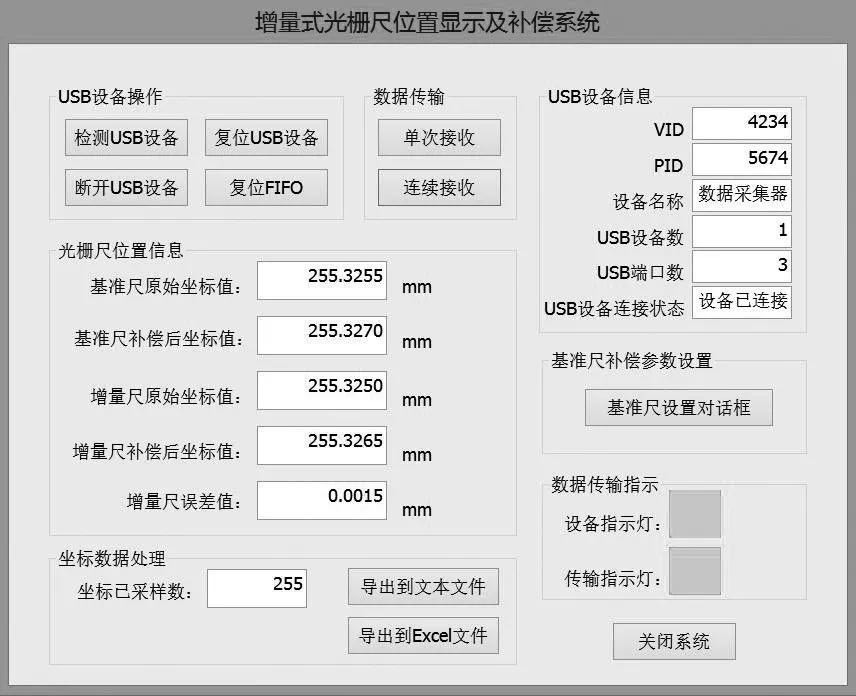

上位機初期的調試軟件實現了兩路光柵尺位置數據的接收和位置顯示功能,工作界面如圖5所示,說明上位機和數據采集模塊之間的通信能滿足通信協議要求。

圖5 調試階段主機程序界面

4 基于Slave FIFO模式的光柵尺精度檢測系統的優越性

本文采用FPGA設計一種光柵尺精度檢測系統數據采集器,實現了基于Slave FIFO模式的光柵尺精度檢測系統接口程序,具有以下優點:

(1)具有較強的時序邏輯控制能力,生成光柵尺信號采集時序和觸發激光干涉儀采集數據的脈沖,從而完成數據采集的任務;

(2)具有多任務并行處理能力,可以實現多種光柵尺產品的精度檢測;

(3)具有極小的延時誤差,保證光柵尺位置數據的同步性,嚴格控制檢測誤差。

5 結束語

本文設計了基于Slave FIFO模式的光柵尺精度檢測系統的接口程序,構建了系統數據采集模塊與上位機之間的數據傳輸通道,并通過相關實驗驗證了接口各部分設計。光柵尺精度檢測系統工作時,FPGA采集模塊能將采集的兩路光柵尺位置數據發送給上位機進行進一步的數據處理,實現了光柵尺產品精度檢測。