基于RocketIO可靠性傳輸改進方案的研究與實現(xiàn)*

曹健輝,周 剛,魯戰(zhàn)鋒

(中國電子科技集團公司第三十研究所,四川 成都 610041)

0 引 言

本項目需要在多張信號處理板卡之間傳輸實時、可靠的數(shù)據(jù),而并行傳輸需要在背板上布置多路并行信號線,設(shè)計復(fù)雜,不能滿足本項目的要求。因此,本項目采用現(xiàn)場可編程門陣列(FPGA)實現(xiàn)高速串行接口。

Xilinx公司Virtex-5 FPGA內(nèi)嵌的RocketIO GTP收發(fā)器為物理層,利用基于自定義協(xié)議的傳輸模型,實現(xiàn)兩者間單向多通道高速串行傳輸。設(shè)計時,RocketIO收發(fā)器采用一對差分線,僅需要兩根數(shù)據(jù)線,大大節(jié)省了I/O口資源,也使印制板的布線更加方便。

1 RocketIO收發(fā)器

1.1 RocketIO主要特點

Xilinx公司65 nm工藝的Virtex-5系列FPGA的LXT和SXT平臺內(nèi)嵌了RocketIO GTP(Gigabit Transceiver with Low Power)高速收發(fā)器,主要特征為[1:]

(1)每個通道收發(fā)器支持0.1~3.2 Gb/s的速率,支持5X的數(shù)字過采樣(當數(shù)據(jù)率處于100 ~500 Mb/s);

(2)收發(fā)器內(nèi)嵌發(fā)送時鐘生成電路和接收時鐘恢復(fù)電路;

(3)支持可編程差分輸出電壓擺幅和可編程預(yù)加重,用于改善信號的完整性;

(4)收發(fā)器支持直流和交流耦合方式,可兼容多種高速接口標準;

(5)片內(nèi)集成可編程差分終端電阻,50 Ω用于芯片間互連,75 Ω用于電纜連接;

(6)支持片內(nèi)多種環(huán)回測試模式;

(7)支持8b/10b編碼,可編程邊界檢測符(Comma),提供對多種標準協(xié)議的支持。

1.2 RocketIO主要組成部分

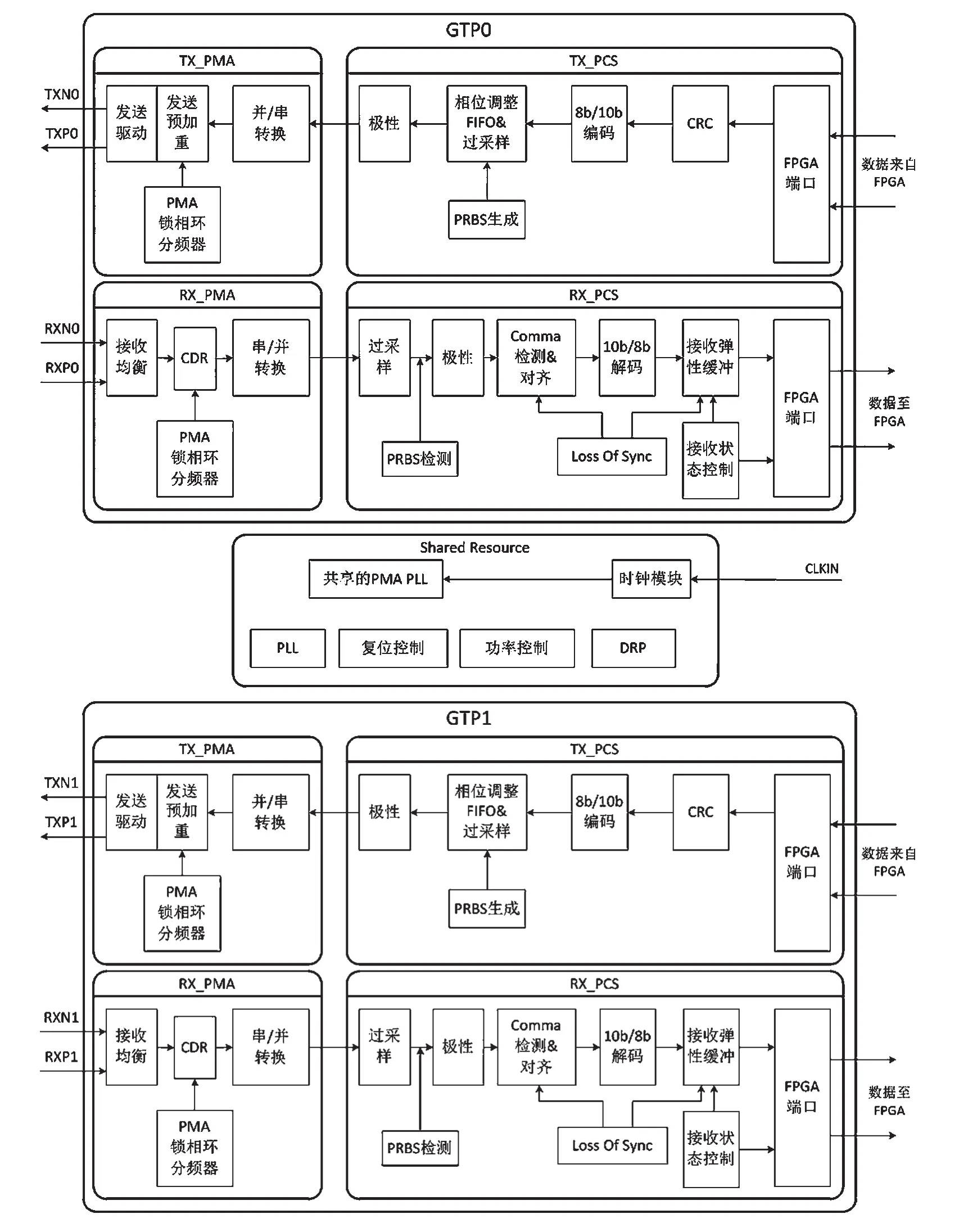

一個完整的RocketIO收發(fā)器主要包括兩個子層:物理媒介適配器(PMA)和物理編碼子層(PCS)。其中,PMA子層主要用于數(shù)據(jù)串行化和解串、高速時鐘生成及恢復(fù),包括發(fā)送預(yù)加重、接收均衡器等在線配置技術(shù),以實現(xiàn)最優(yōu)信號完整性。PCS子層主要包括Comma檢測對齊、8b/10b編解碼、CRC校驗和用于通道綁定和時鐘修正的彈性緩沖[2]。

數(shù)據(jù)串行化和解串。在發(fā)送端,收發(fā)器把輸入GTP的參考時鐘作20倍頻,作為發(fā)送線路的參考時鐘,然后將經(jīng)過編碼的并行數(shù)據(jù)轉(zhuǎn)化為串行數(shù)據(jù),從串行差分端發(fā)送出去;在接收端,時鐘恢復(fù)電路從比特流中提取出時鐘相位和頻率,恢復(fù)出接收時鐘,將串行數(shù)據(jù)解碼并轉(zhuǎn)化為并行數(shù)據(jù)送入用戶接口,以進行其他操作。

8b/10b編解碼:RocketIO收發(fā)器采用標準的8b/10b編碼機制將8位字符轉(zhuǎn)化為10位字符,保證了良好的直流平衡特性,有利于交流和直流耦合和時鐘恢復(fù)。

CRC校驗:CRC循環(huán)冗余檢測用于對被接收數(shù)據(jù)的出錯檢測,RocketIO收發(fā)器CRC循環(huán)冗余檢測邏輯直接32位產(chǎn)量CRC,被用于如Gigabit Ethernet、Fibre Channel、InfiniBand 和 User-defined等通信模式[3]。

PRBS為偽隨機二進制序列,用于測試高速串行通道傳輸誤碼率。

CDR(Clock and Data Recovery)為時鐘數(shù)據(jù)恢復(fù)電路,和接收均衡器協(xié)同負責從一個復(fù)合信號中把時鐘和數(shù)據(jù)都正確恢復(fù)出來[4]。

在Virtex-5 LXT和SXT器件中,每個GTP_DUAL模塊包含2個GTP(GTP0和GTP1)。GTP_DUAL的模塊框圖見圖1。

2 系統(tǒng)架構(gòu)

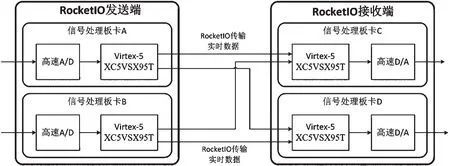

本文構(gòu)建了一個多張信號處理板卡使用RocketIO的系統(tǒng)。FPGA選擇Xilinx公司的Virtex-5系列的XC5VSX95T,邏輯密度范圍是35 000~95 000邏輯單元。采用RocketIO實現(xiàn)多張信號處理板卡之間的數(shù)據(jù)傳遞,信號處理板卡A和信號處理板卡B為RocketIO發(fā)送端,信號處理板卡C和信號處理板卡D為RocketIO接收端。信號處理板卡A和信號處理板卡B分時使用,信號處理板卡A同時發(fā)送實時數(shù)據(jù)到信號處理板卡C和信號處理板卡D,信號處理板卡B同時發(fā)送實時數(shù)據(jù)到信號處理板卡C和信號處理板卡D。本文RocketIO系統(tǒng)架構(gòu)如圖2所示。

2.1 RocketIO時鐘

GTP_DUAL的參考時鐘有以下三種方式[5]:

(1)使用外部晶振驅(qū)動GTP專用時鐘線路。當時鐘源滿足器件手冊上的指標要求時,設(shè)計具有最佳性能;

(2)通過專用時鐘走線,使用來自相鄰GTP_DUAL的參考時鐘。同一列上,時鐘布線跨線從源端到目的端,中間相隔的數(shù)量不超過3,且禁止GTP_DUAL之間時鐘交叉走線;

(3)使用FPGA內(nèi)部的時鐘(GREFCLK),雖然用法靈活多樣,但性能最差,因為會引入較大的時鐘抖動,只適合低傳輸速率、低誤碼率要求的場合。

本項目最開始使用的是FPGA內(nèi)部的時鐘來驅(qū)動RocketIO。

2.2 RocketIO協(xié)議

RocketIO支持基于標準協(xié)議的可靠通信模型和基于自定義協(xié)議的實時傳輸模型,標準協(xié)議包括Aurora、Serial RapidIO、PCI Express和 XAUI等[6]。

圖1 GTP_DUAL的模塊

圖2 RocketIO系統(tǒng)架構(gòu)

由于本項目需要實時發(fā)送引導(dǎo)數(shù)據(jù),而引導(dǎo)數(shù)據(jù)量不大,但對及時性和可靠性要求較高,因此未采用標準協(xié)議,采用的是自定義協(xié)議。本項目對RocketIO外部接口進行了封包處理,滿足了通用化和模塊化的使用需求。

3 RocketIO參數(shù)配置

3.1 設(shè)置PMA_PLL速率

PMA_PLL速率確定需遵循以下原則,并通過以下公式計算得出。

(1)PLL_DIVSEL_REF={1,2};

(2)PLL_DIVSEL_FB={1,2,3,4,5};

(3)當OVERSAMPLEMODE=TRUE或OVERSAMP LEMODE=FALSE且INTDATAWIDTH為高時,DIV=5;當OVERSAMPLEMODE=FALSE且INTDATAWIDTH為低時,DIV=4;

(4)系統(tǒng)時鐘f PLL CLK=f CLKIN*PLL_DIVSEL_FB* DIV/PLL_DIVSEL_REF,f PLL CLK必須處于1.5 ~ 3.25 GHz;

(5)一旦f PLL CLK確定,發(fā)送和接收線速率即可基本確定,具體計算公式如下:

①接收端串行時鐘速率=2*f PLL CLK/PLL_RXDIVSEL_OUT_n;

②發(fā)送端串行時鐘速率=2*f PLL CLK/PLL_TXDIVSEL_OUT_n。

3.2 設(shè)置RocketIO時鐘

由于RocketIO高低溫試驗時出現(xiàn)了傳輸誤碼的情況,因此改為外部專用晶振加硬件鎖相環(huán)作為專用時鐘源。專用時鐘經(jīng)過倍頻分頻,最后供給GTX_DUAL_TILE的時鐘頻率為200 MHz(例化時需要使用IBUFDS原語)。

在配置共享PMA鎖相環(huán)時鐘時,需要根據(jù)輸入時鐘的頻率確定共享時鐘的屬性。本系統(tǒng)中輸入時鐘為200 MHz,所以CLK25_DIVIDER需要配置為10。

本系統(tǒng)采用的時鐘配置如下。

TXUSRCLK是RocketIO發(fā)送端PCS的內(nèi)部時鐘,該時鐘的頻率由以下公式計算求得:

TXUSRCLK Rate=Line Rate/Internal Datapath Width

TXUSRCLK2是RocketIO發(fā)送端的主要同步時鐘,速率值由TXDATAWIDTH值和TXUSRCLK共同決定。

TXDATAWITH={0,1,2},其中0代表F_TXUSRCLK2=2*F_TXUSRCLK;1代表F_TXUSRCLK2=F_TXUSRCLK;2代表F_TXUSRCLK2=F_TXUSRCLK/2。

TXUSRCLK和TXUSRCLK2必須為同源時鐘,且兩者上升沿需對齊。本設(shè)計使用REFCLKOUT時鐘結(jié)合專用的分頻倍頻模塊來產(chǎn)生所需的TXUSRCLK和TXUSRCLK2時鐘。

3.3 設(shè)置復(fù)位選項

系統(tǒng)復(fù)位很重要。工程實踐中發(fā)現(xiàn),若使用恢復(fù)時鐘接收前不對GTX_DUAL進行復(fù)位,將無法正常收到數(shù)據(jù)。本系統(tǒng)復(fù)位通過以下方式實現(xiàn):將GTXRESET拉高保持120 μs,然后拉低。

4 RocketIO發(fā)送端配置

4.1 RocketIO發(fā)送接口寬度設(shè)置

RocketIO發(fā)送接口寬度由以下參數(shù)決定。當以下三個參數(shù)不同組合時,發(fā)送接口寬度也不同。

(1)INDATAWITH={0,1},其中0代表內(nèi)部數(shù)據(jù)寬度為16 bit,1代表內(nèi)部數(shù)據(jù)寬度為20 bit。

(2)TXDATAWITH={0,1,2},其中0代表發(fā)送口數(shù)據(jù)寬度為8 bit或10 bit,1代表發(fā)送口數(shù)據(jù)寬度為16 bit或20 bit,2代表發(fā)送口數(shù)據(jù)寬度為32 bit或40 bit。

4.2 RocketIO發(fā)送端編碼配置

本設(shè)計使用8b/10b編碼。8b/10b編碼是一種工業(yè)級編碼策略,實現(xiàn)方法是每個字節(jié)會有2 bit的冗余碼,以此提高數(shù)據(jù)傳輸?shù)目煽啃裕襌ocketIO自帶的8b/10b編碼不占用FPGA資源,并能降低傳輸誤碼率,因此本設(shè)計中采用了8b/10b編碼功能模塊。

設(shè)計中配置如下:

(1)TXBYPASSB10B[3:0]={0,1},其 中TXBYPASSB10B[x]=0代表相應(yīng)的字節(jié)被8b/10b編碼,TXBYPASSB10B[x]=1代表相應(yīng)的字節(jié)不被8b/10b編碼。

(2)TXENC8B10BUSE={0,1},其 中TXENC8B10BUSE=0代表相應(yīng)的字節(jié)不被8b/10b編碼,TXENC8B10BUSE=1代表相應(yīng)的字節(jié)被8b/10b編碼。

4.3 RocketIO發(fā)送端數(shù)據(jù)速率配置

RocketIO發(fā)送端數(shù)據(jù)速率配置如下:

Tx Line Rate=PLL Clock Rate*2/PLL_TXDIVSEL_OUT

當oversampling為高時,有:

Tx Line Rate=PLLClock Rate*2/PLL_TXDIVSEL_OUT*5

4.4 RocketIO發(fā)送端驅(qū)動配置

RocketIO發(fā)送端驅(qū)動有以下特點:

(1)支持不同的電壓值;

(2)支持不同預(yù)加重值;

(3)可配置終端平衡。

本系統(tǒng)采用的是輸出擺幅為1 100 mV。詳細配置如下:

(1)TXDIFFCTRL[2:0]配置值為101;

(2)TXBUFDIFFCTRL[2:0]配置值為101;

(3)TXPREEMPHASISI[2:0]配置值為101。

經(jīng)過實踐證明,部分板卡在驅(qū)動擺幅不屬于上述配置時,有些板卡常溫情況下能正常通信,有些不能正常通信;還有一些板卡在常溫下能正常,但在高低溫環(huán)境下不能正常通信。本系統(tǒng)是基于此原因開展研究和實現(xiàn)的。

5 RocketIO接收端配置

5.1 RocketIO接收端CDR配置

接收端也由PCS和PMA兩部分組成。接收端接收時鐘數(shù)據(jù)恢復(fù)電路(CDR)并從中提取出恢復(fù)時鐘,利用該恢復(fù)時鐘能很好地將接收數(shù)據(jù)提取出來。在總線傳輸過來的數(shù)據(jù)可用前,嵌入在信號中的恢復(fù)時鐘必須先被取出。

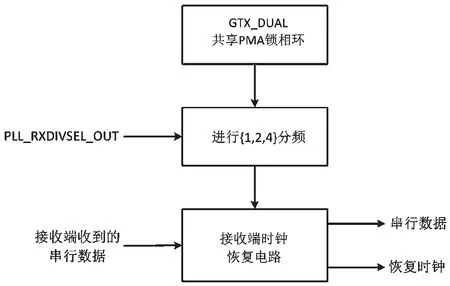

CDR電路從共享的PMA鎖相環(huán)中取出高速、分頻的串行時鐘,并矯正它的相位和頻率,直到該時鐘的轉(zhuǎn)換能夠與發(fā)過來的數(shù)據(jù)相匹配,從而產(chǎn)生正確的串行數(shù)據(jù)流。選用恢復(fù)時鐘后,必須在接收數(shù)據(jù)前先對時鐘恢復(fù)電路進行復(fù)位,具體實現(xiàn)流程如圖3所示。

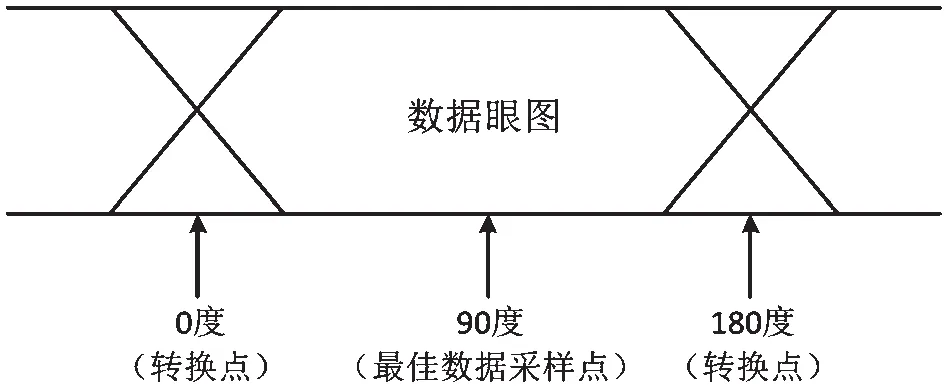

CDR能夠在進來的數(shù)據(jù)中查找數(shù)據(jù)轉(zhuǎn)換點,并用數(shù)據(jù)轉(zhuǎn)換點恢復(fù)時鐘。這些轉(zhuǎn)換點能夠輔助數(shù)據(jù)采樣時刻的選擇。為了降低數(shù)據(jù)采錯的概率,CDR應(yīng)選擇距離轉(zhuǎn)換點較遠的地方進行數(shù)據(jù)采樣,這個位置就是數(shù)據(jù)眼圖的中心,如圖4所示,此處的數(shù)據(jù)最穩(wěn)定。

圖3 CDR時鐘恢復(fù)流程

圖4 數(shù)據(jù)眼圖

5.2 RocketIO接收端參數(shù)配置

根據(jù)本設(shè)計數(shù)據(jù)的傳輸需求,本設(shè)計的參數(shù)設(shè)置如下所示。

(1)過采樣配置

因為本系統(tǒng)的傳輸速率為400 Mb/s,剛好處于過采樣要求的傳輸線速率范圍內(nèi)(150~750 Mb/s),所以O(shè)VERSAMPLE_MODE設(shè)置為TRUE,PMA_CDR_SCAN的參數(shù)設(shè)置為27’h6404040,把90°位置作為數(shù)據(jù)采樣點,達到了最優(yōu)設(shè)計。

(2)接收線速率配置

RX Line Rate=PLL Clock*2/PLL_RXDIVSEL_OUT

(3)8b/10b解碼器

8b/10b解碼器對應(yīng)的是8b/10b編碼器的逆過程,本應(yīng)用中使用了8b/10b解碼器。

(4)時鐘糾正

因本設(shè)計使用的是恢復(fù)時鐘且進行了過采樣,而過采樣模塊中包含了隱藏的buffer,可解決RXUSRCLK和RXRECCLK之間的相位差,所以不用RX elastic buffer,不用進行時鐘糾正。因為不用RX elastic buffer,所以也不用進行通道綁定。

(5)接收數(shù)據(jù)位寬配置

R X D A T A W I D T H={0,1,2},其 中TXBYPASSB10B[x]=0表示接口寬度為8 bit;TXBYPASSB10B[x]=1表示接口寬度為16 bit;TXBYPASSB10B[x]=2表示接口寬度為32 bit。

(6)接收數(shù)據(jù)時鐘配置

F RXUSRCLK配置選項如下:

① F RXUSRCLK=line Rate/16,當 INTDATA WIDTH=0;

② F RXUSRCLK=line Rate/20,當 INTDATA WIDTH=1。

F RXUSRCLK2配置選項:

①F RXUSRCLK2=2*F RXUSRCLK,當RXDATA WIDTH=0;

②F RXUSRCLK2=F RXUSRCLK,當RXDATA WIDTH=1;

③F RXUSRCLK2=F RXUSRCLK/2,當RXDATA WIDTH=2。

本設(shè)計中RXUSRCLK為RXRECCLK,RXUSRCLK2為RXRECCLK/2。

本設(shè)計接收端數(shù)據(jù)位寬配置如下,三條配置共同將接收接口位寬配置為32 bit:

(1)INTDATAWIDTH=1;

(2)RXDATAWIDTH=2;

(3)RXDEC8B10BUSE=1。

6 試驗驗證

多張信號處理板卡工作時出現(xiàn)了較高的誤碼,排除硬件故障后,對系統(tǒng)中RocketIO相關(guān)參數(shù)進行了如下優(yōu)化。

(1)優(yōu)化RocketIO時鐘使用方式。由原來使用FPGA內(nèi)部的時鐘改為使用RocketIO內(nèi)部專用時鐘走線;接收端用數(shù)據(jù)恢復(fù)時鐘代替本地時鐘進行數(shù)據(jù)接收。

(2)降低RocketIO的傳輸線速率。由原來的2 Gb/s降低為400 Mb/s(經(jīng)過技術(shù)驗證,降為400 Mb/s不影響功能性能指標)。

(3)增大了發(fā)送端輸出驅(qū)動擺幅,由原來的500 mV增大為1 100 mV。

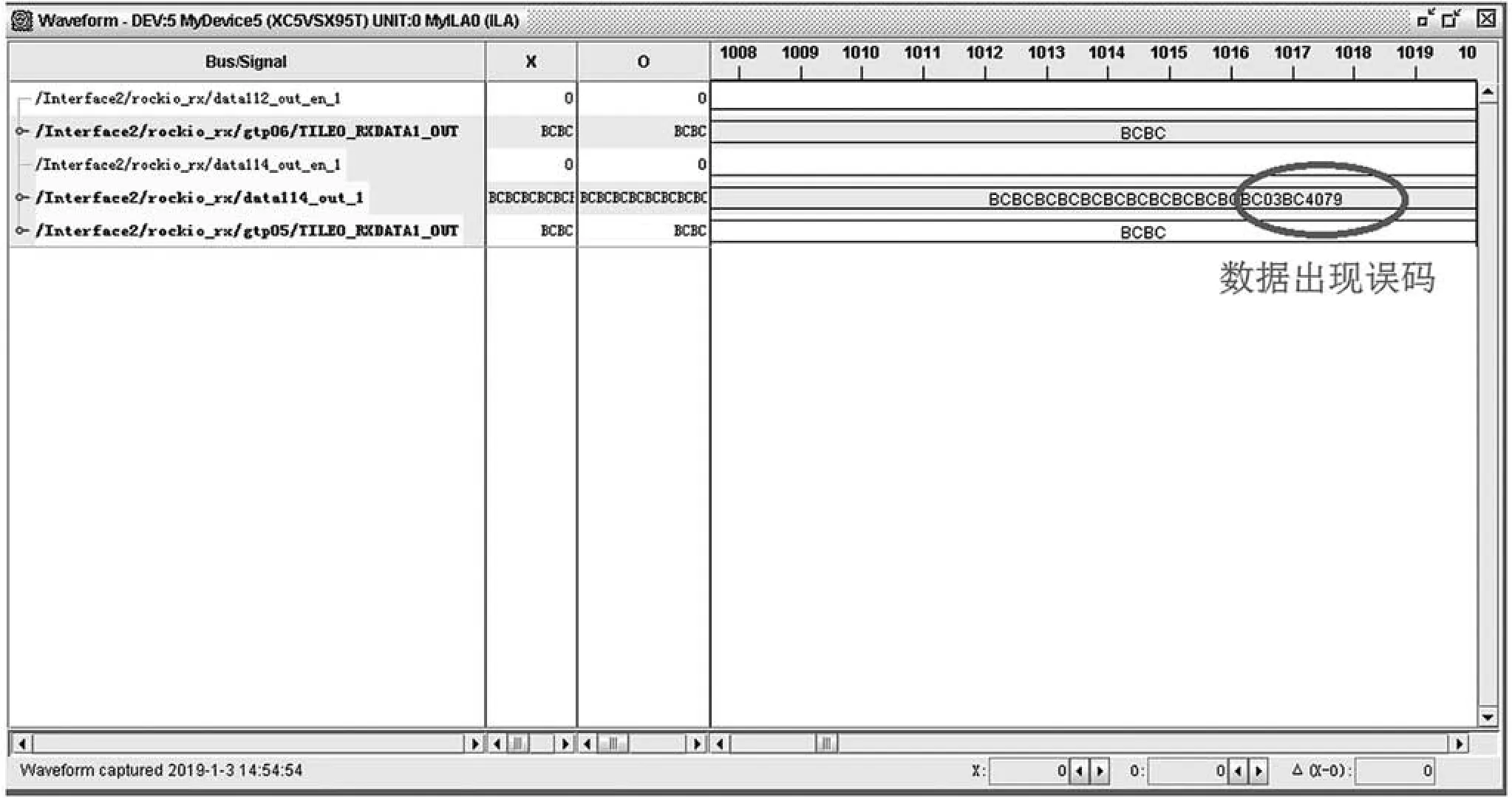

圖5為改進前的Chipscope截圖,出現(xiàn)了誤碼(BC03BC4079),正常情況下應(yīng)該只有握手碼(BCBCBCBC……)或者自定義協(xié)議報文(89ABCDEF……)。

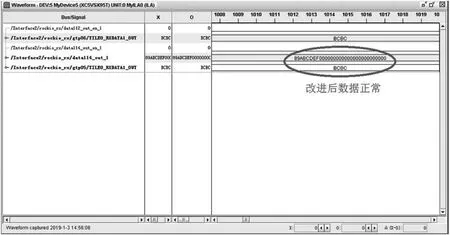

圖6為改進后的Chipscope截圖,收到的數(shù)據(jù)只有握手碼(BCBCBCBC……)或者自定義協(xié)議報文(89ABCDEF……)。

圖5 改進前Chipscope截圖

圖6 改進后Chipscope截圖

升級發(fā)送端和接收端的FPGA程序,經(jīng)過長時間常溫和高低溫(高溫工作:+55 ℃,低溫工作:-20 ℃)加電工作的試驗,RocketIO接收端未再出現(xiàn)誤碼。

7 結(jié) 語

通過優(yōu)化RocketIO時鐘使用方式,降低了RocketIO傳輸線速率,增大了發(fā)送端輸出電壓擺幅,能夠解決RocketIO出現(xiàn)較高誤碼的問題。