用于HF接收機的高純度頻率源的研制

程明,周葉華,姜建飛,2

(1.中國電子科技集團公司第三十六研究所,嘉興 314033;2.通信信息控制和安全技術(shù)國防重點實驗室,嘉興 314033)

0 引言

短波通信,這一傳統(tǒng)的通信方式,由于其通信距離遠、成本低廉、抗打擊毀壞能力強等優(yōu)點,在軍事遠程通信、無線電導航、授時系統(tǒng)、廣播等領(lǐng)域得到廣泛應(yīng)用[1-3]。盡管自20世紀70年代以來,隨著衛(wèi)星通信的異軍突起,衛(wèi)星通信在相當大的程度上取代了短波通信,但隨著人們對衛(wèi)星通信的易損耗性、耗資巨大等局限性的認知,短波通信又重新得到重視。從軍事角度而言,沒有一種單一的遠程通信可以滿足所有需求,因而世界上主要發(fā)達國家的C4ISR系統(tǒng)都部署了短波通信系統(tǒng),而且發(fā)揮著越來越重要的作用[4-7]。其中,0.3~300 kHz用于超遠程海軍通信,0.3~30 kHz多用于潛艇通信和無線電導航,500 kHz~15 MHz用于無線電廣播,2~30 MHz(HF(high frequency)頻段為主)用于三軍超視距通信、陸軍戰(zhàn)術(shù)移動通信、我國BPM授時系統(tǒng)等[8-12]。短波頻段電磁頻譜異常擁擠和復(fù)雜,因此要求短波接收機必須具有大動態(tài)的特點,而研制大動態(tài)接收機必然需要高純度頻率源作為本振,因為頻率源的相位噪聲和雜散抑制影響接收機的瞬時動態(tài)范圍和靈敏度,同時換頻速度也影響接收機的偵察搜索速度及截獲能力,因此研制高純度的頻率源是研制高性能短波接收機的關(guān)鍵技術(shù)。

1 方案原理

現(xiàn)因某機載工程需要,需要研發(fā)一款高性能大動態(tài)短波接收機,工作頻段為HF頻段:2~30 MHz。HF接收機的一本振頻率為:76.8~104.8 MHz,要求頻率源具有小步進、捷變頻、高純度等特點。下面對其詳細指標和設(shè)計方案進行論述。

1.1 主要技術(shù)指標要求

用于HF接收機的高純度頻率源的主要技術(shù)指標要求如下:

①輸出頻率范圍:76.8~104.8 MHz;

②頻率步進:1 Hz;

③雜散抑制:≥85 dB;

④相位噪聲:≤-140 dBc/Hz@10 kHz;

⑤換頻速度:≤10 μs;

⑥標頻輸入:100 MHz,0~5 dBm,相噪優(yōu)于-155 dBc/Hz@10 kHz。

⑦頻率準確度與穩(wěn)定度:同外部標頻。

1.2 方案選擇

目前,頻率合成的方法一般包括如下幾種:直接頻率合成技術(shù)、鎖相頻率合成技術(shù)(PLL)和直接數(shù)字頻率合成技術(shù)(DDS)。

①直接式頻率合成技術(shù)運用倍頻器、分頻器、混頻器、諧波發(fā)生器等部件,對頻標源進行加減乘除運算,采用濾波器取出所需的頻率;具有換頻速度快、相噪低等優(yōu)點,但體積較大,雜散抑制也很難做好。

②鎖相式頻率合成技術(shù)利用鑒相器、分頻器、環(huán)路濾波器、壓控振蕩器等器件組成,鎖相環(huán)鎖定后輸出特定頻率,具有電路簡單、成本低、體積小等優(yōu)點。

③直接數(shù)字頻率合成技術(shù)采用數(shù)字電路技術(shù)得到離散的數(shù)字序列,然后經(jīng)過D/A變換得到模擬信號,具有換頻速度快、頻率分辨率高、體積功耗小等優(yōu)點[13]。

經(jīng)過慎重考慮和評審,課題組認為該高純度頻率源采用鎖相式頻率合成技術(shù)與直接數(shù)字頻率合成技術(shù)相結(jié)合的方案比較合適,兼具低相噪、高分辨率、高雜散抑制、捷變頻等優(yōu)點。

1.3 詳細設(shè)計方案

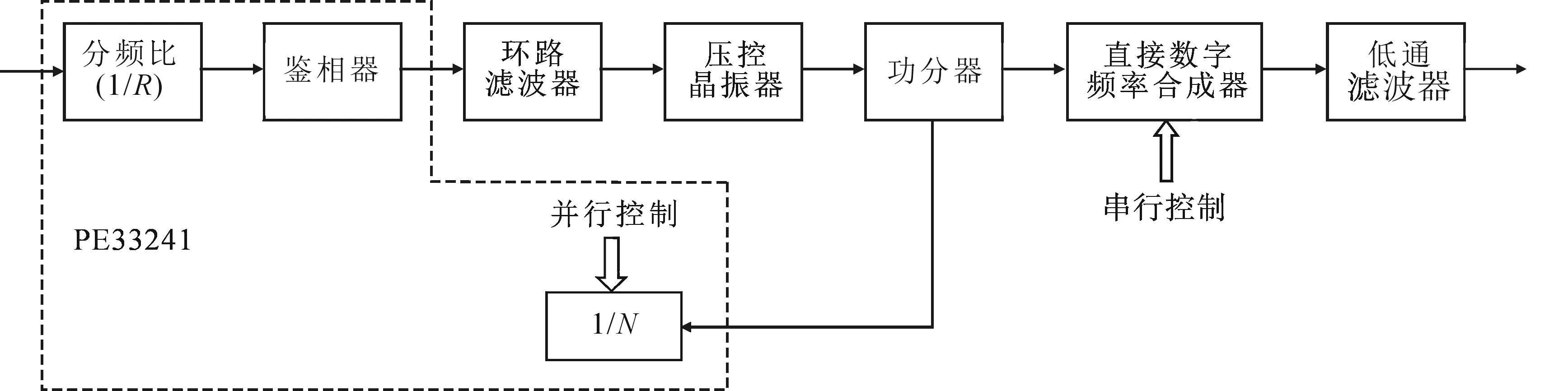

具體方案如圖1所示,該方案采用鎖相式頻率合成技術(shù)與直接數(shù)字頻率合成技術(shù)相結(jié)合的方式,主要由鎖相源和DDS兩部分組成,鎖相源用做DDS的時鐘,鎖相源頻率為900/1 000 MHz,時鐘選擇可變的原因是為了規(guī)避DDS某些雜散。鎖相源輸出頻率fCLK(即DDS時鐘)可用下面公式表示:

fCLK=N·fPD,

(1)

式(1)中,N為環(huán)路分頻比,對于該方案N為9或10;fPD為環(huán)路鑒相頻率,對于該方案fPD為100 MHz。

DDS輸出頻率fDDS可用下面公式表示:

(2)

式(2)中,F(xiàn)TW為DDS的頻率控制字,假定DDS有32 bit控制字。

該方案主要由以下單元組成:鑒相器、環(huán)路濾波器、壓控振蕩器(VCO)、放大器、功率分配器、DDS、低通濾波器等。工作原理如下,輸入標頻為100 MHz,來自超低相噪恒溫晶振,標頻分頻比R=1;鑒相頻率為100 MHz;環(huán)路分頻比N=9或10。高純度頻率的DDS頻標為900/1 000 MHz,需要100 MHz鑒相才能做到最低相噪,分頻比為9/10。AD公司的(鎖相環(huán)路)PLL,集成VCO芯片,具有體積小的優(yōu)點,在低鑒相頻率時(20 MHz以下)鑒相器基底噪聲為-230 dBc/Hz,具有較好的基底噪聲,但在100 MHz鑒相時鑒相器基底噪聲只有-220 dBc/Hz,有較大惡化,并且該類集成芯片換頻速度一般超過100 μs,做不到捷變頻。DDS集成的時鐘倍頻功能,使用的集成VCO噪聲較差,鑒相器在100 MHz是基底噪聲也不是最低,因此不適合本方案。PEREGRINE公司PE33241芯片,在100 MHz鑒相時基底噪聲仍然可以做到-230 dBc/Hz,為目前行業(yè)最低水平;并且該芯片采用并行控制,在換頻發(fā)送數(shù)據(jù)時可以做到最快速度;采用鑒相芯片PE33241自己搭建鎖相環(huán),可以選用分離的性能較好的集成VCO,從而使鎖相環(huán)輸出900/1 000 MHz具有更好的相位噪聲[14-15]。經(jīng)環(huán)路鎖定后,VCO輸出頻率為900/1 000 MHz,用作DDS的時鐘信號,通過控制DDS,輸出76.8~104.8 MHz信號。DDS輸出具有一定的時鐘雜散,因此需要加低通濾波器加以濾除,該低通濾波器的截止頻率可以設(shè)計為120 MHz。

圖1 頻率源方案

1.4 與上一代方案比較

上一代HF接收機用頻率源的主要技術(shù)指標如下:①接收機工作頻段:HF頻段;②頻率步進:10 Hz;③相位噪聲:≤-133 dBc/Hz@10 kHz;④換頻速度:≤50 μs;⑤雜波抑制:≥85 dB。

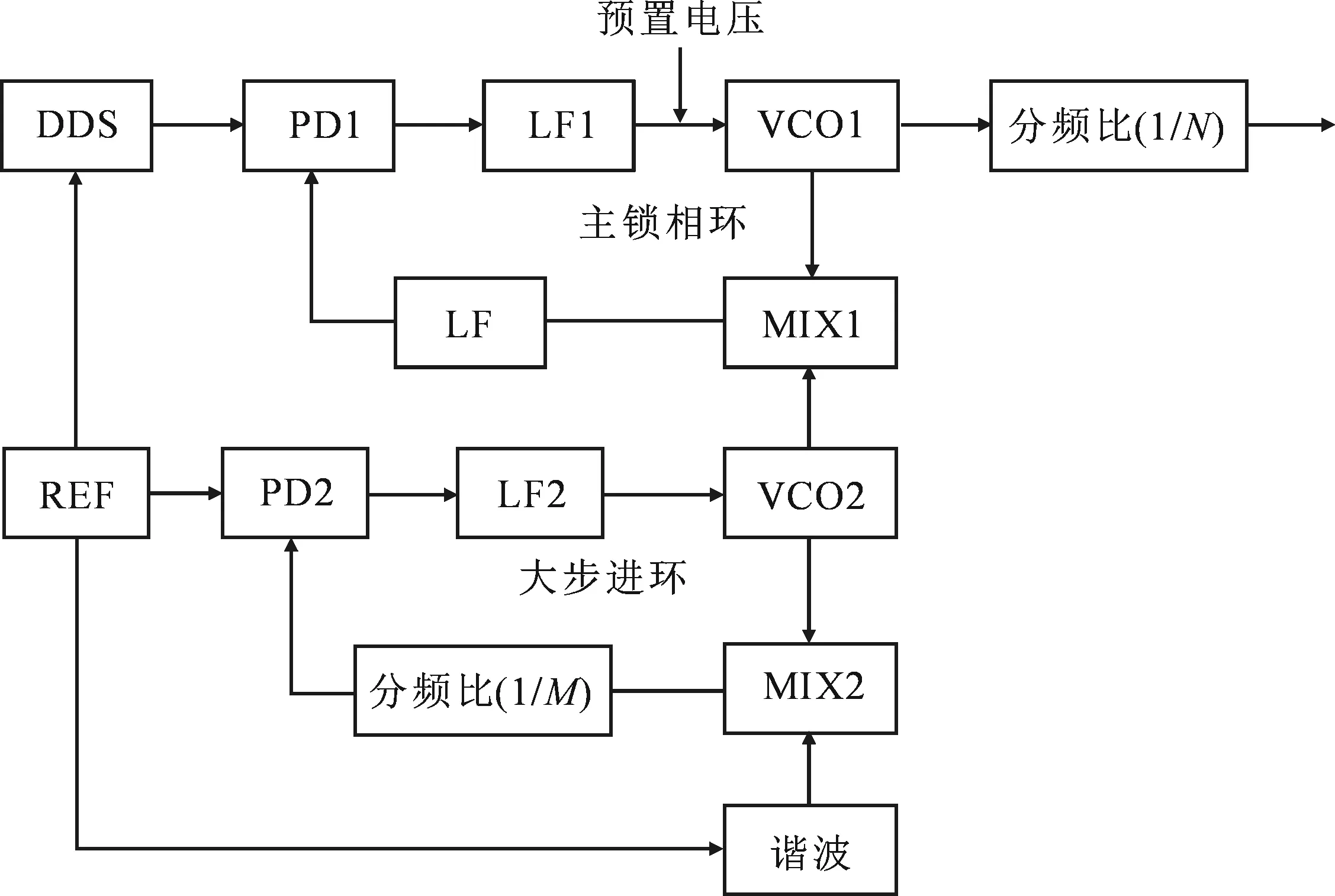

因為受制于當時的元器件水平等原因,上一代HF接收機用頻率源的方案比較復(fù)雜,基本原理如圖2所示,詳細方案可見參考文獻6[16]。該方案主要由以下幾部分組成:①標頻分配電路;②大步進環(huán)路;③梳狀譜發(fā)生器電路;④DDS小步進電路;⑤主鎖相環(huán);⑥預(yù)置電壓電路。頻標為100 MHz恒溫晶振信號,然后3分路用作各自標頻。通過梳狀譜和大步進混頻環(huán)實現(xiàn)大步進功能,通過DDS實現(xiàn)小步進,主鎖相環(huán)的VCO1鎖定后輸出相對比較高的頻率,然后再通過分頻器N除下來,得到比較高的雜散抑制和低相噪。換頻速度主要通過預(yù)置頻率電壓來實現(xiàn),但也很難做到捷變頻。

與上一代方案比較,新方案具有如下優(yōu)點:①方案大大簡化,只需一個環(huán)路和DDS即可實現(xiàn);②因為不再需要多環(huán)電路,因此可以實現(xiàn)捷變頻,這對接收機而言是個重要進步;③可以實現(xiàn)更低的相位噪聲。

1.5 DDS工作流程

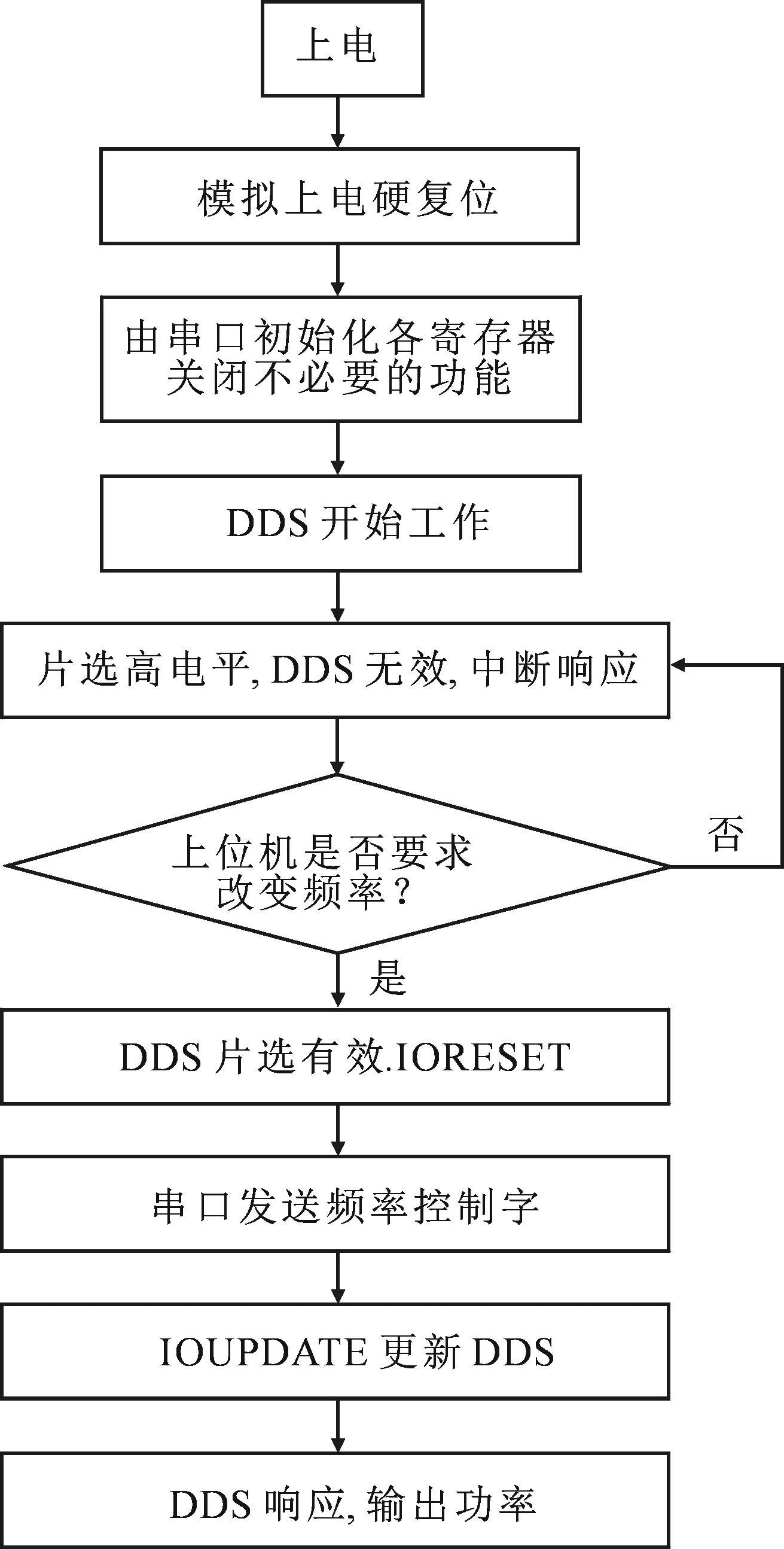

DDS是該頻率源的關(guān)鍵電路,應(yīng)對DDS工作流程特別重視,DDS工作流程設(shè)計的優(yōu)劣將決定該頻率源能否可靠的工作,本方案的DDS工作流程如圖3所示[17-18]。

注:DDS為直接數(shù)字頻率合成器;PD為鑒相器;LF為低通濾波器;VCO為壓控晶振器;MIX為混頻器;REF為頻標

圖3 DDS工作流程示意圖

2 性能分析與仿真

該方案的性能分析與仿真,是基于已知芯片性能的基礎(chǔ)上展開,因此有必要說明一下主要芯片的性能。

①PLL芯片(PE33241):整數(shù)分頻,5/6預(yù)分頻模式最大工作頻率為4 GHz,10/11預(yù)分頻模式最大工作頻率為5 GHz;鑒相器基底相噪為-230 dBc/Hz(5/6預(yù)分頻模式);最大鑒相頻率為100 MHz,標頻輸入最大為100 MHz;具有并行和串行控制模式[19]。

②DDS芯片(AD9910):最大時鐘1 GHz,具有時鐘倍頻功能,模擬輸出最大400 MHz;14位DAC,32 bit控制字,頻率分辨率0.23 Hz;最大串行控制速率70 Mbit/s;窄帶雜散抑制大于80 dB。

2.1 相噪與頻率分辨力分析

該方案鎖相芯片采用PE33241,在鑒相頻率為100 MHz時,其歸一化基底噪聲為:

Nfloor=-230+10lg100 000 000=-150 dBc/Hz@10 kHz,

(3)

那么輸出1 GHz時鐘時,環(huán)路分頻比N=10,1 GHz時鐘的相噪估算為:

NCLK=Nfloor+20lgN。

(4)

那么,NCLK=-150+20lg10=-130 dBc/Hz@10 kHz。

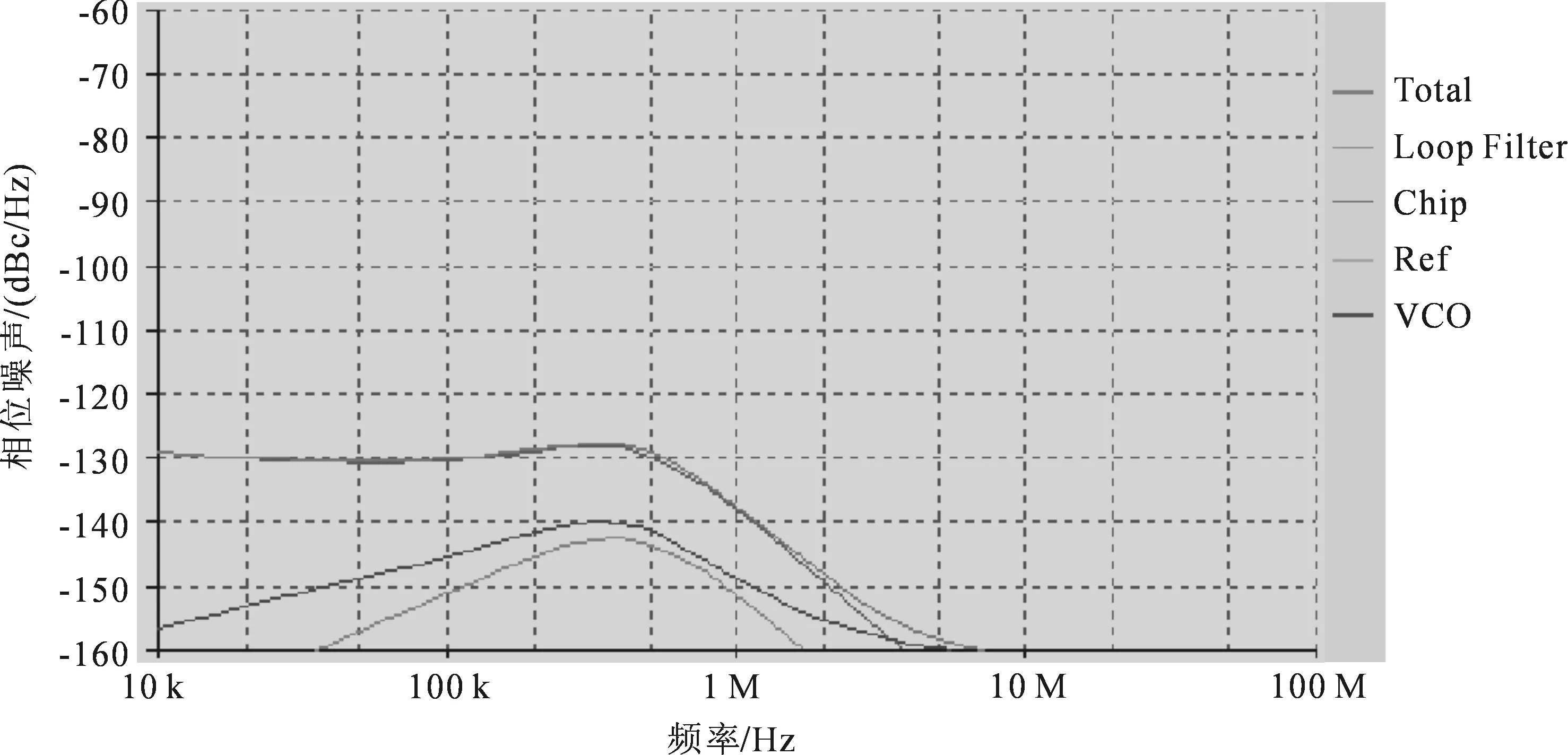

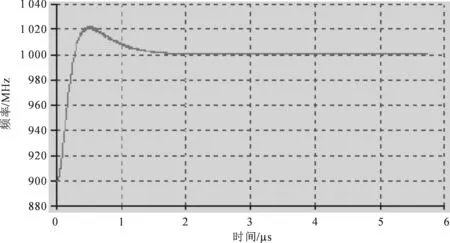

設(shè)置以下參數(shù),對1 GHz時鐘信號的相噪仿真和換頻速度如圖4和圖5所示。標頻輸入為100 MHz,標頻相位噪聲為≤-155 dBc/Hz@10 kHz。標頻分頻比R=1;鑒相頻率為100 MHz;環(huán)路分頻比N=9,N=10;環(huán)路帶寬取約1 MHz;鎖相芯片采用PE33241,采用該公司已有建模庫;環(huán)路濾波器采用有源比例4階濾波器;VCO頻率為900~1 000 MHz;調(diào)諧靈敏度38~45 MHz/V。

圖4 1 GHz相位噪聲仿真

圖5 換頻速度仿真

由以上計算和仿真可知,1 GHz時鐘信號的理論相噪約為-130 dBc/Hz@10 kHz,為DDS輸出高純度超低相噪信號創(chuàng)造了必要條件。

DDS輸出頻率的相噪可用公式(5)表示:

(5)

DDS輸出76.8 MHz時,理論相噪估算如式(6)所示:

(6)

DDS輸出90 MHz時,理論相噪估算如式(7)所示:

(7)

DDS輸出104.8 MHz時,理論相噪估算如式(8)所示:

(8)

DDS輸出的頻率分辨率計算如式(9)所示:

(9)

從以上分析和計算可知,DDS輸出信號理論相噪優(yōu)于-149 dBc/Hz@10 kHz,頻率分辨率為0.23 Hz,滿足設(shè)計要求。

2.2 換頻速度與雜散抑制分析

對于本方案,頻率源的換頻速度(T)主要由兩部分組成:時鐘切換速度(TCLK)和DDS換頻速度(TDDS)。

T=TCLK+TDDS

(10)

由時鐘切換速度仿真圖5可知,時鐘切換速度為3 μs。

由于DDS響應(yīng)極快,因此DDS的換頻速度主要由送數(shù)時間決定。由于單機設(shè)計需要,DDS只能采用串行總線控制,串行總線速率為25 MHz,DDS在進行初始化后,只需發(fā)送寄存器地址和32 bit的頻率控制字即可,因此送數(shù)時間不超過2 μs。

T=TCLK+TDDS=3+2=5 μs。

(11)

由以上分析可知,頻率源的理論換頻速度不超過10 μs,滿足捷變頻的要求[20]。

DDS輸出信號為76.8~104.8 MHz,是由DDS的時鐘(1 GHz)分頻所得,因此DDS輸出的雜散和相噪相對1 GHz都有一定優(yōu)化,DDS輸出的雜散抑制主要取決于DDS本身的雜散抑制能力,基本不受時鐘制約,因此選用AD公司14位的DDS芯片,如果布線合理的話,DDS輸出近端雜散抑制超過80 dB并不難[6]。

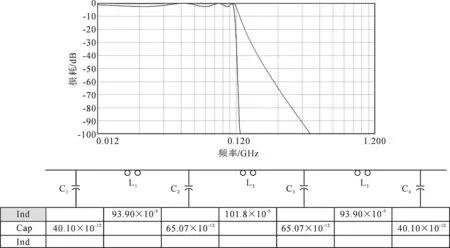

由于DDS輸出信號的遠端具有較大的雜散信號,因此需要使用低通濾波器加以濾除雜散信號,該低通濾波器的設(shè)計比較簡單,可以采用一般的七階chebyshev濾波器即可,仿真如圖6所示。

該低通濾波器的設(shè)計參數(shù)為:L1=94 nH,L2=102 nH,L3=94 nH;C1=40 PF,C2=65 PF,C3=65 PF,C4=40 PF。

由仿真可知,該低通濾波器在200 MHz以上具有超過50 dB的抑制,為了防止該濾波器在遠端有翹起情況,還可以在該低通濾波器后加一個簡單的集成LTCC濾波器,加強對1 GHz以外雜散的抑制[19]。

圖6 低通濾波器仿真圖

3 模塊系統(tǒng)集成

模塊集成在一個100 mm×50 mm×15 mm的腔體中。為了節(jié)省體積,采用4層板布線,板材為羅杰斯5880,包括VCO、分路、放大、環(huán)路濾波、DDS、低通濾波器等電路。尤其需要關(guān)注DDS電路的設(shè)計,應(yīng)注意以下幾方面:①數(shù)模電源分離設(shè)計;②上電硬復(fù)位;③寄存器初始化,后續(xù)控制只發(fā)送頻率控制字,以節(jié)省控制時間;④控制速率不可過高,波形容易畸變;⑤電源雜散應(yīng)該處理干凈,否則影響雜散抑制能力。

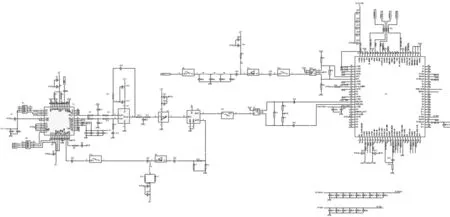

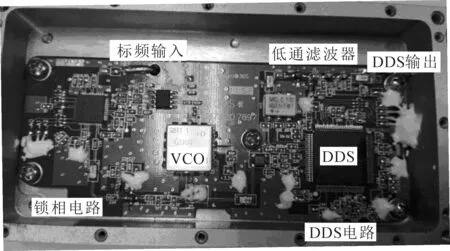

頻率源電路如圖7所示,實物見圖8所示。

圖7 頻率源電路圖

圖8 頻率源實物圖

4 模塊測試與分析討論

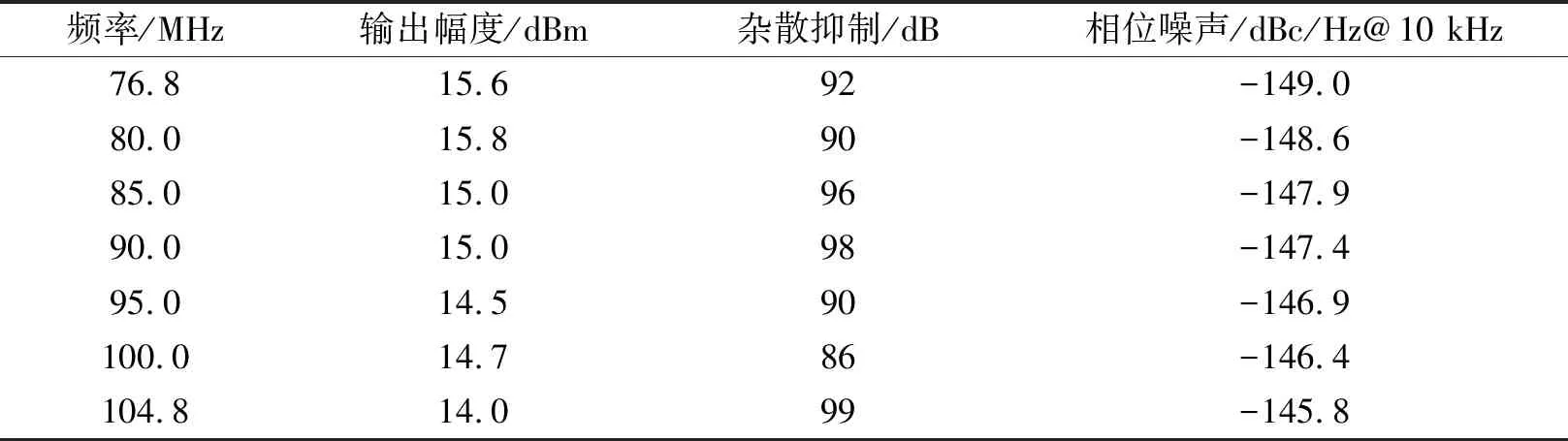

模塊加工完成后,課題組對模塊的性能進行了測試。測試性能指標見下表1所示。測試條件為:

①常溫條件下測試;

②電源輸入為+5 V/12 V;

④標頻輸入為100 MHz,幅度為0 dBm;標頻相噪:-155 dBc/Hz@10 kHz,穩(wěn)定度為≤3×10-7/d;

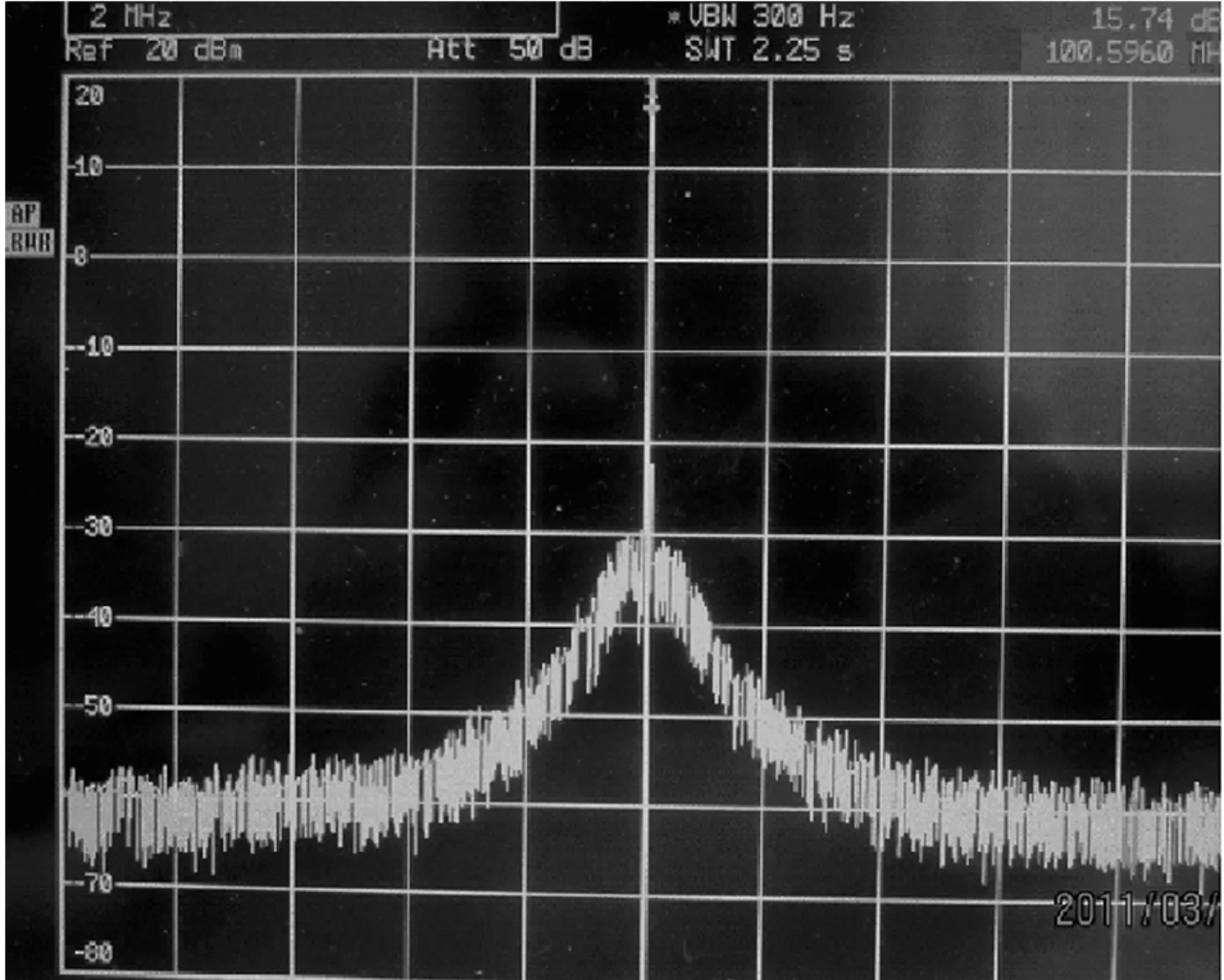

⑤采用頻譜儀測試幅度與雜散抑制,示于圖9;

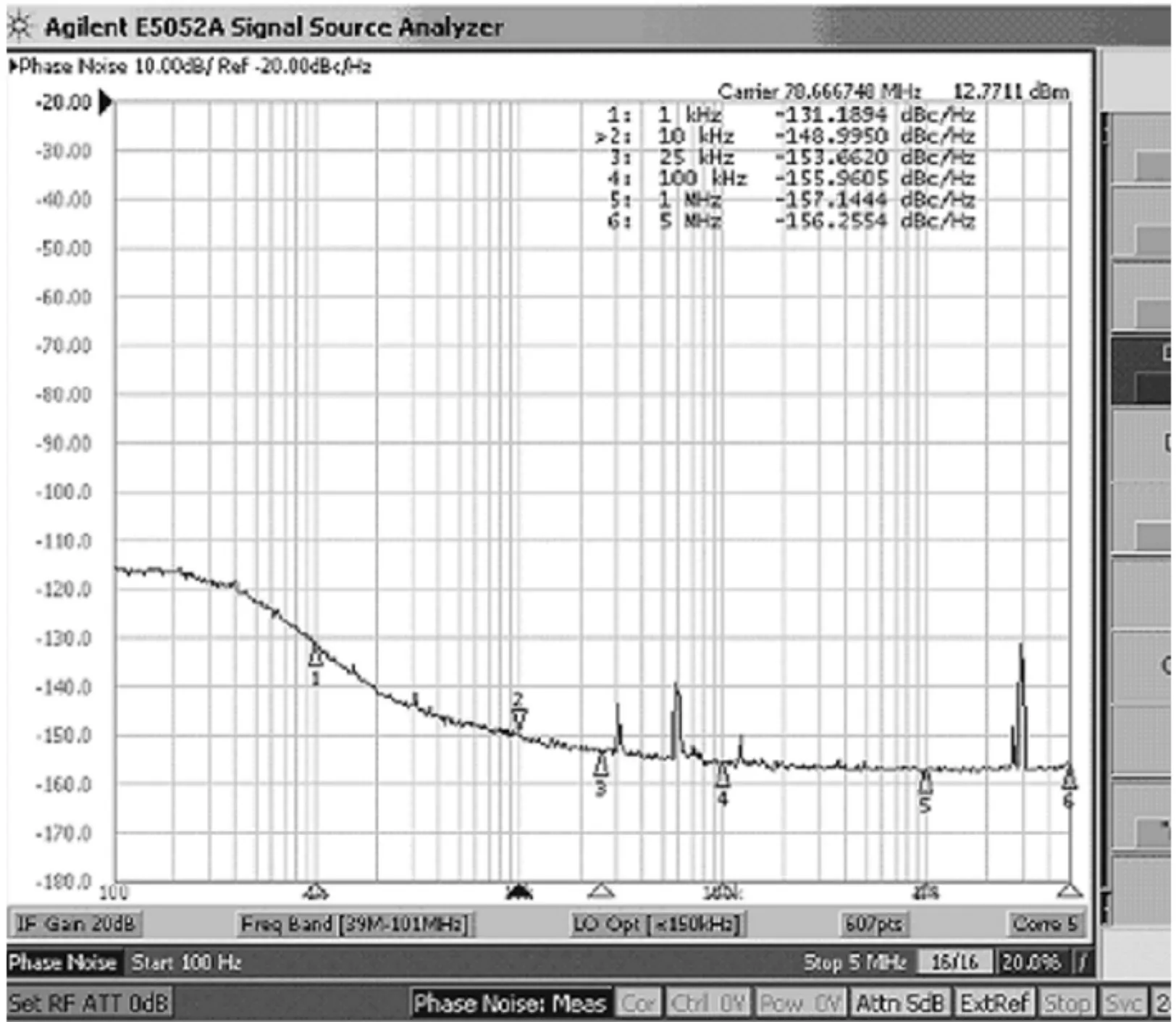

⑥采用信號源分析儀測試相位噪聲,示于圖10。

圖9 100.596 MHz雜散抑制測試圖

圖10 78.666 74 MHz相噪測試圖

表1 頻率源模塊指標測試表

測試結(jié)果為,輸出頻率范圍為76.8~104.8 MHz,輸出幅度為13~16 dBm,雜散抑制為86~99 dB,相位噪聲為-145~-149 dBc/Hz@10 kHz,頻率分辨率小于1 Hz,換頻速度小于10 μs,均滿足設(shè)計要求。在完成測試后,課題組還對該模塊進行了環(huán)境試驗,試驗結(jié)果表明該模塊具有較好的環(huán)境適應(yīng)性,為實際工程應(yīng)用奠定了較好的基礎(chǔ)。

在該模塊研制完成后,課題組認為有幾個方面值得總結(jié)和探討:

①相噪方面。實測相噪比仿真稍差,原因可能是PE33241芯片的在鑒相頻率為100 MHz時,底噪比理論值有較大的惡化,而芯片datasheet上又沒有明確說明,這種情況在設(shè)計時應(yīng)引起重視。

②雜散方面。為了降低雜散對靈敏度的影響,要求DDS輸出在接收機一中頻的頻率(74.8 MHz)雜散抑制大于110 dB以上,這對于DDS而言是非常難的。如果批量生產(chǎn)時,該頻率點雜散抑制超標,我們可以改變時鐘的方式規(guī)避,此時要注意的是時鐘切換速度必須要快。

③上電初始化。當該模塊用在不同的單機和系統(tǒng)上時,課題組發(fā)現(xiàn)有上電初始化失敗的情況,經(jīng)過測試分析,發(fā)現(xiàn)原因為不同的系統(tǒng)和單機電源上電情況不同,在電源還沒完全穩(wěn)定的情況,就貿(mào)然給DDS進行了初始化,導致初始化失敗。解決辦法就是在單機上電后增加1~2 s延時,再進行DDS初始化,后面問題不再復(fù)現(xiàn)。

④數(shù)據(jù)計算方面。應(yīng)選用高位數(shù)DSP進行計算,保證頻率控制字計算精度,才能保證頻率分辨率。另外,應(yīng)優(yōu)化浮點數(shù)計算算法,提高計算速度,否則會影響控制速度。

⑤通用性方面。該頻率源時鐘頻率較高,因此DDS可以輸出200 MHz以內(nèi)的高質(zhì)量信號,輸出范圍可以有比較大的拓展空間,可以滿足不同體制HF接收機的需求,具有較高的通用性。

⑥相噪優(yōu)化方面。如果要想DDS輸出更好相噪的信號,可以對DDS的時鐘信號進行改進,時鐘考慮采用100 MHz直接倍頻的方式得到,那么1 GHz時鐘相噪可以有3~4 dB的提升,但因為受制于DDS的基底噪聲(-151 dBc/Hz@10 kHz)限制,也很難具有大的提升空間。同時,靈活性和通用性會有一定的損失[20-21]。

⑦頻率分辨率優(yōu)化。該方案采用32 bit的AD9910,所以頻率分辨率為0.23 Hz。因為目前單機的標頻為恒溫晶振,穩(wěn)定度為≤3×10-7/d,所以頻率分辨率可以滿足目前單機的使用需求。但隨著系統(tǒng)逐漸采用高穩(wěn)定原子鐘作為時標,0.23 Hz的頻率分辨率將不再滿足要求。我們后續(xù)打算對該DDS電路進行改進,DDS擬采用AD9912芯片,該DDS芯片頻率控制字達到48位,理論分辨率可以做到3.5 μHz。

⑧換頻速度優(yōu)化。在發(fā)送順序方面還可以做更進一步優(yōu)化,可以考慮先發(fā)送鎖相環(huán)的控制字,讓其進入鎖定狀態(tài),其鎖定過程大約需要3 μs,在鎖定過程中,可以再發(fā)送DDS控制字,這樣可以節(jié)省DDS的發(fā)送時間2 μs,因此總換頻速度可以控制在3 μs左右。

⑨國產(chǎn)化率方面不足。該設(shè)計的核心芯片為PE33241和AD9910,都為進口器件,因此在國產(chǎn)化率方面存在不足。隨著國家在芯片方面進行的戰(zhàn)略性投資, 13所及一些民品公司已經(jīng)有一些射頻與DDS芯片產(chǎn)品問世,相信在不遠的將來,我們國家也能生產(chǎn)此類高性能的芯片。

5 結(jié)語

本文介紹了一種用于HF接收機的高純度頻率源的研制,給出了設(shè)計原理和仿真,并進行了模塊系統(tǒng)集成和電路加工,課題組對模塊進行了實際測試。測試結(jié)果表明,該頻率源模塊的輸出頻率、相位噪聲、雜散抑制、頻率分辨率、換頻速度等指標均滿足設(shè)計要求;主要指標較上一代短波接收機有了大幅提升,具有如下幾方面的優(yōu)點:

①更低相噪。相噪可以做到優(yōu)于-145 dBc/Hz@10 kHz,相噪優(yōu)化了10 dB;

②更快速度。換頻速度小于10 μs,換頻速度提升了4倍;

③更具通用性、靈活性,輸出頻率范圍可進行大范圍拓展,而性能不會有大的下降;

④模塊化,方便批量生產(chǎn)和調(diào)試,方便移用和維修;

⑤體積和功耗更小,只有原來的約1/5;

⑥成本也有比較大幅度的下降。

當然該頻率源也存在國產(chǎn)率不高方面的缺點。由于本文包含課題組的一些實際工作經(jīng)驗和想法,鑒于課題組成員的水平和認知局限,本文難免存在不當之處,敬請各位同行、專家不吝賜教并給予指正。