設備級的高精度時間同步

黃華明

【摘要】??? 本文介紹了在精確時間同步系統中,為實現設備與設備間高精度的時間同步而提出的一種新的接口設計方案。該方法不但大幅度提高同步精度,而且簡化了硬件接口設計。此外,對于將來更高精度的升級擴展,長距離傳送和強干擾環境等特定場景的時間同步應用也具備巨大的優勢。

【關鍵詞】??? PTP??? 1PPS??? ToD??? RS422??? 1000BASE-X

一、引言

在PTP(Precise Time Protocol)分布式系統中,我們需要在本地設備之間同步ToD(Time of Day)并測量PTP系統的準確性。ITU-T G.703和CCSA都定義了1PPS/ToD接口,接口提供串行ToD時間信息傳送和秒脈沖1PPS(One Pulse Per Second)信號作為相位指示。物理連接器采用RJ-45連接器,其電氣特性符合RS422標準。

本篇文章主要闡述當前采用的RS422接口技術所具備的局限性,以及采用新型1000BASE-X接口傳輸1PPS/ToD原理和新設計在各項性能上的大幅提升。

二、當前的接口實現方案

當前的1PPS/ToD接口設計符合G.703和G.8271中規定的基于ITU-T V.11的相位和時間分配接口以及相關的CCSA/CMCC標準。

外部接口采用RS422接口進行1PPS和ToD信息傳輸,采用RJ-45物理連接器,其電氣特性符合RS422標準的要求。

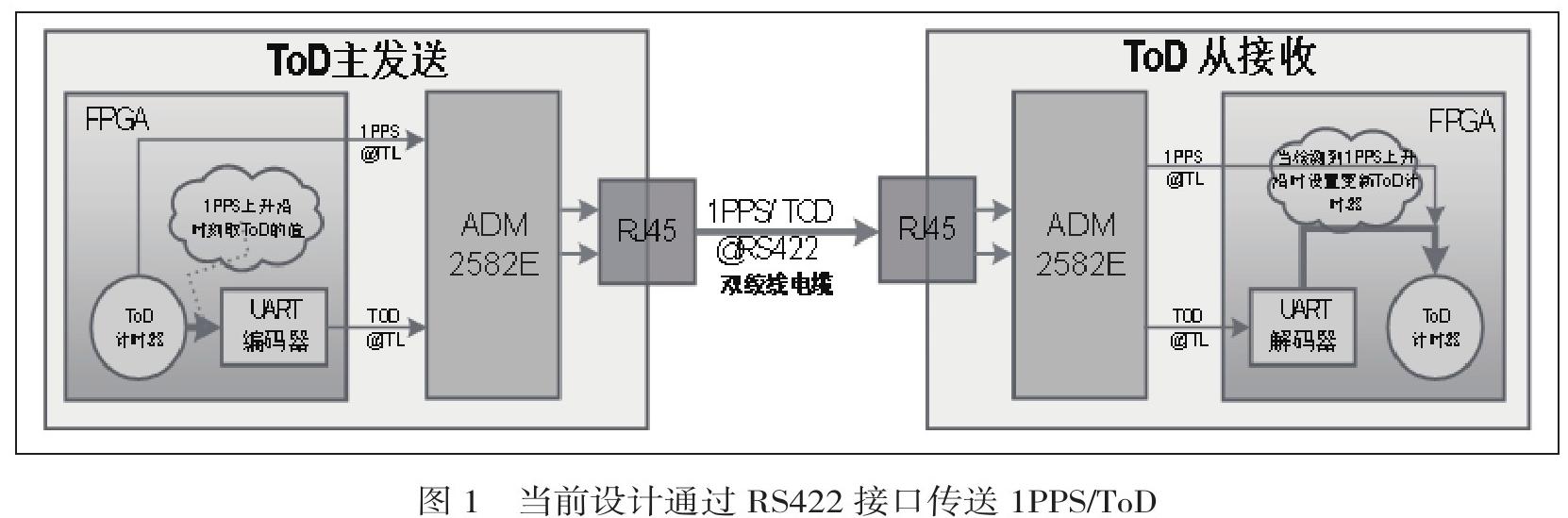

FPGA引腳輸出1PPS/ToD使用單端LVTTL電平。 在FPGA輸出到面板接口時,電平轉換芯片ADM2582E將單端LVTTL電平轉換為差分422電平輸出到面板。 同時,芯片將面板輸入1PPS/ToD的差分422電平轉換為單端LVTTL電平,并將其發送到FPGA。 具體實現框圖如圖1:

由于采用RS422標準1PPS/ToD接口,插入電平轉換芯片ADM2582E,該電平轉換芯片使得1PPS產生較大的上升時間(最大可達15納秒),這將會引入很大的1PPS采樣誤差,達到數納秒級別的誤差。同時,采用不同批次的電平轉換芯片ADM2582E,當轉換電平時,1PPS信號延遲的差異會造成最終1PPS采樣時間點的差異,嚴重影響采樣1PPS的一致性,甚至可達到10納秒以上的差異。

此外,即使同一電平轉換芯片ADM2582E,隨著溫度等環境因素的變化,經過ADM2582E芯片的1PPS信號延遲也會發生變化,這也會導致最終1PPS采樣時間點的差異,嚴重影響采樣精度,誤差可達數納秒。

綜上所述,采用RS422標準傳輸1PPS/ToD,由于物理特性和接口標準的局限性,在時間同步系統中會產生數十納秒的同步誤差,雖然可以滿足早期同步系統的要求,其允許微秒或數百納秒精度的同步誤差要求。但對于目前納秒級的高精度同步系統,這是不可接受的。

除了同步精度較差以外,使用該接口傳輸1PPS/ToD還不利于惡劣環境和長距離傳輸以及強電磁干擾等場合。同時,也很難升級擴展到更高精度的同步系統應用中。

三、改進型設計方案

在改進型設計中,采用1000BASE-X接口,1PPS和ToD信號被組合編碼為以下時序:

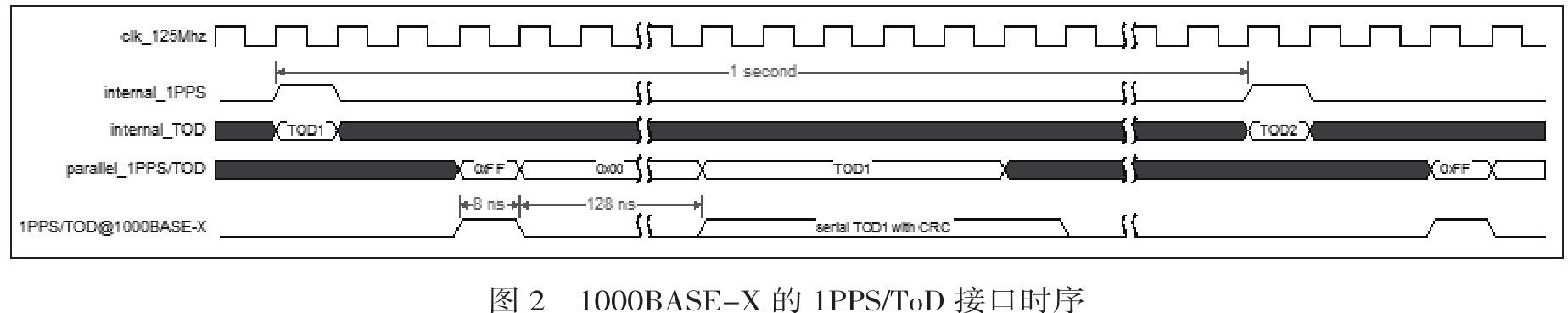

從圖2的時序圖可以看出,在空閑狀態下,信號線全部為0。當PTP系統產生125Mhz的1PPS定時信號時,FPGA內部鎖存當前系統的ToD時間值。ToD主發送測內部8ns寬度的125Mhz 時鐘下的1PPS脈沖,在SERDES串行數據線上表現為連續輸出的8個納秒高電平。 在連續8納秒高電平之后,插入128納秒低電平作為間隔。在該間隔之后,80位系統時間ToD信息和8位CRC校驗值按照順序被串行編碼到SERDES數據線上。

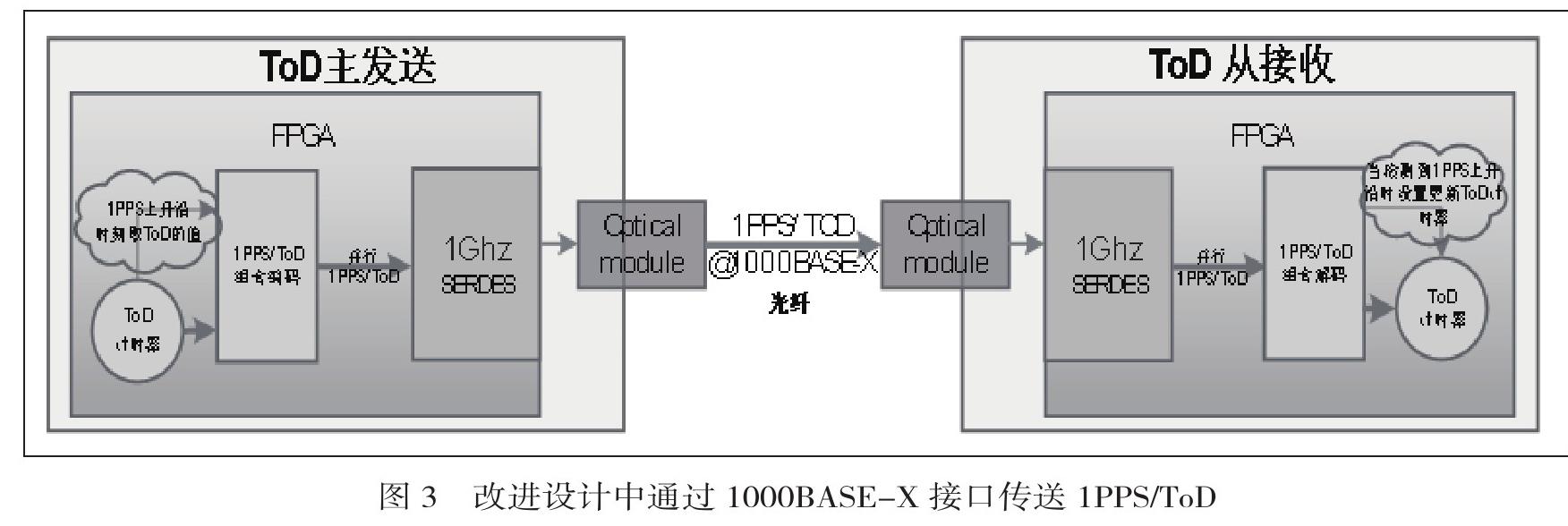

改進型設計框圖如下圖3:

改進設計中使用1000BASE-X作為實現的示例。在ToD的主發送側,FPGA中的1PPS/ToD組合編碼將1PPS和80位的ToD信息組合成單個串行數據線,通過FPGA內嵌SERDES硬核將數據串行化為1Ghz信號,并使用差分LVDS電平輸出到光模塊接口。

在ToD的從接收側,1Ghz串行數據流被解串并行化,但未被FPGA中內嵌的SERDES硬核進行原始數據的比特流對齊。通過從前一級輸入的并行1PPS/ToD,在1PPS/ToD組合解碼中,通過將代表1PPS的連續8個‘1的0xFF比特對齊,來恢復后續ToD信息,并獲得1PPS和接收系統采樣時鐘之間的相位差值phase_diff。

使用恢復的1PPS和ToD信息校準從接收側的本地ToD計時器。更新校準時,補償先前獲得的相位差phase_diff,這樣可以使同步校準精度達到1納秒。

為了滿足更高精度的時間同步要求標準,可以使用更高頻率的SERDES接口。例如10G或100G,代替1Ghz接口。只要通過改變接口速率而不改變內部功能實現,就能提高同步精度至一個甚至幾個數量級。因此,通過提高1PPS信號的SERDES檢測精度,可以很容易地升級到更高的時間同步精度。

使用上述改進型接口設計方案,可使本地設備之間的ToD系統同步精度和PTP系統的測量精度提高一個數量級以上,并且可以提供具有更高精度的可擴展升級設計。為5G新標準要求中的超高精度時間同步提供了強有力的保證。

四、結果及分析

使用1000BASE-X千兆光纖接口代替RS422接口作為1PPS/ToD信號傳輸接口。千兆光模塊直接連接到FPGA的SERDES引腳,將1PPS/ToD信息串行編碼為單條數據線,并使用LVDS差分電平直接通過千兆光纖接口傳輸。

與原有RSS422接口技術相比,主要優點如下表:

五、結束語

本文所描述的通過新型傳送接口實現的設計方案,將1PPS和ToD信號合二為一,降低硬件實施成本;同時采用具有可擴展工作頻率的硬件接口有助于擴展到更高精度的時間同步;設計使用光信號接口代替電信號接口傳送1PPS/ToD信號,可應用于更多實際場景,如長距離和強電磁干擾環境等。

參? 考? 文? 獻

[1] 中國移動高精度時間同步1PPS+ToD時間接口規范,中國移動通信有限公司發布,2010年

[2] ITU-T G.703. Physical/electrical characteristics of hierarchical digital interfaces, Apr,2016.

[3] ITU-T G.8271/Y.1366. Time and phase synchronization aspects of packet networks, Jul,2016.

黃華明,1976年9月,男,FPGA研發工程師,高級職稱。長期從事固網傳輸芯片開發。