基于FPGA動態重構的卷積神經網絡硬件架構設計*

何凱旋,袁 勛,陳 松

(1.中國科學技術大學 微電子學院,安徽 合肥 230026; 2.中國科學技術大學 微納電子系統集成研究中心,安徽 合肥 230026)

0 引言

卷積神經網絡是一種多層神經網絡,通常由卷積層、池化層和全連接層組成。在圖像處理領域,卷積神經網絡主要用于對輸入圖像的特征進行提取分類,以識別位移、縮放與其他形式扭曲不變的二維圖形,比如應用于手寫數字與車牌的識別[1-2]。ImageNet數據集的推出,使卷積神經網絡在計算機視覺應用方面取得巨大成功,更加推動了卷積神經網絡的發展[3]。

卷積神經網絡具有很高的并行性,其間的運算操作由大量的乘法與加法組成,是一種運算密集性很高的網絡。FPGA設計靈活,大量的片上資源可以滿足卷積神經網絡的運算要求,不僅可以充分發揮卷積神經網絡的并行性,還可以有效降低設計成本。

隨著卷積神經網絡的發展,其深度和復雜度都在上升。從大量的前人工作中可以發現,卷積神經網絡識別的正確率與其層數規模基本成正比,在硬件實現的階段,便對FPGA的片上資源需求提出了更大的挑戰。因此,本文提出動態重構的設計方法來降低卷積神經網絡所需的硬件資源。

基于FPGA的動態重構技術就是利用“時分復用”的思想,將FPGA的配置區域劃分為靜態區域與重構區域。在重構控制器的控制下,重構區域從存儲器中加載不同的配置文件,經過一定的配置時間,重構模塊加載完成,之后重構區域可以開始執行不同的邏輯功能。如果重構區域的配置時間大于兩個重構模塊使用時間間隔,便會延長系統的執行時間,反之,便可以隱藏在執行時間中。當一個重構區域重配置時,FPGA內部其他區域的正常運行不受影響。通過應用FPGA可動態重構的特性,可以實現FPGA上資源的“時分復用”,對部分模塊進行動態重構,提高了系統的靈活性,充分利用了FPGA的硬件資源,節約了成本。動態重構技術具有很高的拓展性,可以應用于航天、國防等眾多領域[4]。

1 基本原理

1.1 卷積神經網絡的基本原理

卷積神經網絡通常由卷積層、池化層與全連接層組成。卷積層與池化層交替連接構成卷積神經網絡的前幾層,一個或者幾個全連接層構成卷積神經網絡的后幾層,作用是對前面的網絡層產生的特征進行識別與分類。通過局部連接和神經元的共享權重,可以大大減少卷積神經網絡所需的參數,且卷積神經網絡的執行效率高于全連接神經網絡。結合池化層的功能,使得圖像特征具有較好的平移、縮放和扭曲不變性[5]。

本文使用的優化Lenet-5手寫體識別卷積神經網絡是一個典型的多層感知網絡[1],由三層卷積層(C1、C3、C5)、兩層池化層(S2,S4)與一層全連接層(F6)組成,如圖1所示。

圖1 優化的Lenet-5網絡

其中,C1層為單卷積層,實行卷積運算,有6個卷積核,輸入1幅32×32的圖像,輸出6幅28×28的特征圖像。S2層為2×2的平均池化層,輸入6幅28×28的特征圖像,輸出6幅14×14的特征圖像。S2與C3之間有一個激勵層。C3為卷積層,輸入6幅14×14的特征圖像,輸出16幅10×10的特征圖像,每個輸出由若干個輸入圖像卷積后相加再加偏置得到。S4層為2×2 的平均池化層,輸入16幅10×10的特征圖像,輸出16幅5×5的特征圖像。C5為卷積層,輸入16幅5×5 的特征圖像,輸出120幅1×1的特征圖像。F6為全連接層,輸入為1×120的特征圖像,輸出為1×10的特征圖像,值最大的即結果。

卷積層生成的輸出特征圖可由(1)式計算得到:

Aki=f(Wki?Aki-1+bki)

(1)

其中,Aki表示第i層的第k個特征圖,第i層的第k個卷積核的特性由權重矩陣Wki和偏置項bki決定。

卷積神經網絡由于其自身算法的運算密集性,在硬件實現階段對LUT、DSP等資源提出了很高的要求,所以降低卷積神經網絡的硬件資源占用量勢在必行。

1.2 FPGA動態重構的基本原理

基于FPGA動態可重構技術就是利用“時分復用”的思想,將設計從一個純空間的數字邏輯系統轉化為在時間、空間混合構建的數字邏輯系統。這種技術使FPGA資源利用率成倍提高,實現系統功能所用的硬件規模大大下降[6]。

本文采用模塊化設計方法實現FPGA的動態部分重構,其原則是將重構邏輯和靜態邏輯劃分到不同的區域中。根據要求從重構區域中替換需要更改的模塊,從而實現動態重構的功能,如圖2所示。

圖2 模塊化設計示意圖

動態重構的流程需要使用動態重構控制器來進行控制。動態重構控制器接收靜態區域中產生的重構觸發信號,然后對相應的重構區域進行重配置。

動態重構控制器從非易失性存儲器(例如Flash)中檢索部分比特流文件,將其傳送到內部配置端口ICAP(Internal Configuration Access Port)。動態重構制器可以置于外部設備(例如處理器)中,也可以放在需要重構的FPGA設備中。與靜態區域中的其他邏輯一樣,動態重構控制器在整個動態重構過程中不間斷地運行。

Vivado設計套件對動態重構的設計進行了軟件上的支持。在Vivado中,提供了動態重構設計的專用流程,并且提供了動態重構控制器(Partial Reconfiguration Controller,PRC)IP核[7-8],用戶可以直接使用此IP核來進行動態重構流程的設計。

2 硬件架構設計

2.1 靜態卷積神經網絡加速器

靜態卷積神經網絡加速器的總體硬件架構圖如圖3所示。在第一層(C1)、第三層(C3)與第五層(C5)卷積層階段,分別采用了6個、6個、10個卷積模塊并行運算。其中第二層池化層(S2)與第四層池化層(S4)分別與之前的C1和C3構成流水線結構。最后一層全連接層(F6)直接復用C5層的10個卷積模塊。

圖3 總體架構圖

在第一層卷積層(C1)中,輸入為32×32的輸入圖像,輸出為6個通道的輸出特征圖。所以在C1中,設計了6個卷積模塊并行地對6幅輸出特征圖進行計算。在每個卷積模塊中有5個PE單元,它們將25個乘加運算分解為5個1×5的乘加運算并行計算。

C1之后的是第一層池化層(S2),輸入為6幅28×28的特征圖,輸出為6幅14×14的輸出特征圖。所以在S2中,設計了6個池化模塊并行地對6幅輸入特征圖進行池化運算。C1與S2采用流水線結構,S2階段首先對C1階段生成的像素點進行緩存,當緩存的像素點可以形成一個2×2的池化區域時,開始S2層的運算。

第二層卷積層(C3)在S2之后開始運算。C3層的輸入圖像為6幅14×14的輸入特征圖,輸出為16幅10×10的輸出特征圖(與6幅輸入特征圖部分連接)。所以在C3層中設計了6個卷積模塊對6幅輸入特征圖進行卷積操作,串行地輸出16幅輸出特征圖。卷積模塊中的PE設計同C1層。

第二層池化層(S4)采用一個池化模塊對串行輸出的16幅輸出特征圖進行下采樣,輸出16幅5×4的輸出特征圖。流水線設計同上。

第三層卷積層(C5)的輸入為16幅5×5的輸入特征圖,輸出為120幅1×1的輸出特征圖。所以設計了10個卷積模塊循環12次對這120個輸出特征圖進行計算。

最后一層全連接層(F6)輸出為1×10的數組,代表著手寫體的識別結果。這里復用了C5層的10個卷積模塊來對這十個值并行計算。

卷積神經網絡涉及的一個核心運算是圖像的卷積運算。由于Lenet-5網絡卷積層的卷積運算規模為5×5,本文的設計將卷積運算分成等量的5組,每組中的5個乘加運算采用二級流水線的結構。每一組的乘加運算都會輸出一個結果至下一組,下一組將自己的乘加運算結果加上上一組的結果后,再繼續對下一組輸入。最后由第五組累加前面4組的乘加和進行輸出。本文設計的PE結構圖如圖4所示。PE工作時乘法器每個周期都有輸入數據,既提高了吞吐率又提高了硬件的利用率。

圖4 PE架構圖

2.2 動態重構卷積神經網絡加速器

本文設計的動態部分重構方案把FPGA片上區域分為靜態區域(Static)與四個動態重構區域(PR1、PR2、PR3、PR4)。每個重構區域都分配了三個不同的重構模塊用于分時配置。

將重構模塊分配給不同的重構區域時,遵循了配置進同一個重構區域的不同模塊,其占用的片上資源數目要盡量相近的原則,以降低對片上資源的浪費[9]。本文的設計對重構模塊的分配情況如表1所示。在不同的階段,相應的重構模塊被配置進對應的重構區域中,與靜態區域中的其他模塊共同完成這一階段的運算。

如表1所示,整個神經網絡的識別過程分為C1-S2(第一層卷積層與第二層池化層)、C3-S4(第三層卷積層與第四層池化層)與C5-F6(第五層卷積層與第六層全連接層)這三個階段。

表1 重構模塊分配

在第一個階段,四個重構區域將會配置C1層與S2層所需的功能模塊。在S2層的輸出特征圖存儲結束之后,部分重構控制器通過ICAP接口讀取C3-S4階段的配置文件,對四個重構區域進行新的配置。C5-F6階段同理。在C5~F6階段的運算完成后,卷積神經網絡輸出一個識別結果,此時開始新的C1-S2階段的重構模塊配置。

重構設計硬件架構圖如圖5所示。對于重構流程的控制、配置文件的掃描提取、配置文件的存儲,分別使用了:

圖5 硬件架構圖

(1)Xilinx?PRC(Partial Reconfiguration Controller) IP:Xilinx提供的PRC IP為部分動態重構提供了管理功能,它可以監測到重構觸發信號,并對重構的流程進行控制[8]。

(2)ICAP (Internal Configuration Access Port):Xilinx FPGA的動態部分重構設計要基于ICAP接口來實現,它用于檢索與傳送存儲于非易失性存儲器中的配置文件,并且可以通過部分重構控制器來控制[9]。

(3)BPI(Byte-wide Peripheral Interface) Flash:本文的設計中采用了FPGA開發板上的BPI Flash來進行所有配置文件的存儲。BPI Flash在存儲結構上屬于Nor Flash,其×16位寬的數據總線可以提供比SPI閃存更快的配置,并且擁有比SPI閃存更大的容量[10]。

當重構區域需要重配置時,會產生一個特定的觸發信號。PRC捕捉到觸發信號后,通過ICAP端口提取存儲至BPI Flash的配置文件。ICAP作為FPGA的內部配置端口,和SelectMap端口功能相似,它會在PRC的控制下對FPGA進行動態配置。

3 實驗與評估

本文對Lenet-5手寫體識別網絡的動態重構設計,采用了Xilinx-VC707開發板上進行硬件實現。代碼編寫采用Verilog硬件描述語言,使用Vivado IDE 2018進行仿真實現,軟件環境為Windows 10。

3.1 硬件資源評估

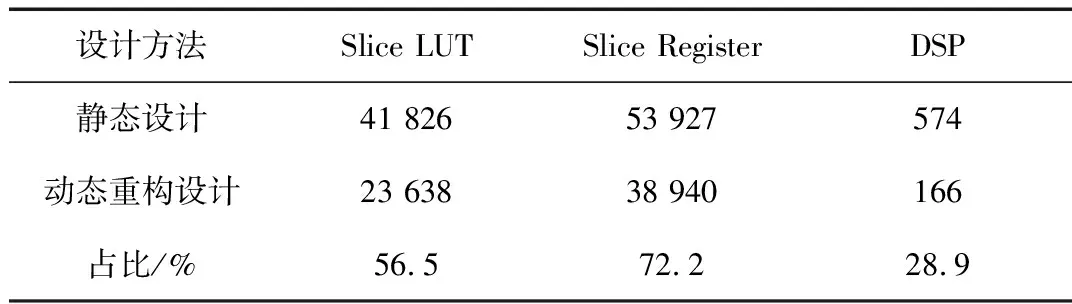

對Lenet-5卷積神經網絡的靜態設計(不使用動態部分重構)與動態部分重構設計進行了對比。使用了動態部分重構方法的設計相比靜態設計,在片上資源的使用量上,尤其是DSP的使用量上有了極大的降低。具體評估結果如表2所示。

表2 資源占用情況

在動態重構設計后,卷積神經網絡加速器所用Slice LUTs資源降低至靜態設計的56.5%,Slice資源降低至靜態設計的56.5%,Slice Register資源降低至靜態設計的72.2%,DSP資源降低至靜態設計的28.9%。可見,動態重構設計可以有效地減少卷積神經網絡加速器占用的硬件資源,提升資源利用率,節約硬件成本。

3.2 時間功耗評估

FPGA動態重構的配置速度基本由配置文件的大小和ICAP端口的帶寬所限制[9]。

在本文的設計中,共劃分了四個重構區域,每個重構區域有三個分時配置的重構模塊,所以一次完整的手寫體識別網絡共需要1個靜態配置文件與12個部分配置文件。總的配置文件大小約為27 MB。

VC707所屬的Virtex系列開發板,ICAP配置端口在100 MHz的最大時鐘頻率下的最大帶寬為3.2 Gb/s[9]。加上卷積神經網絡本身的識別時間,計算得出總時間為20.3 ms。對比基于ARM Cortex A9處理器的軟件實現,如表3所示,在時間與功耗上有著很大的提升。

表3 不同實現方式識別100次的用時與功耗

由于ICAP內部配置端口的帶寬限制,動態重構之后完成一次手寫體識別所需的時間,相較在FPGA上直接進行靜態實現所需的時間會有所延長。這是因為在重構模塊需要工作時,重構區域還未重配置完成,這些等待重構區域而配置完成的時間拉長了整個系統的執行時間。

在未來的設計中,為了更好地發揮動態重構的優勢,可以選取更大規模的卷積神經網絡,并將重構粒度縮小,使配置時間可以隱含在執行時間當中。當然,相信未來的科研工作者們會對配置端口帶寬進一步提升,增大動態重構的優勢。

4 結論

本文介紹了動態部分重構的思想與設計方法,對Lenet-5手寫體識別卷積神經網絡進行了動態重構設計。在文中對部分動態重構設計中要用到的ICAP接口與BPI Flash進行了簡要的說明。在文章的最后,給出了本文的設計在Xilinx VC707上實現所需的資源、時間與功耗。實驗表明,動態重構設計可以有效降低卷積神經網絡硬件實現階段所需的片上資源,大大提升硬件資源利用率,使卷積神經網絡的硬件實現更加通用靈活。

本文首次將動態重構技術應用于卷積神經網絡的硬件實現中,可以有效解決卷積神經網絡因所需硬件資源過多而不能完整放置于硬件的問題。

限制動態重構配置速度的主要為ICAP配置端口的帶寬,希望未來科研工作者可以對此進步一提升,更好地推動動態部分重構的發展。