基于FPGA的CPCI-CAN通信卡電路設計

戴宏睿李文魁阮嘉偉

(1.海軍工程大學電氣工程學院,武漢,430033;2.東部戰區海軍保障部,寧波,315100)

20世紀90年代發展起來的PCI總線作為計算機的行業標準,具有支持多種處理器、優異的并行操作能力、即插即用等特點[1],但在工業控制、軍工等可靠性實時性要求較高的場所,暴露出連接不可靠、抗干擾能力差、抗震性差等問題。緊湊型PCI總線(Compact PCI)是PCI總線的電氣和軟件標準與歐式板卡機械結構的結合。電氣接口上增加了一部分故障檢測、系統管理、熱插拔等總線信號;機械結構上摒棄了原有的金手指連接方式,采用高密度、氣密性針孔連接器,連接可靠。

控制器局域網(Controller Area Network,CAN)是20世紀90年代發展起來的現場串行總線。相比于RS485等傳統總線,CAN總線采用不分主從的多主方式,通信實時性高;傳輸距離更遠、傳輸速率更快;采用非破壞性總線仲裁技術,抗電磁干擾性好[2];使用短幀數據結構,容錯性高。本文設計旨在開發基于CPCI總線的CAN通信卡,滿足工業、軍事應用環境下的自動化測控系統應用需要。

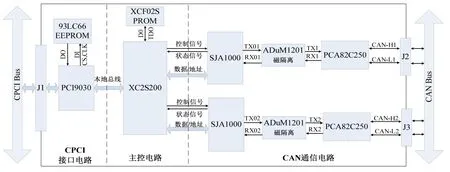

1 總體設計

擬設計的CPCI-CAN通信卡電路組成如圖1所示,主要參數為:3U規格(100 mm×160 mm),2通道隔離CAN接口,DB9接口,支持CAN 2.0B規范,最高波特率1 Mbps,電氣隔離DC 2 500 V。電路主要包括CPCI接口電路、主控電路、CAN通信電路。CPCI接口電路負責接收上位機的指令,CAN收發電路用于執行指令,完成數據和地址的收發,主控電路負責控制數據傳輸速率。

圖1 CPCI-CAN通信卡電路組成框圖

CPCI接口實現一般有兩類方案[3],一是采用FPGA等可編程邏輯器件實現接口邏輯,但 CPCI總線協議及時序控制復雜,開發難度較大;二是采用專用接口芯片,此時不用考慮邏輯的時序匹配等。本文采用第二種方案,選用PLX Technology公司的PCI9030接口芯片實現,它具有可編程通用I/O,兼容PCI r2.2規范,并將CPCI總線信號轉化為本地總線信號。

主控制器件的選擇有多種方案:或是采用單片機、ARM、DSP等微處理器;或是采用可編程邏輯器件,如 CPLD和 FPGA等。現場可編程門陣列FPGA是在PAL、CPLD基礎上發展起來的,相比單片機、ARM 等微控制器,在不更換硬件條件下可靈活方便地升級,開發時間短。本設計采用FPGA實現主控電路功能,具體選用 Xilinx公司的XC2S200。它具有低功耗高級CMOS NOR閃存工藝和適用于標準FPGA配置的JTAG初始化命令。

CAN總線控制器實現有多種方案:一是選用集成CAN控制器的微控制器,如單片機、DSP、ARM等;二是選用獨立的CAN控制器;三是通過FPGA等實現CAN控制器功能[4]。本設計選用獨立CAN控制器SJA1000,可靠性高,開發效率高。

2 電路設計

2.1 CPCI接口電路

2.1.1 組成及功能

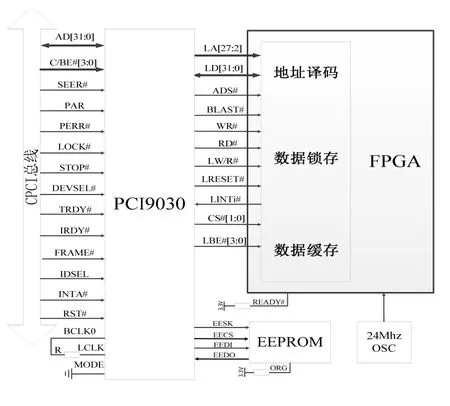

CPCI接口電路實現CPCI總線與本地總線的時序轉換、協議轉換和數據傳輸。如圖2所示,CPCI總線接口信號包括上位機控制信號、數據地址等,這些信號經 PCI9030轉換為本地總線信號,進入FPGA的 PCI9030接口模塊。其中,MODE引腳置低規定PCI9030為非復用模式。

圖2 PCI9030接口電路圖

2.1.2 CPCI本地總線信號

CPCI本地總線信號及含義為:ADS#(地址起始)、BLAST#(傳輸結束),分別控制總線數據傳輸開始和結束。本地地址信號LA[27:2],通過LBE[3:0]使能。非分時復用數據總線 LD[31:0]用來傳遞 32位PCI數據。PCI9030作為主設備時,通過LW/R#控制本地總線數據的寫/讀。RD#和 WR#實現PCI9030的讀輸出和寫輸出。本地中斷輸入 LINTi用于觸發中斷。基地址片選信號 CS0#、CS1#使能本地總線上相應設備,并設定總線地址范圍。LRESETo#用于在復位輸入 RST#有效時輸出本地復位信號。

2.1.3 PCI9030配置電路

PCI9030的初始化通過EEPROM配置實現,包括工作模式、數據地址空間及設備ID等。EEPROM選用93LC66B,3.3 V供電。將93LC66B的CS(片選)、SLK(時鐘)、DO(數據輸出)及 DI(數據輸入)與PCI9030對應引腳相連。ORG置1選擇16位數據傳輸模式。DO需要外接上拉電阻,配合 PCI9030的復位下拉信號 RST#,上電時可在 PC端對EEPROM進行在線燒寫。

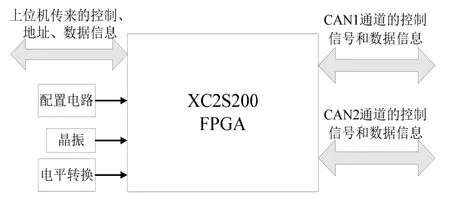

2.2 FPGA主控電路

如圖3所示,主控電路由XC2S200 FPGA及其輔助電路組成,包括24 MHz晶振、電平轉換(5 V-3.3 V、5 V-2.5 V及FPGA配置電路等。其主要功能為:通過CPCI總線接收上位機傳來的信息,處理后產生各種控制信號,實現 CAN總線和上位機之間按規定的時序邏輯進行數據傳輸;通過訪問 CAN控制器實現對 CAN總線的控制,并對兩端總線傳輸過來的數據進行緩沖和鎖存。

圖3 主控電路

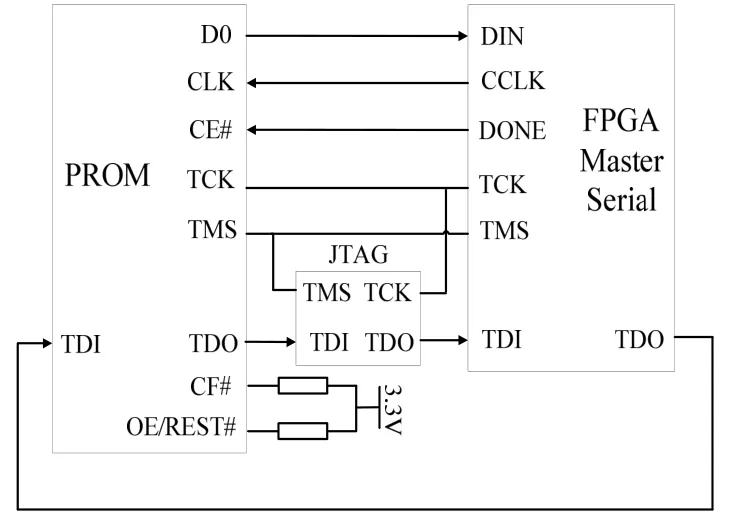

XC2S200 FPGA是基于RAM的,掉電后程序丟失,配套的需選用專用系統可編程PROMS平臺閃存存儲FPGA內部網表信息,工作時再將其加載到FPGA上。根據Xilinx的FPGA配置芯片匹配表,選擇XCF02S作為配置芯片,它具有標準FPGA配置的JTAG初始化命令。配置電路見圖4。

圖4 XCF02S配置電路

FPGA配置可采用主串行模式或從串行模式。本設計使用FPGA主串行模式。該模式下時,FPGA產生時鐘由CCLK輸出驅動PROM,將CF#置高,并使能CE#、OE,數據將在時鐘上升沿傳輸。

FPGA TDO將其內部網表信息傳輸至XCF02S。在配置時,控制信號和同步信號通過TDO發給配置芯片 XCF02S,其收到指令后,通過數據輸出引腳D0輸出網表信息至FPGA的DIN。來自PC端的程序通過JTAG TDO直接對FPGA進行燒寫。

2.3 CAN通信電路

在FPGA控制下,CAN通信電路實現CAN消息幀的接收和發送,其中CAN控制器SJA1000和CAN收發器PCA82C250分別實現CAN協議的數據鏈路層功能和物理層功能。

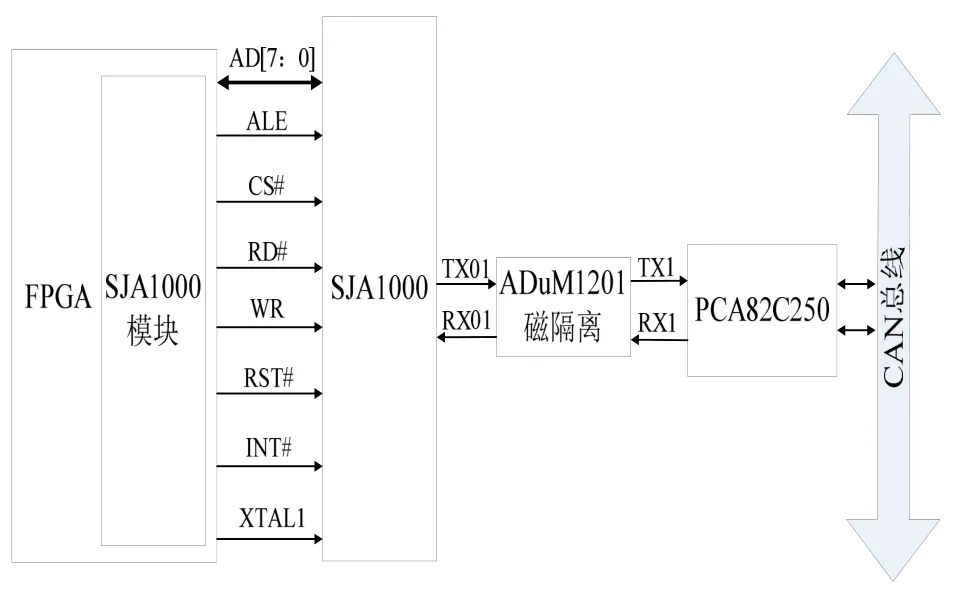

如圖5所示,SJA1000與FPGA的連接信號主要包括:AD[7:0](數據地址復用);讀寫控制信號 RD(讀)、WR (寫)、ALE(鎖存)、INT#(收發中斷使能);來自FPGA的時鐘輸入XTAL1。

圖5 CAN通信接口電路圖

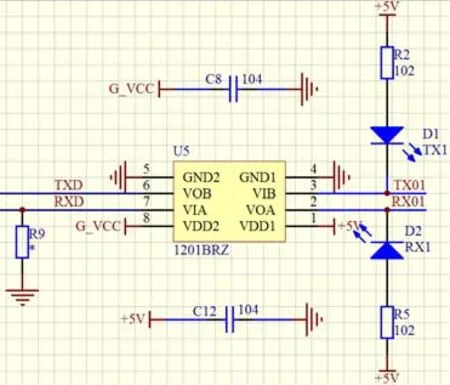

采用雙通道數字磁隔離器 ADuM1201實現CAN控制器與收發器之間的電氣隔離。隔離電路如圖6所示。

圖6 CAN通信磁隔離電路

3 邏輯設計

FPGA開發可采用Verilog HDL、VHDL等多種硬件描述語言。Verilog HDL簡潔易懂,應用廣泛。本文在Xilinx ISE10.1集成開發環境下采用Verilog HDL語言進行板卡的FPGA邏輯設計。

3.1 邏輯模塊組成

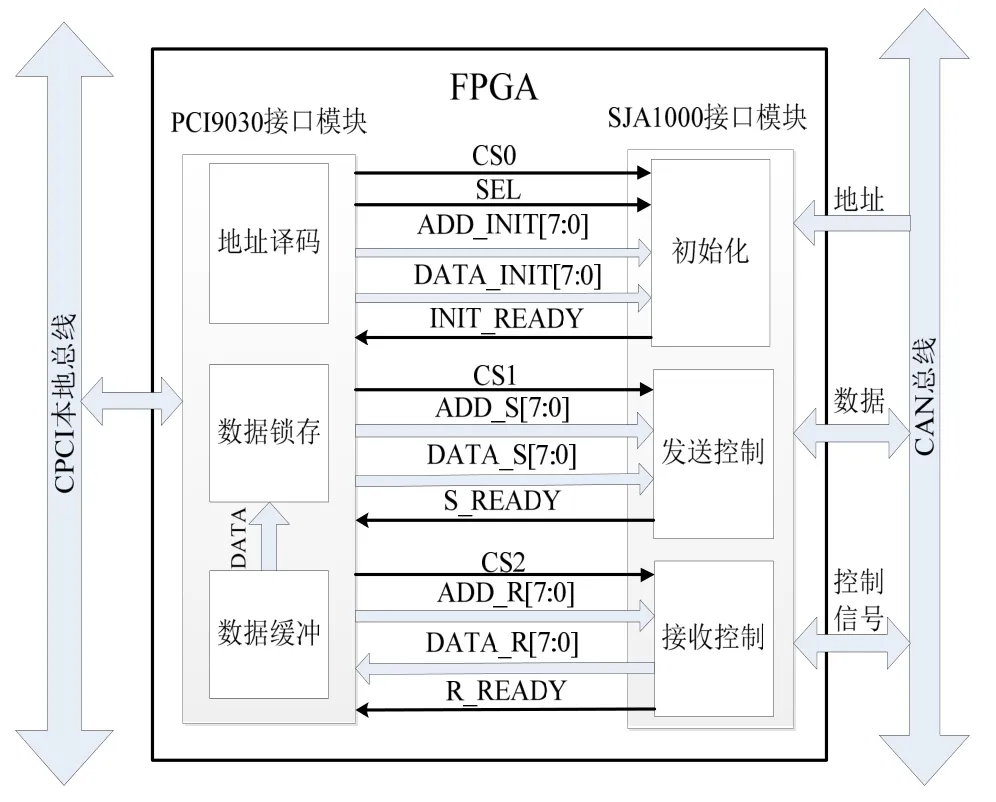

FPGA內部邏輯可分為PCI9030接口模塊和SJA1000接口模塊兩個功能模塊。前者包括地址譯碼、數據鎖存和數據緩沖子模塊,實現與CPCI總線的數據交互;后者包括初始化、發送控制和接收控制等子模塊,實現CAN總線數據通信。FPGA內部邏輯如圖7所示。

圖7 FPGA內部邏輯

上電后,應首先完成SJA1000和PCI9030的初始化。接收數據時,SJA1000接口模塊接收來自CAN總線數據,通過接收控制單元進入數據緩沖區,發送給PCI9030接口模塊,經由PCI9030傳遞到CPCI總線到達上位機。發送數據時,上位機發送指令,經PCI9030接口模塊地址譯碼后,將數據地址鎖存。進入SJA1000接口模塊數據緩沖區,待先前數據發完后,通過發送邏輯將數據送至SJA1000往外發送。

PCI9030接口模塊負責將傳來的上位機發送或接收命令信號進行譯碼,使能(CS[2:0])SJA1000的各子模塊和CAN通道選擇(SEL)等。鎖存來自上位機或 CAN總線的數據地址,并提供接收數據時的緩沖空間。

3.2 SJA1000接口模塊設計

FPGA要實現對SJA1000的控制,主要是對其寄存器進行操作,包括初始化、發送控制及接收控制。FPGA的控制命令是通過寫使能 WR、讀使能RD、鎖存ALE及片選CS等操作實現對寄存器的讀寫。

SJA1000接口模塊的主要工作流程為:接收到發送或接收指令后,向SJA1000發送初始化指令,待發送/接收的數據進入 SJA1000接口模塊中的發送接收控制子模塊。同時各子模塊準備好后將READY信號返回上位機。

3.2.1 初始化邏輯

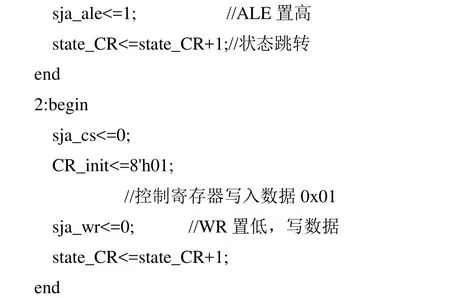

仿真開始時,設置各信號初值為0。分別對控制寄存器賦值0x01和0x06,完成置位復位請求和發送中斷使能。下面給出部分代碼及含義。

SJA1000初始化操作時序如圖8所示。通過對總線定時寄存器(BTR0和 BTR1)賦值來設置總線波特率。16 MHz晶振,波特率125 kbps,則BTR0和BTR1分別賦值0x03和0x1c。置位命令寄存器(CDR)設置CAN模式。

圖8 CAN控制器初始化仿真

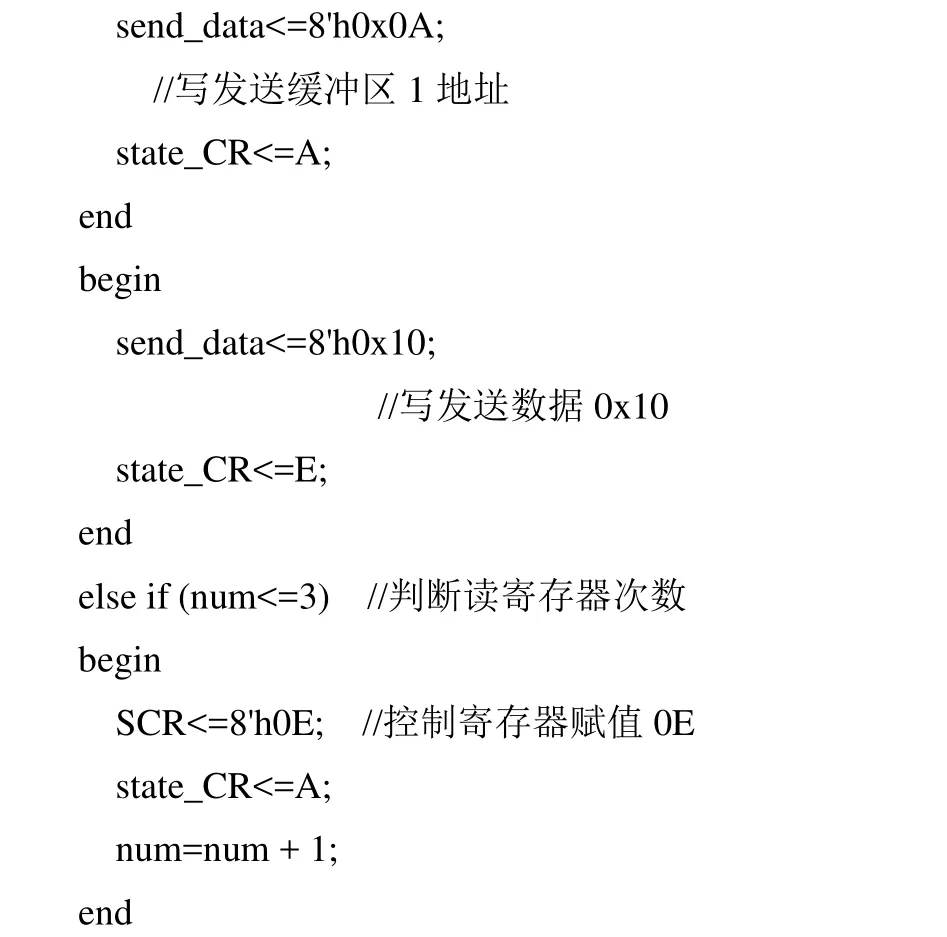

3.2.2 發送控制邏輯

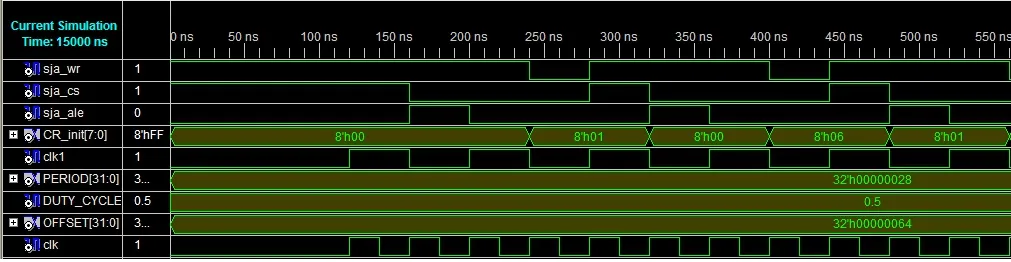

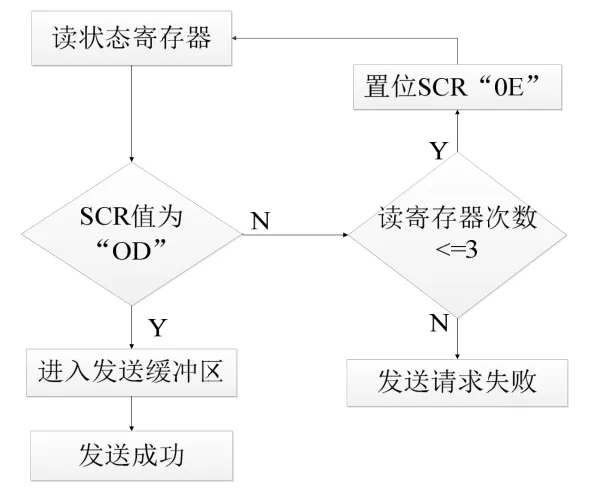

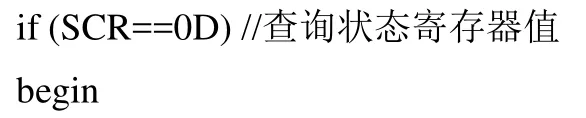

發送前,檢測是否有數據等待發送,即讀取SJA1000狀態寄存器值是否為“0D”,若是,表明發送緩沖區空閑。若不滿足,賦值“0E”給控制寄存器,清空發送緩沖區,再讀取狀態寄存器值,循環超過3次即發送請求失敗。發送控制流程如圖9所示。

圖9 發送控制流程圖

部分發送代碼如下:

3.2.3 接收控制邏輯

板卡收到上位機“接收”指令后,SJA1000接收模塊接收PCI9030接口模塊的發送使能信號,然后讀SJA1000狀態寄存器,判斷是否滿足接收條件。若滿足,置位命令寄存器將SJA1000接收緩沖區的數據發送至PCI9030接口模塊的數據緩沖子模塊。接收控制邏輯對應的主要代碼如下:

4 測試與結論

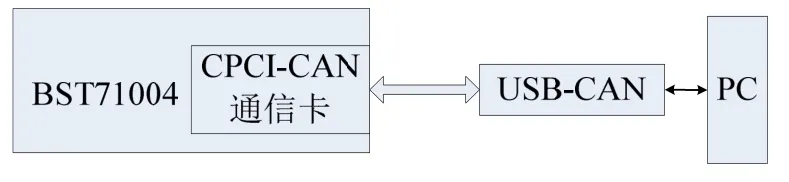

如圖10所示,將CPCI-CAN通信卡插入神州飛航CPCI 6U工控機BST71004,通過USB-CAN轉接器與 PC連接。PC端運行 CAN測試軟件CANTest。總線波特率分別設置為125 kbps、500 kbps和1 000 kbps,CAN數據幀采用擴展幀,對板卡進行 CAN數據收發的通信速度測試和正確性測試。結果表明,該CPCI-CAN通信卡能在CPCI總線計算機上以最高1 Mbps的波特率實現CAN總線數據的正確傳輸,通信可靠,工作穩定。

圖10 板卡通信測試連接圖

本文設計的CPCI-CAN通信電路以FPGA為核心進行開發,消除了傳統 CAN通信電路可能存在的信道堵塞等問題,具有可靠性高、抗干擾能力強、便于后續升級的優點。該CPCI-CAN通信卡在工業及軍事領域具有廣泛的應用前景。