一種高效的CPU設計方法及其在計算機組成原理課程中應用

吳繼明, 曾碧卿

(華南師范大學 計算機學院,廣州 501631)

0 引 言

CS2013及國家教育部高等學校計算機科學與技術指導委員會均要求進行計算機專業學生的系統能力培養,2017年國家教指委提出的新工科思維中也特別注重計算機系統能力、創新能力的培養,當前國內外高校都在開展這方面的工作。計算機系統能力包括計算機系統分析能力、系統設計能力和系統驗證能力,3個方面相輔相成,共同構成計算機專業本科學生的基本能力和專業素養。計算機系統能力的培養從根本上依賴于計算機系統類核心課程——計算機組成原理、操作系統和編譯原理這 3 門課程,其中計算機組成原理課程在整個計算機系統類核心課程鏈中處于中心位置[1-3]。

CPU設計是實現計算機系統能力培養中的一個至關重要的環節,通過CPU 的設計可以把對計算機原理的理解上升到計算機的設計與實現層面,對計算機的原理有一個全面的理論認識和切身的設計體會。目前許多國內外高校都在計算機組成原理課程中安排了CPU設計方面的課程和實驗,基本上都是在Quartus II仿真平臺應用硬件描述語言VHDL或者Verilog完成開放式CPU的邏輯設計與仿真,然后下載到FPGA開發板上進行工程驗證[4-9]。這種CPU設計方式存在如下問題:① 學生學習成本高,學習周期長,普通高校的學生難以在短時間內掌握硬件開發語言和硬件開發平臺的調試與使用;② 學生實踐開發過程中,依賴于實驗室的硬件環境,回到宿舍無法繼續開發或者調試,即使只在Quartus II平臺上做仿真,也涉及到不同處理器電腦上安裝仿真軟件出現bug的問題;③ 分析仿真數據時一頭霧水,不知如何下手去看懂各個器件之間的數據關系,程序、指令、微程序、微指令之間的關系不能在仿真界面清晰直觀展現,編譯時出現錯誤或者仿真時數據不對難以快速找到錯誤源。④ 《數字邏輯》《計算機組成原理》《計算機體系結構》等課程使用不同的硬件實驗環境,導致學生在不同課程實驗中完成的設計成果不能延續復用。

1 高效直觀的CPU設計方法

為了更好地培養學生的計算機思維能力和邏輯設計能力,經過多年的CPU設計實踐教學積累,我們在教學過程中提出了“CPU仿真設計與工程實現”兩步走的理念。先通過仿真平臺完成CPU的仿真設計,在設計與仿真分析過程中引領學生深入理解計算機的工作原理;對于有盈余學習能力的學生,再指導他們在FPGA開發板上完成設計的工程實現。考慮到很多普通高校計算機組成原理的實踐教學中以CPU仿真設計為主[10-15],本文著重探討CPU仿真設計的問題。

1.1 仿真平臺LogiSim

LogiSim是一款開源的數字電路仿真軟件,勿需安裝,是一種符號圖設計語言[16]。它提供了硬件設計所需的各種基本器件,器件都是參數化設定的。邏輯設計過程中,對于連接錯誤或者器件之間的邏輯不匹配時,連接的總線或者器件會出現紅色、橙色的信息提示出錯,工作時連線上有有效電平出現時呈現綠色狀態。沒有邏輯錯誤即可進行仿真,設定好輸入數據/信號,就可立即進行仿真,不需要再度編譯。仿真上輸出界面可按需定制,每個器件或者每根連線上的數據都可以用數值、指示燈等方式顯式輸出,非常直觀。每個設計項目就是一個文件,在按照自頂向底或者自底向上的方式設計大系統時,只需要調用該器件的一個電路文*.circ件即可。大系統中某個子模塊修改設計后,通過簡單的重載(reload)操作即可進行仿真輸出。這種基于Logisim仿真平臺的設計,可以把不同硬件課程中完成的設計作品系統化地融為一體,以部件-模塊-系統的方式進行設計,培養學生的邏輯設計和計算機系統能力。

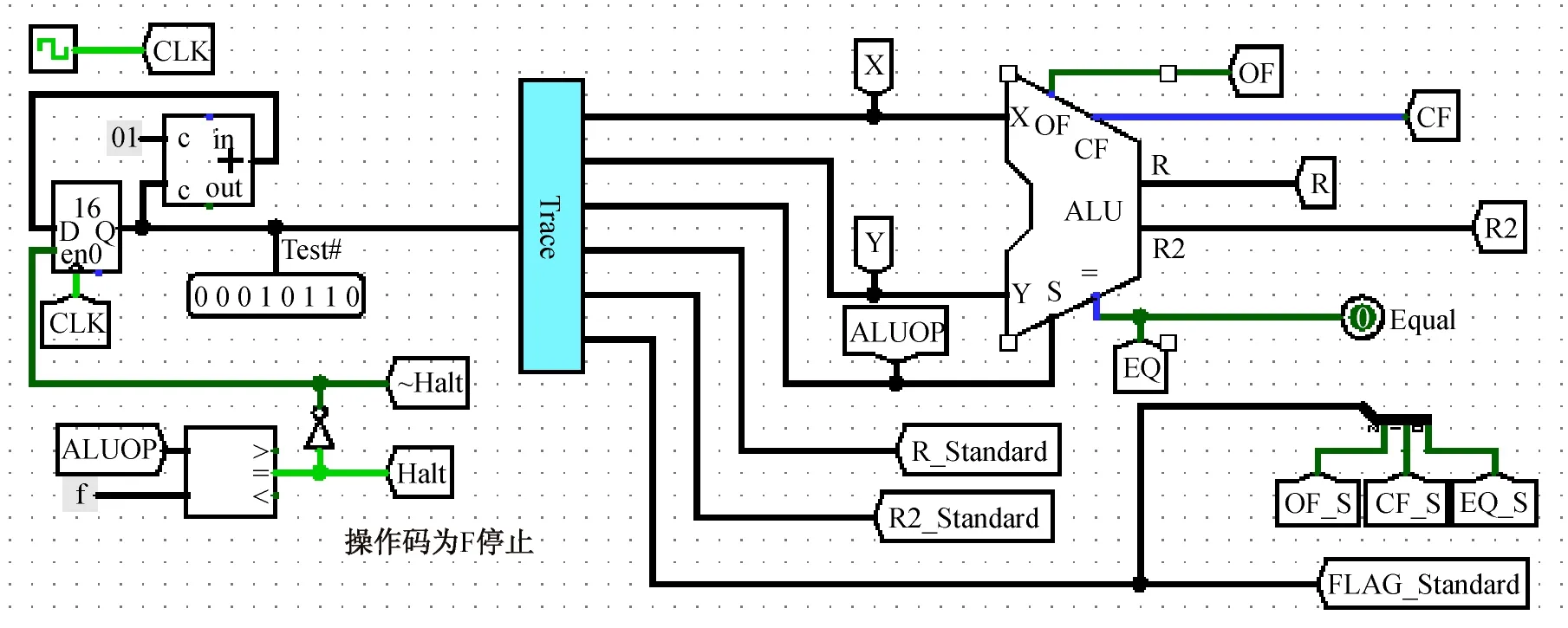

1.2 多功能ALU的設計與仿真

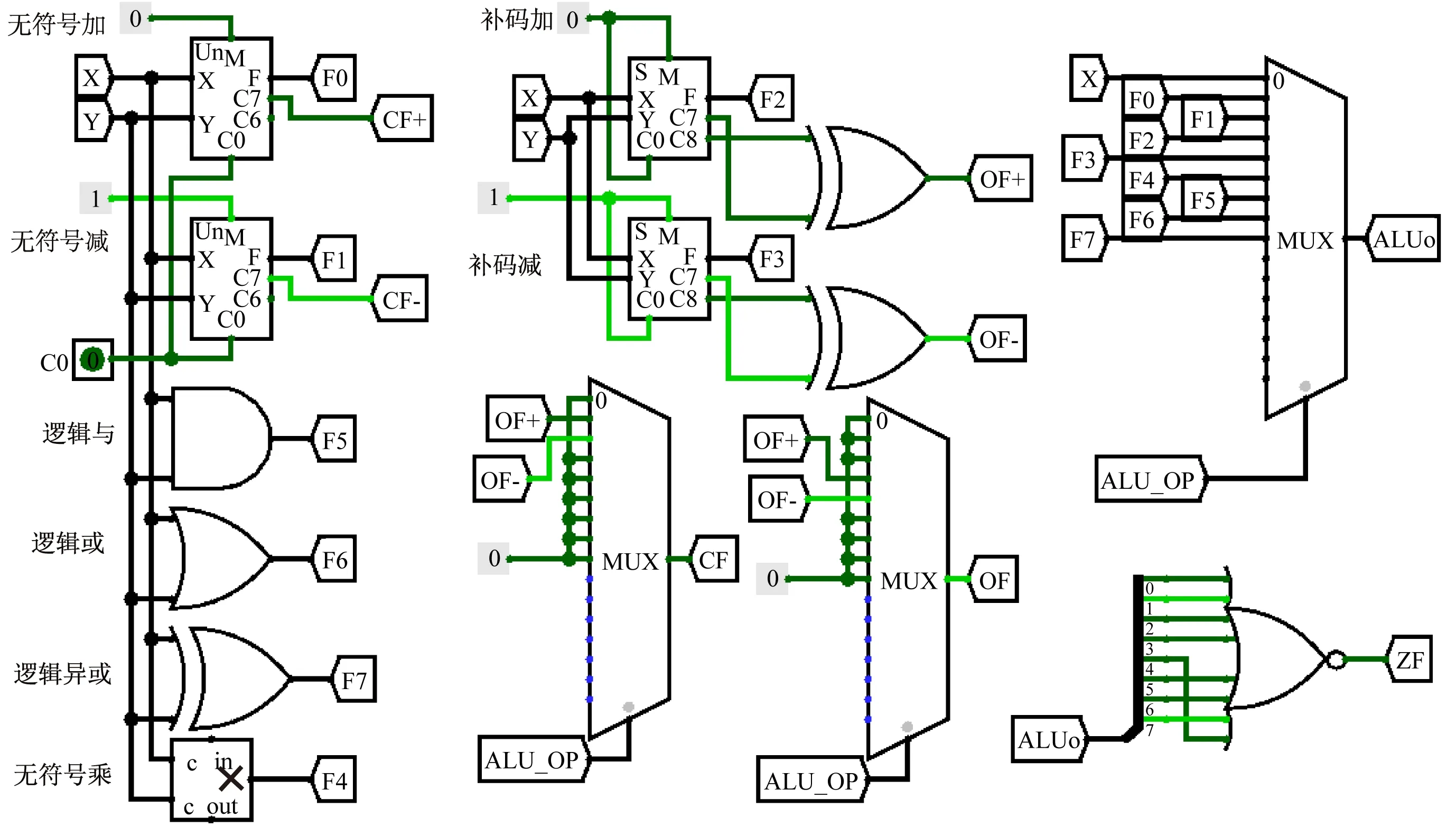

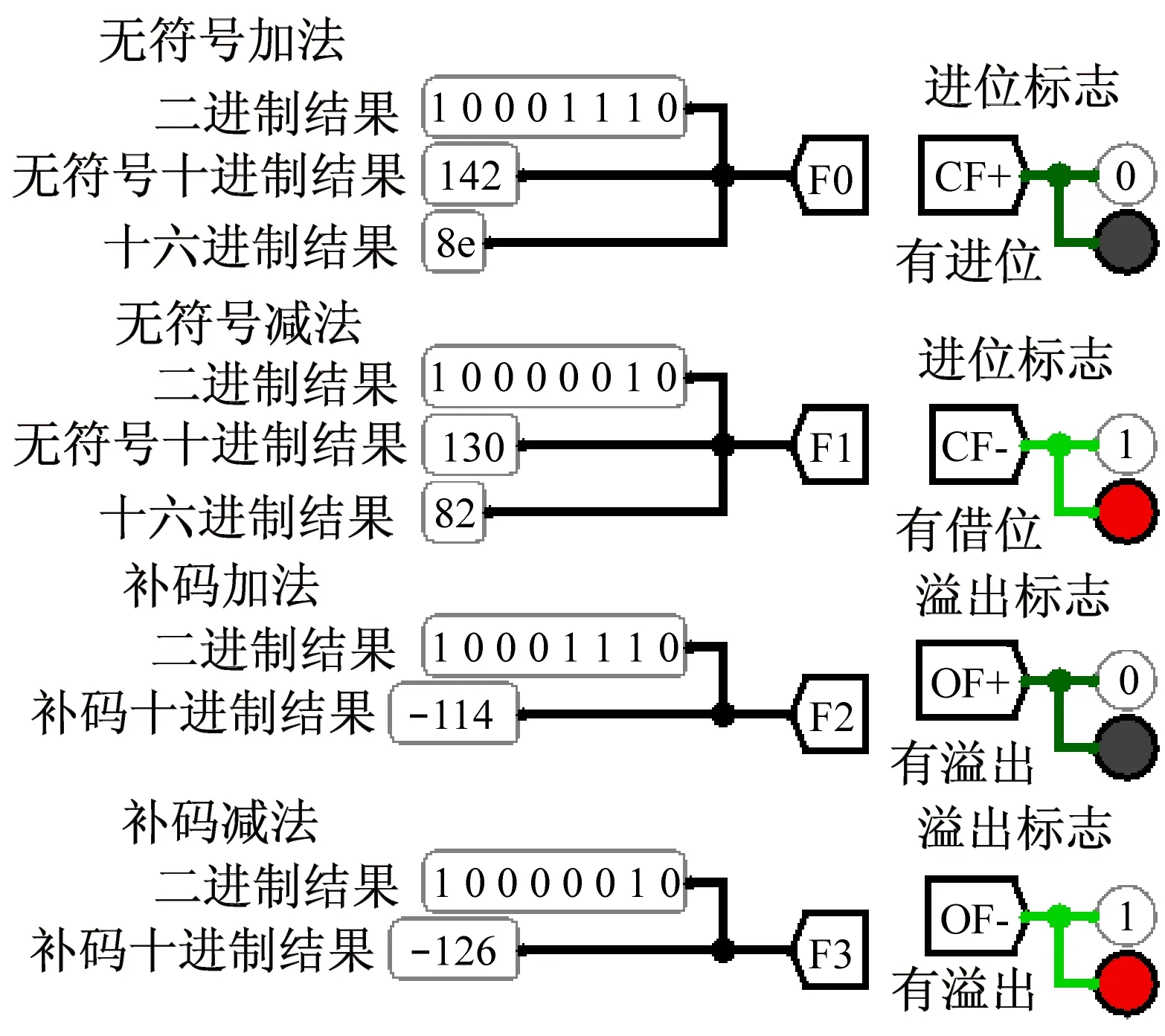

在定義好了ALU的9種功能類型和運算數據長度后,在LogiSim仿真平臺先后設計4位并行的無符號全加器FA/全減器FS,再根據先行進位電路的邏輯關系設計CLA,完成8位并行的無符號FA/FS和補碼FA/FS。整個ALU設計項目中只需要包含4個子器件的電路設計文件*.circ,最終的ALU邏輯電路如圖1所示,ALU功能選擇操作碼有4位,可擴展實現共16種運算。ALU功能仿真截圖如圖2所示,對于2個輸入數據,可以同時查看到不同運算類型的結果和特征位。

1.3 微程序控制器uC的設計與仿真

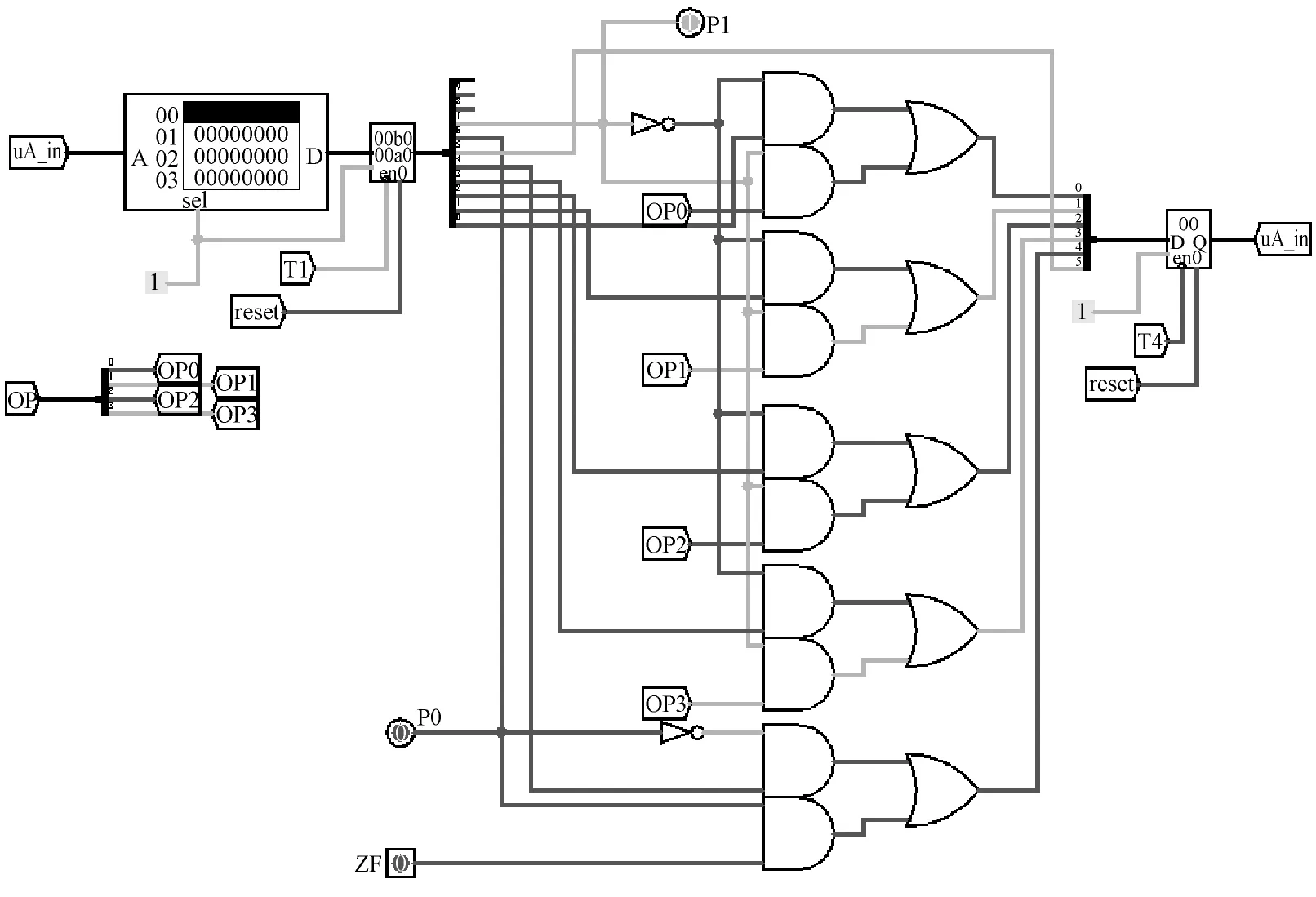

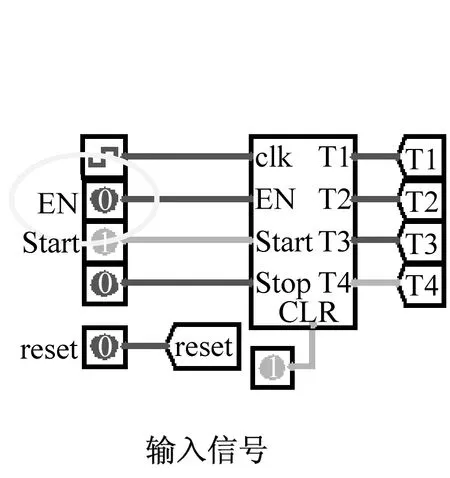

CPU控制器是模型機中的核心部件,負責產生所有的微命令,并在時序信號的同步下完成指令的取出與執行。設計CPU控制器的方法主要有微程序思想和硬布線思想,前者是存儲器型控制器,后者是邏輯電路(布爾)型。限于篇幅,本文給出一個8位字長經典指令的CPU控制器微程序設計,指令類型及數量如表1所示。首先根據指令系統和數據通路繪制出指令的周期流程圖和微程序流程圖,然后定義好微指令格式并進行微程序編碼。接下來,在LogiSim仿真平臺著手控制器uC設計:調用參數化ROM存儲微程序,根據微地址修改邏輯表達式調用基本門器件設計微地址轉移邏輯電路,最后添加輔助器件完成控制器的設計。uC設計電路和仿真界面如圖3所示。

圖1 9種運算功能ALU的邏輯電路

圖2 ALU功能仿真界面

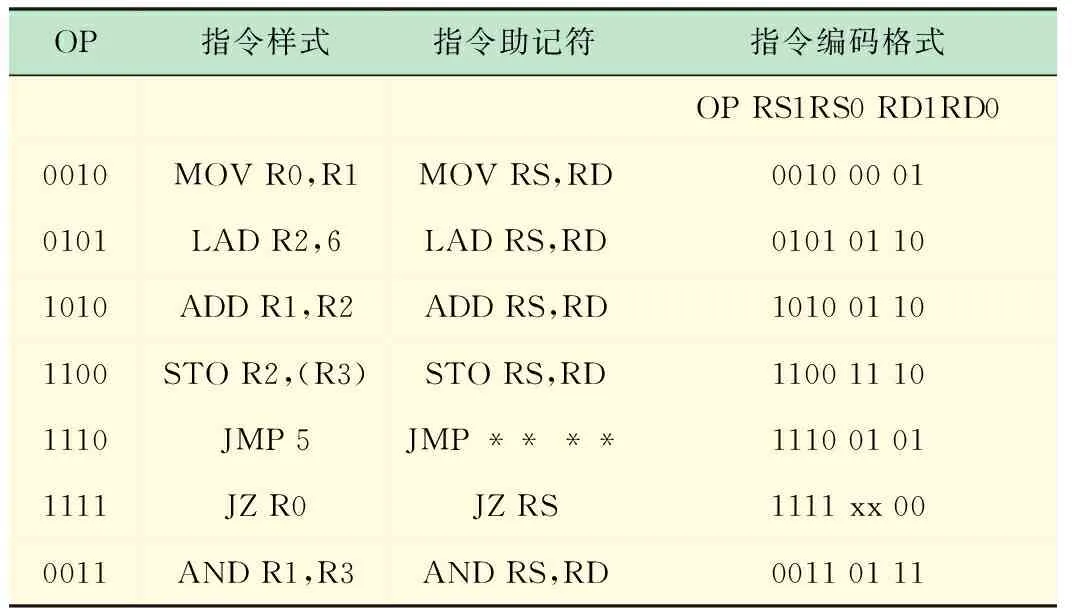

表1 8位字長的機器指令格式

(a)微程序控制器uC邏輯電路

圖3 uC設計電路與仿真界面

由圖3可見,設計和仿真過程非常簡單。可以根據需要用二進制、十六進制形式顯示需要觀察的數據,P位是微程序發生分支轉移的重要標志,可以同時輔以LED指示該條件是否有效。對照微程序編碼表格,逐步改變指令OP和需要的ZF、CF等標志信息,就可以快速完成微程序控制器邏輯功能的驗證。

1.4 多周期CPU模型機的設計與仿真

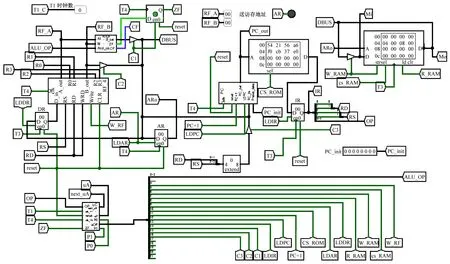

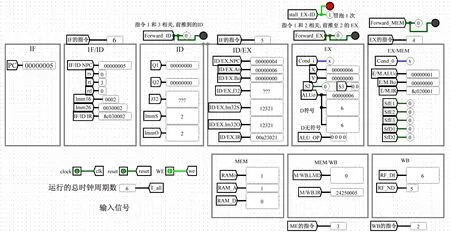

應用前面基于微程序思想設計好的微程序控制器uC和多功能ALU,輔以寄存器和存儲器,在單總線連接方式下完成模型機的電路設計,如圖4所示。圖5為功能仿真過程中取指微指令階段的各種信息。

圖5表達的是取指微指令在一個CPU周期內的數據信息,當前ROM中地址0處取出的指令IR是54H,下一順序指令地址是1,當前取指微指令的地址是00H,后繼微地址是20H,P1有效,當T4上升沿到達后,下一關聯微指令地址被修改為25H。圖6表達的是LAD指令執行期間的數據信息,uA值為26H表示處于LAD第二條微指令工作期間,訪存地址是06H,RAM輸出數據是08H,輸入數據無效表明是讀訪存,T4上升沿到達后R2寄存器值由0變為8H。

圖4 多周期CPU模型機邏輯電路

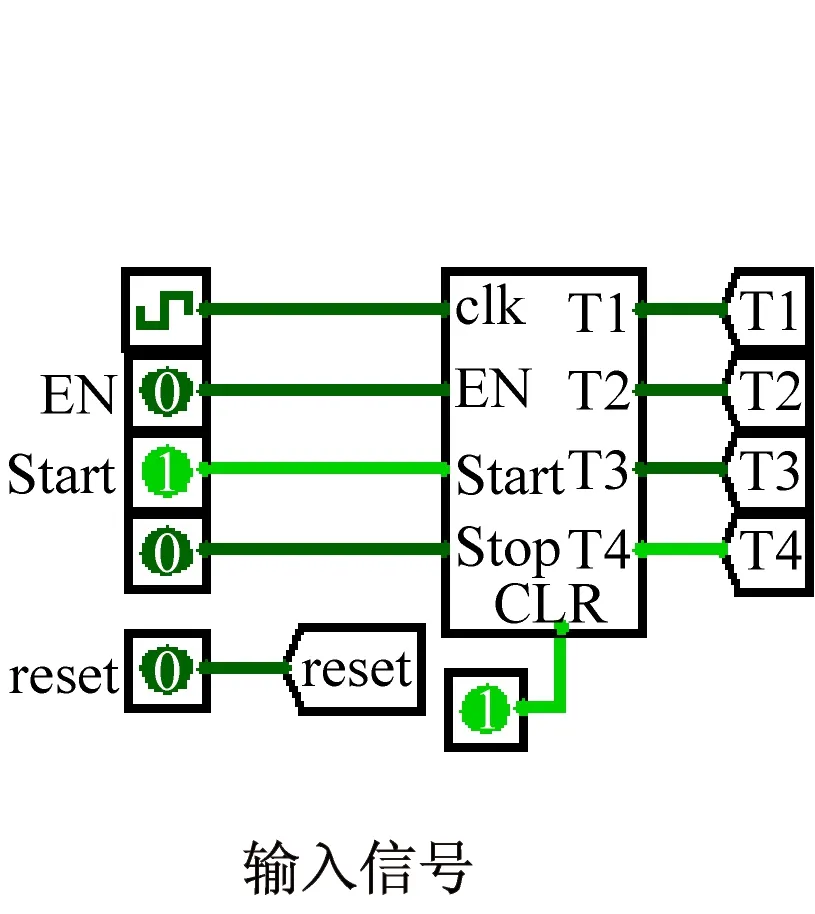

1.5 流水線CPU模型機的設計與仿真

基于RISC指令系統MIPS 32,選取算術邏輯運算指令(R類型)、訪存指令/條件分支轉移指令(I類型)和無條件轉移指令(J類型),在LogiSim仿真平臺完成硬布線控制器、通用寄存器堆、流水線緩沖器(IF/ID,ID/EX,EX/MEM,MEM/WB)、數據真相關前推電路和數據真相關冒泡電路等器件,最后連接成一個基于經典五段流水線IF、ID、EXE、MEM、WB的流水線模型機,圖7是邏輯設計電路,圖8是功能仿真界面。

2 不同開發平臺下CPU仿真設計對比研究

CPU的仿真設計可以幫助學生理解計算機的工作原理,提高他們的計算機思維能力和系統設計能力。當前主流的做法是在Quartus II平臺中完成設計,Quartus II或者ModelSim中完成仿真[4-6]。本文介紹的CPU設計方法,融設計與功能仿真于一體,學習效率高,無實驗環境需求,教師可以在理論課堂上隨用隨講輔助教學,可以在機房帶領學生從事實踐開發,課后學生回到宿舍可在自己電腦上繼續開發。和Quartus II平臺的仿真設計過程相比具有如下分一些優點。

圖7 MIPS指令五段經典流水線CPU模型機

圖8 MIPS指令五段流水線CPU模型機功能仿真界面

2.1 設計和仿真過程的比較

在Quartus II設計和仿真,當調用子器件完成當前項目設計時,需包含子項目符號圖文件和源文件,及子項目設計中調用的系統參數化器件的源文件和符號圖文件,缺少任意一個文件都會無法通過編譯。編譯成功后,生成功能仿真列表,才可以在新建的波形文件中逐一添加輸入、輸出信號節點,設置好end time、grid time,預置輸入信號值,進行仿真。仿真過程不能修改輸入信號值,如果修改了設計中的源文件,必須重新進行編譯和生成功能仿真列表。

LogiSim中設計和仿真,當前項目只需要裝載子項目的源文件*.circ,對調用系統的參數化器件不用考慮文件問題。設計過程就隱含著編譯過程,設計過程有邏輯上的錯誤立刻會以紅色的線或者橙色的線/數字提示錯誤。沒有錯誤提示后,就可以設定輸入信號值立即開始仿真,仿真過程可以隨意改變源文件設計和輸入信號值。

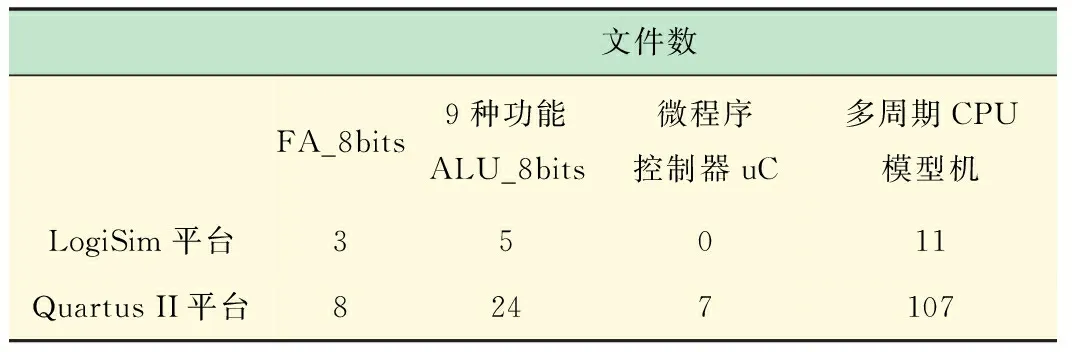

2.2 完成相同邏輯功能器件設計包含子器件文件的比較

LogiSim和Quartus II仿真平臺都支持純符號圖語言的設計方法,但是在基于自頂向底的大系統大項目設計過程中,2個平臺上頂層設計實體對下層支撐模塊和子器件的需求是不同的,以設計8位并行FA_8bits為例分析,主要體現在以下幾個方面:(1)頂層調用子器件1位FA、超前進位電路CLA和4位并行FA,LogiSim中只需要在頂層項目中包含3個子器件文件FA_1bits.circ、CLA.circ、FA_4bits.circ;而在Quartus II中需要包含6個子器件文件FA_1bits.bdf、FA_1bits.bsf、CLA.bdf、CLA.bsf、FA_4bits.bdf、FA_4bits.bsf;(2)頂層調用系統中參數化的數據選擇器、觸發器、寄存器或者存儲器時,Quartus II平臺都會在項目文件夾FA_8bits中生成每個器件的lpm_*.vhd和lpm_*.bsf文件,而LogiSim平臺不會產生任何文件。如果在后續更高層級的項目設計中,例如ALU_8bits或者模型機的設計中,若漏了添加這些系統自動產生的lpm_*.vhd和lpm_*.bsf文件,編譯將會出錯,這也是學生在從事大系統設計時最容易出現遺漏導致編譯不成功的地方。表2給出了2種仿真平臺下純符號圖語言設計器件及模型機時所需下層器件的子文件情況。

表2 兩種不同仿真平臺設計相同目標所包含子器件文件數量比較

2.3 仿真界面的比較

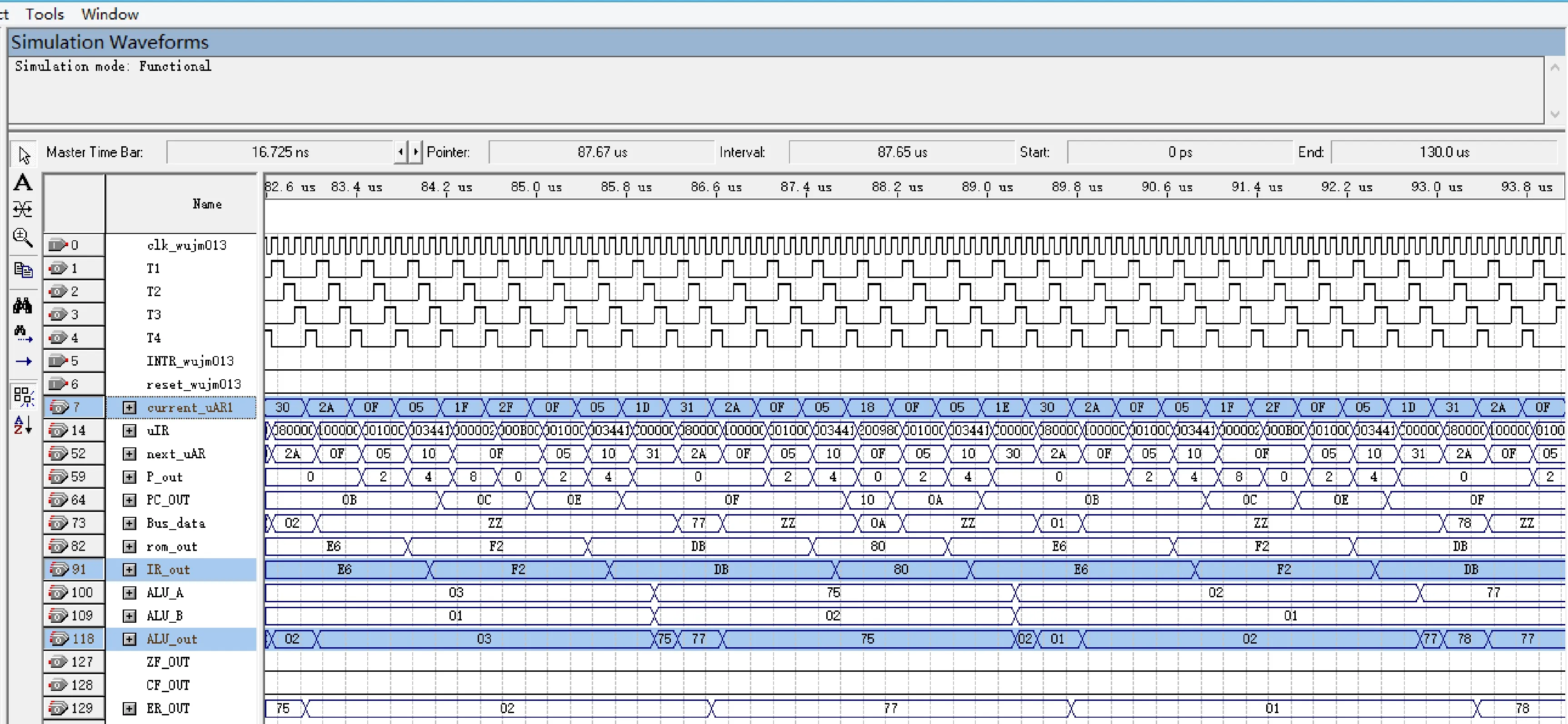

Quartus II或者ModelSim仿真界面是固定的,不能根據用戶需要進行改變,顯示的是波形文件或者數字,Quartus II中多周期CPU構成的模型機仿真界面如圖9所示。當要觀察某個器件的輸出數據時,需要在原設計圖增加輸出引腳output,重新編譯、生成功能仿真列表,并在仿真的波形文件中添加這個output后,運行功能仿真才可以輸出該仿真數據,但是該數據與其它器件之間的數據關系、時間關系卻難以直觀體現。

而在LogiSim中仿真界面可以根據需要靈活設置,便于設計者跟蹤數據的流動和器件的工作狀態。如圖5或者6所示,在本文的CPU設計仿真界面中給出了4類信息。第一列是對應于時序信號發生器的輸入控制信號,連續仿真過程中,如果想停止下來看某個器件或某條總線上的數據,可以用鼠標點擊設置EN=0,仿真程序暫停。同樣,如果某條機器指令工作不正確,可以在任意時鐘周期T內停下來,在設計電路中查看相關數據通路上的數據及相關工作器件的控制信號是否正確。第二列跟蹤微程序工作時的信息,便于學生輸入理解微程序控制器的原理,同時可以隨時檢查自己的微程序控制器是否按照微程序流程圖定義的順序工作。第三列顯示的是機器指令構成的測試程序運行情況,紅色的LED亮表示對應的指令正在工作,LED前面的數字是該機器指令的存儲地址。第四列顯示的是數據通路上通用寄存器和數據存儲器的信息,尤其是在執行訪存指令時,訪存的地址和數據會直接展現在眼前。

圖9 Quartus II中多周期CPU模型機運行1~15累加測試程序仿真界面

2.4 仿真時數據分析過程的比較

Quartus II平臺中,圖9的仿真數據顯示時鐘信號clk周期為20ns時,經過93us后完成了1~15的累加運算,輸出結果ALU_out為78H。但是仿真波形中,什么時候是指令的取值階段,什么時候是指令的執行階段,執行指令時哪些器件在工作,器件之間流動的數據是多少等信息難以直觀看清楚,尤其是對于剛學會使用Quartus II從事硬件設計的學生來講,通過這個仿真數據分析邏輯功能的正確性,理解CPU的指令控制、操作控制、時序控制原理非常困難。

LogiSim平臺中,圖5截圖表達的是取值微指令在一個CPU周期內的數據信息,當前ROM中地址0處取出的指令IR是54H,下一順序指令地址是1,當前取指微指令的地址是00H,后繼微地址是20H,P1有效,當T4上升沿到達后,下一關聯微指令地址被修改為25H。圖6截圖表達的是LAD指令執行期間的數據信息,uA值為26H表示處于LAD第二條微指令工作期間,訪存地址是06H,RAM輸出數據是08H,輸入數據無效表明是讀訪存,T4上升沿到達后R2寄存器值由0變為8H。可以在仿真過程的每個T周期停止下來查看器件工作狀態和數據的變化,輕松理解CPU的操作控制功能。

3 本文CPU設計方法在計算機組成原理課程實踐教學中的應用

LogiSim仿真界面的多樣可視化效果,可以在計算機組成原理實踐教學中提供許多幫助。例如在講授機器碼及補碼的加法/減法運算時,直接在FA的數據仿真過程建立溢出的概念和真值與補碼之間的關系,講授存儲器容量擴展與連接時可以在仿真過程中,形象描述出不同訪存地址選中不同芯片中的單元進行訪問。

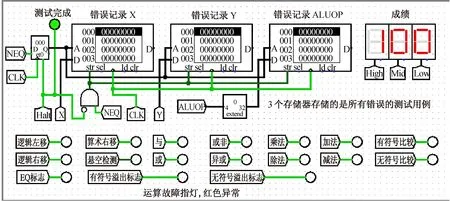

計算機組成原理的實踐教學過程中,給學生布置了多功能ALU、通用寄存器陣列等模塊的設計任務后,教師可以在仿真平臺設計一個自動檢測并給予評分的仿真測試工具,極大提高工作效率,減少教師審閱學生設計項目的工作量。圖10給出了ALU模塊的自動檢測仿真界面,要求學生提交的ALU輸入輸出引腳按規范的要求設置,檢測時只需要把ALU載入就可以自動完成連接,運行仿真就可以在圖(b)的評分界面看到該器件設計的錯誤之處和按權值設定給出的評分[17]。

(a)ALU設計模塊檢測界面

(b)ALU設計模塊評分界面

4 結 語

CPU設計在《計算機組成原理》課程的學習過程中具有非常重要的意義,基于LogiSim仿真平臺的CPU設計方法,能夠幫助學生快速完成設計過程。仿真時能夠以一種直觀、易懂的形式給出輸出,可以按需設計輸出的仿真界面,學生分析仿真數據更簡單明了,有助于理解CPU的工作過程與模型機中的數據驅動。同時也方便教師在理論教學中應用仿真過程描述抽象的概念,設計檢測和評分工具實現對學生設計項目的自動校驗。和其它硬件設計語言的仿真平臺相比,在培養以邏輯設計能力為主的計算機系統思維能力方面,本文給出的設計方法具有突出的優勢。《計算機組成原理》課程中,還存在許多內容重要、概念抽象、晦澀難懂的知識點,例如IEEE754浮點數的四則運算過程及流水線工作方式,Cache、主存、輔存三級存儲體系之間的地址轉換,及多級中斷嵌套工作模式等。后續我們將應用LogiSim仿真平臺完成這些知識點的設計,給學生提供更多易懂的仿真界面,幫助學生深入掌握相應知識,提高他們的計算機系統思維能力和設計能力。