基于CMOS工藝毫米波寬帶片上天線

, ,

(北京遙感設備研究所, 北京 100854)

0 引言

天線通常是一個無線通信系統中的大部件,嚴重制約了系統體積和面積的縮小。在毫米波頻段,將電路元件與天線集成在同一片芯片襯底上,可以有效地減小天線的尺寸。由于片上天線直接與芯片電路相連,不需要經過傳輸線連接,使得設計變得更加靈活。片上天線還具有能大幅度節省功耗、可加工重復性好、可靠性高、結構緊湊、不易磨損等優點。片上天線可以借用最新的半導體技術進行大規模的制造和組裝,隨著技術的逐漸成熟,制造成本也會逐步降低。顯著的優勢及潛在的應用前景使得片上天線的設計成為熱點,并得到了廣泛關注[1-4]。

目前,片上天線的發展仍然存在一些挑戰,比如低阻抗基底導致的天線電流損耗很大、增益小、片上集成導致的結構限制等。標準的CMOS工藝片上天線的增益通常很低,例如94 GHz工作頻率下的微帶圓形貼片片上天線的增益為-5 dBi,在天線上加介質諧振片以后可達到1.2 dBi[4]。采用漏波天線形式,可實現增益約-2.5 dBi[5]等。

本文設計了一種工作于94 GHz頻段的改進型單極子天線,該天線具有寬頻帶工作特性,其相對中心頻率95.8 GHz的相對阻抗帶寬(|S11|≤ -10 dB)達到45.5%。在94 GHz頻點處,輻射效率達到46%,增益約為1.35 dBi。由于半導體介質襯底不同于普通的絕緣介質材料,其特殊的電氣特性對天線輻射性能會產生一定的影響。通過采用全波分析軟件HFSS分析在天線金屬輻射貼片結構不改變的情況下,天線襯底尺寸對天線阻抗和輻射性能的影響。該天線具有工作頻帶寬、輻射性能好等特性,可實現天線與IC芯片的一體化片上集成,滿足寬帶無線通信系統或毫米波雷達系統高集成度、小型化的應用需要。

1 片上天線設計

本文所設計的片上天線采用0.18 μm CMOS工藝,該工藝剖面結構圖如圖1所示,各層介質特性如表1所示。天線襯底采用低阻硅材料,其電阻率為10 Ω·cm,相對介電常數為11.9,厚度為300 μm。天線輻射部分設計在金屬層M6層,該金屬層厚度為4.6 μm,電導率為3.1×107S/m。

圖1 CMOS工藝剖面結構圖

所設計的天線采用改進的單極子結構形式,饋電采用CPW饋電結構,如圖2所示。采用改進的單極子結構可以實現較寬的阻抗帶寬特性。CPW饋電結構和天線輻射結構均設計在M6金屬層,由于毫米波測試探針平臺的G-S-G探針的針距為150 μm或250 μm,因此天線采用的CPW饋電結構滿足兩種探針針距的測試需要。該天線及饋電結構各部分詳細尺寸如表2所示。

表1 CMOS工藝各介質層尺寸性能標準

圖2 片上天線結構示意圖

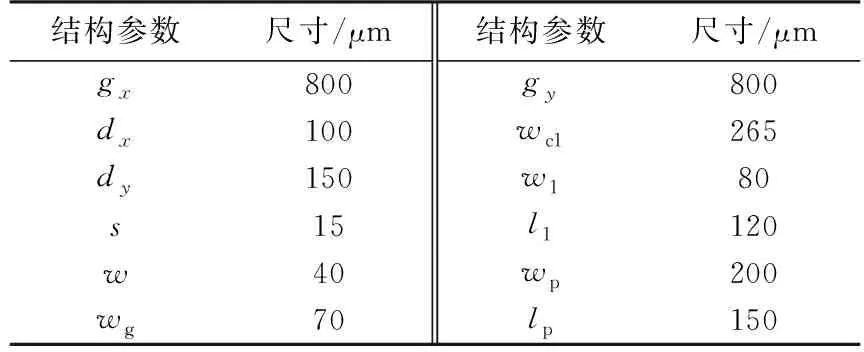

結構參數尺寸/μm結構參數尺寸/μmgx800gy800dx100wc1265dy150w180s15l1120w40wp200wg70lp150

2 襯底尺寸對天線性能影響分析

片上天線采用CMOS工藝,襯底采用低阻硅材料。由于低阻硅材料為半導體結構且相對介電常數較高,部分電磁能量束縛于硅襯底中,形成輻射損耗,使得僅有部分能量從天線輻射部分向外輻射,天線輻射效率較低。另外,由于邊界條件效應,硅襯底中的能量從襯底的邊緣輻射出來,這些能量又極大地影響了天線的輻射方向圖。因此,對于片上天線而言,由于采用半導體襯底的特殊性,會導致天線輻射損耗較大,這些損耗可以歸結為: 1)金屬輻射體的導體損耗; 2)介質的介電損耗; 3)表面波損耗; 4)半導體基底的電阻性損耗; 5)由基底與絕緣層交接面上的載流子運動導致的界面損耗等[6]。

本節分析硅襯底對天線性能的影響,在M6金屬層輻射天線和饋電結構不改變的情況下,僅改變襯底尺寸,對比5種不同襯底尺寸下對天線阻抗特性和輻射特性的影響。

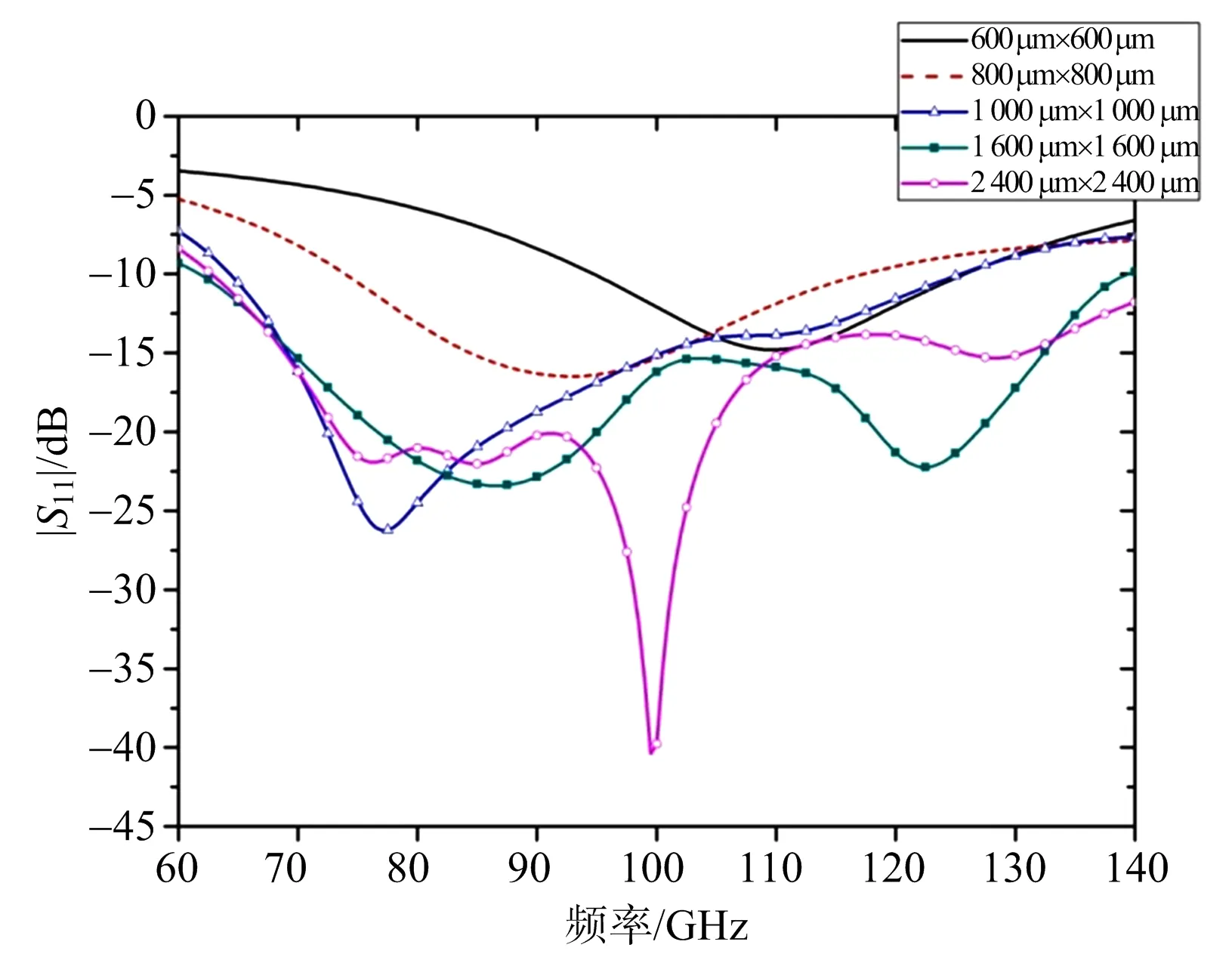

圖3給出了不同硅襯底尺寸下天線的阻抗特性對比。當天線硅襯底尺寸由600 μm×600 μm增大到2 400 μm×2 400 μm時,天線阻抗帶寬(|S11|≤-10 dB)由31.3 GHz(95.18~126.48 GHz)提高到77.21 GHz(62.79~140 GHz),天線阻抗匹配效果逐漸變好。

圖3 不同硅襯底尺寸下天線的|S11|參數

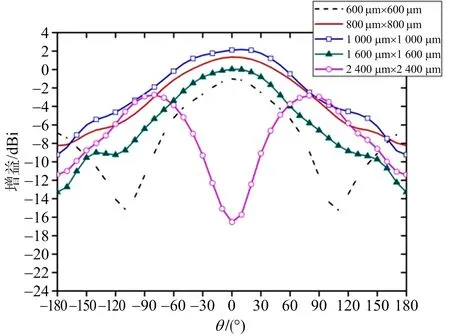

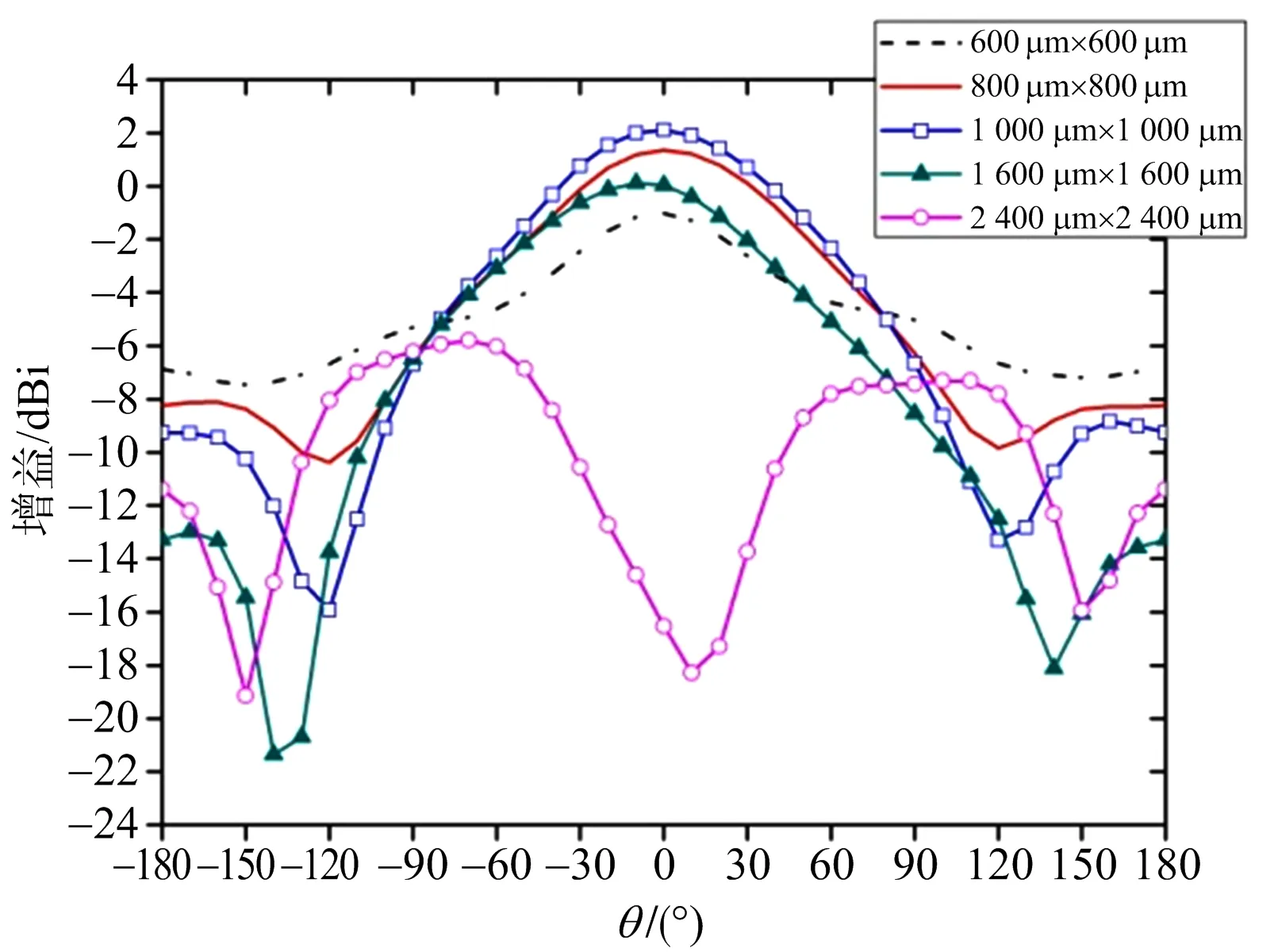

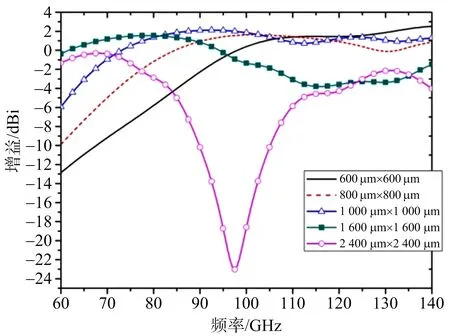

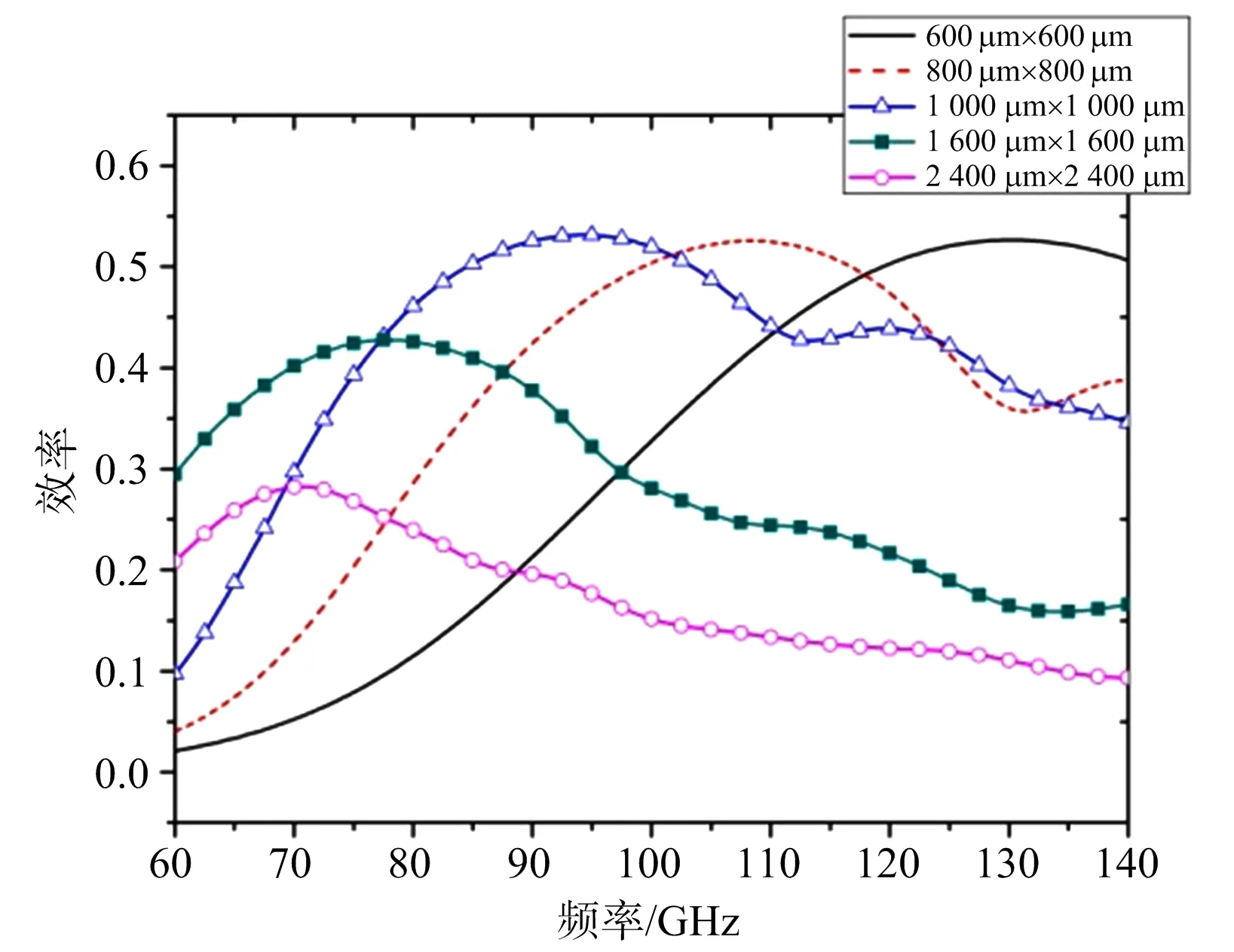

圖4給出了不同襯底尺寸下天線在94 GHz頻點處的仿真方向圖。由天線的方向圖可以看出,天線的輻射圖對稱性較好,但是在天線尺寸過小或者過大時,天線的增益都有不同程度的降低。隨著硅基版尺寸的加大,雖然天線阻抗匹配效果變好了,但是饋入天線的功率并沒有引起增益的提高,而且當尺寸達到2 400 μm×2 400 μm時,天線在Z軸向增益出現了斷崖式下降,為-16.5 dB,天線的輻射方向圖發生的畸變。主輻射方向不在金屬貼片的法向方向,電磁能量向XOY平面的4個方向泄漏。可能是由于硅介質的低阻特性,電流被引向襯底內,電磁能量被束縛在襯底中,一部分形成了電流損耗,一部分從襯底的邊緣輻射出來。隨著襯底的進一步加大,這種現象更加明顯,導致輻射方向圖發生畸變。

(a) H面方向圖

(b) E面方向圖圖4 不同硅襯底尺寸下天線在94 GHz頻點處E面和H面方向圖

(a) 帶內增益

(b) 輻射效率圖5 不同硅襯底尺寸下天線的帶內增益及輻射效率

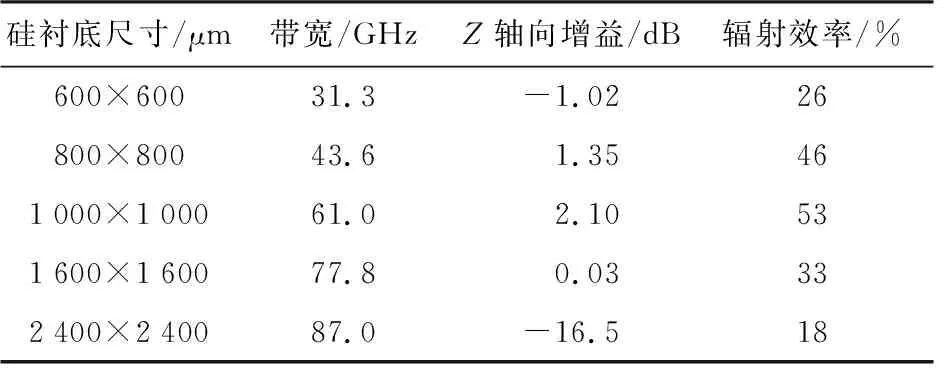

硅襯底尺寸/μm帶寬/GHzZ軸向增益/dB輻射效率/%600×60031.3-1.0226800×80043.61.35461000×100061.02.10531600×160077.80.03332400×240087.0-16.518

3 天線仿真性能分析

基于上述天線襯底尺寸對天線性能影響的分析可知,當天線尺寸定為800 μm×800 μm和1 000 μm×1 000 μm時,天線的阻抗帶寬和Z軸向增益均有不錯的表現,但是當天線處于1 000 μm×1 000 μm尺寸時,天線出現了頻偏,諧振頻率落在77 GHz上。綜合考慮下,天線襯底尺寸選擇800 μm×800 μm。該天線的阻抗特性仿真結果如圖6所示。天線的仿真阻抗帶寬(|S11|≤-10 dB)為74~117.6 GHz,中心頻率為95.8 GHz,相對帶寬為45.5%。仿真結果表明,該天線具有較寬的阻抗帶寬特性。

圖6 天線仿真阻抗帶寬

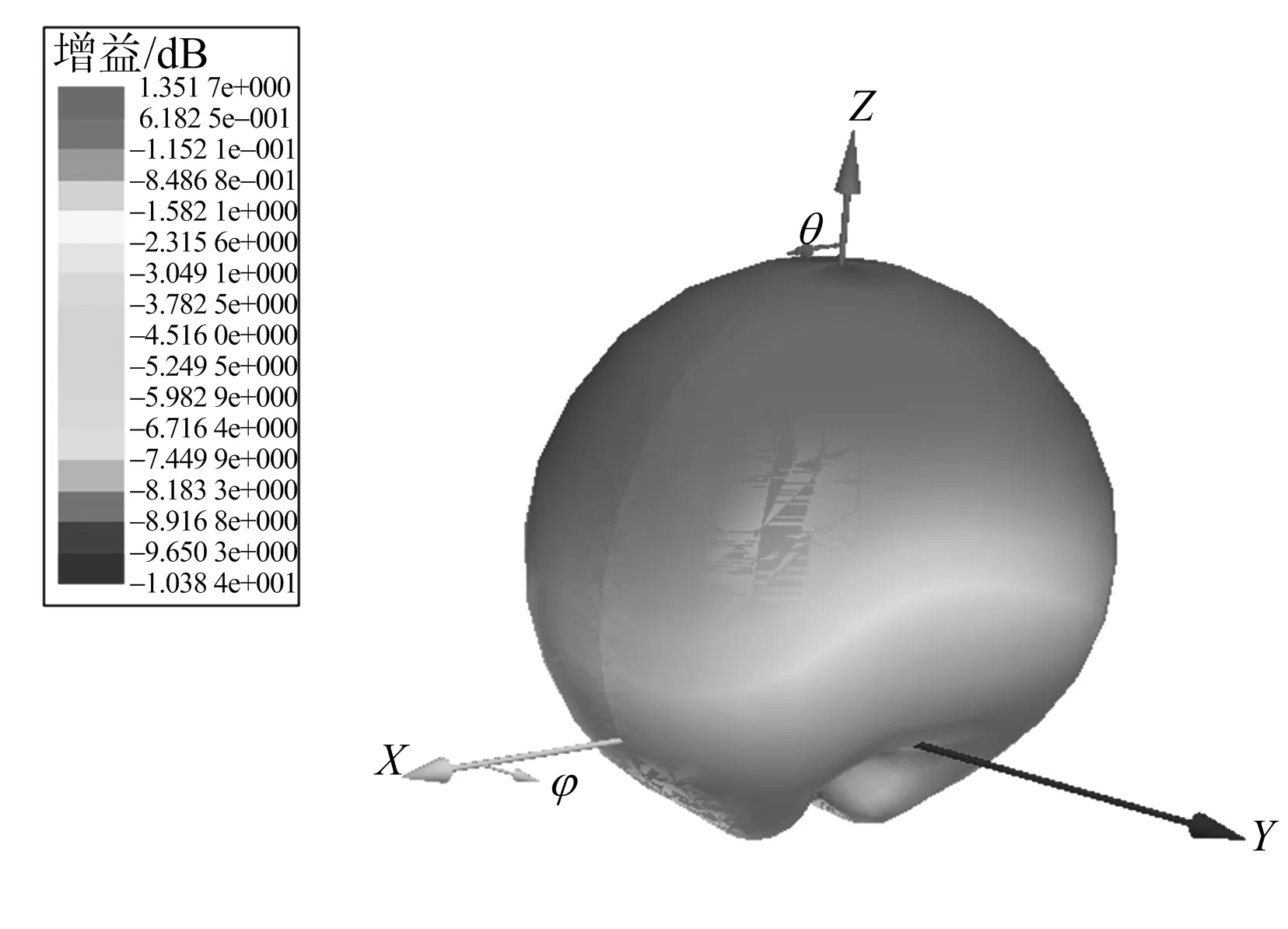

圖7給出天線在中心頻點94 GHz處的仿真三維輻射方向圖。本文的改進單極子天線水平放置(XOY平面),在輻射單元下方有損耗較大的硅基襯底及金屬地板結構,使得天線能量主要向+Z軸方向輻射。

圖7 天線94 GHz頻點處仿真3D輻射方向圖

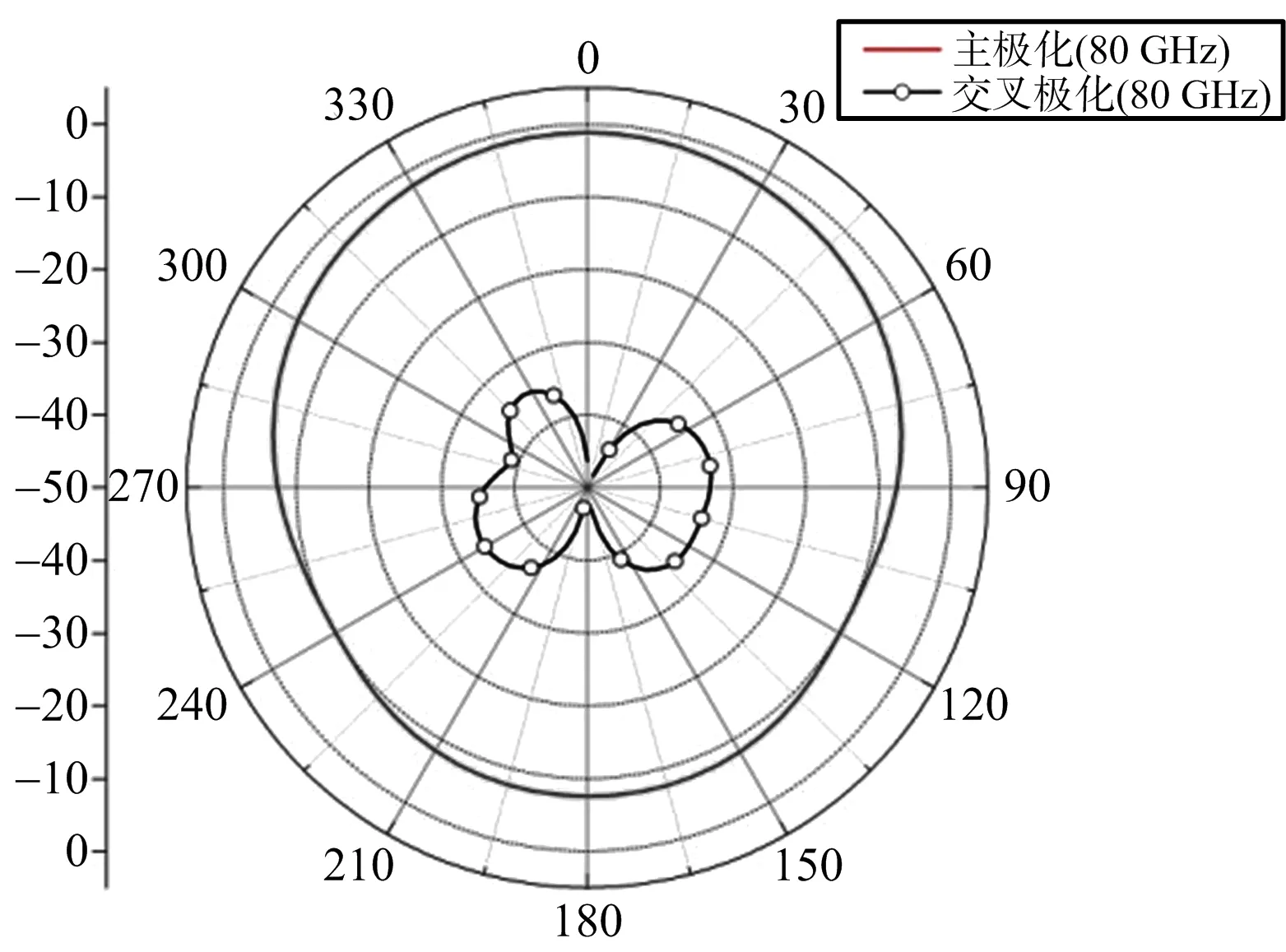

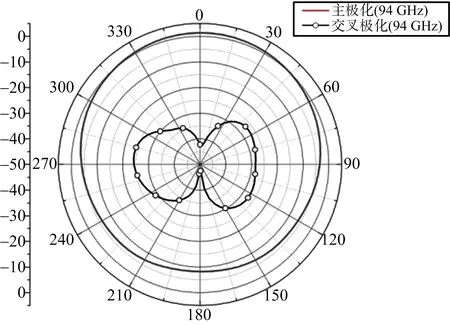

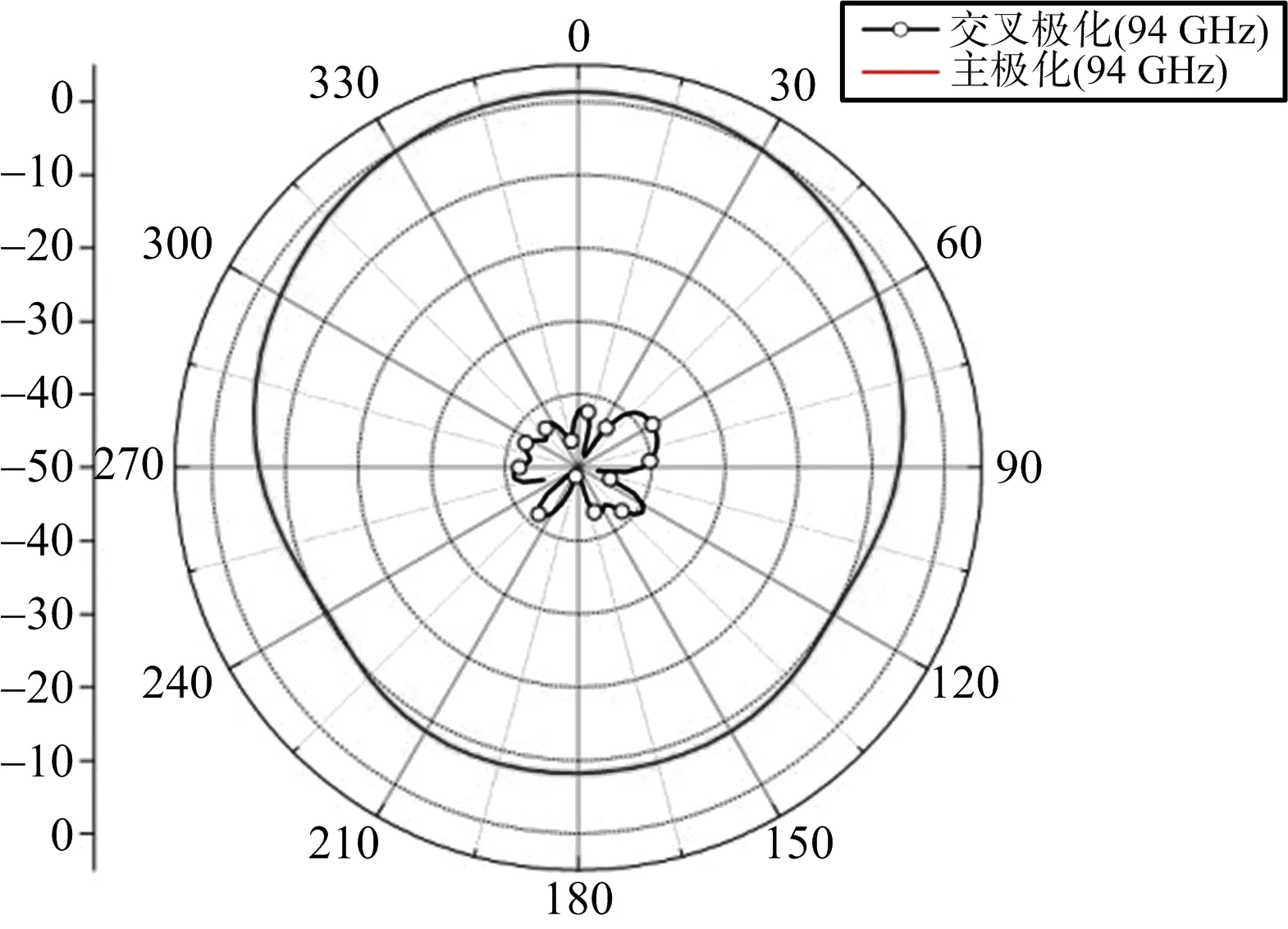

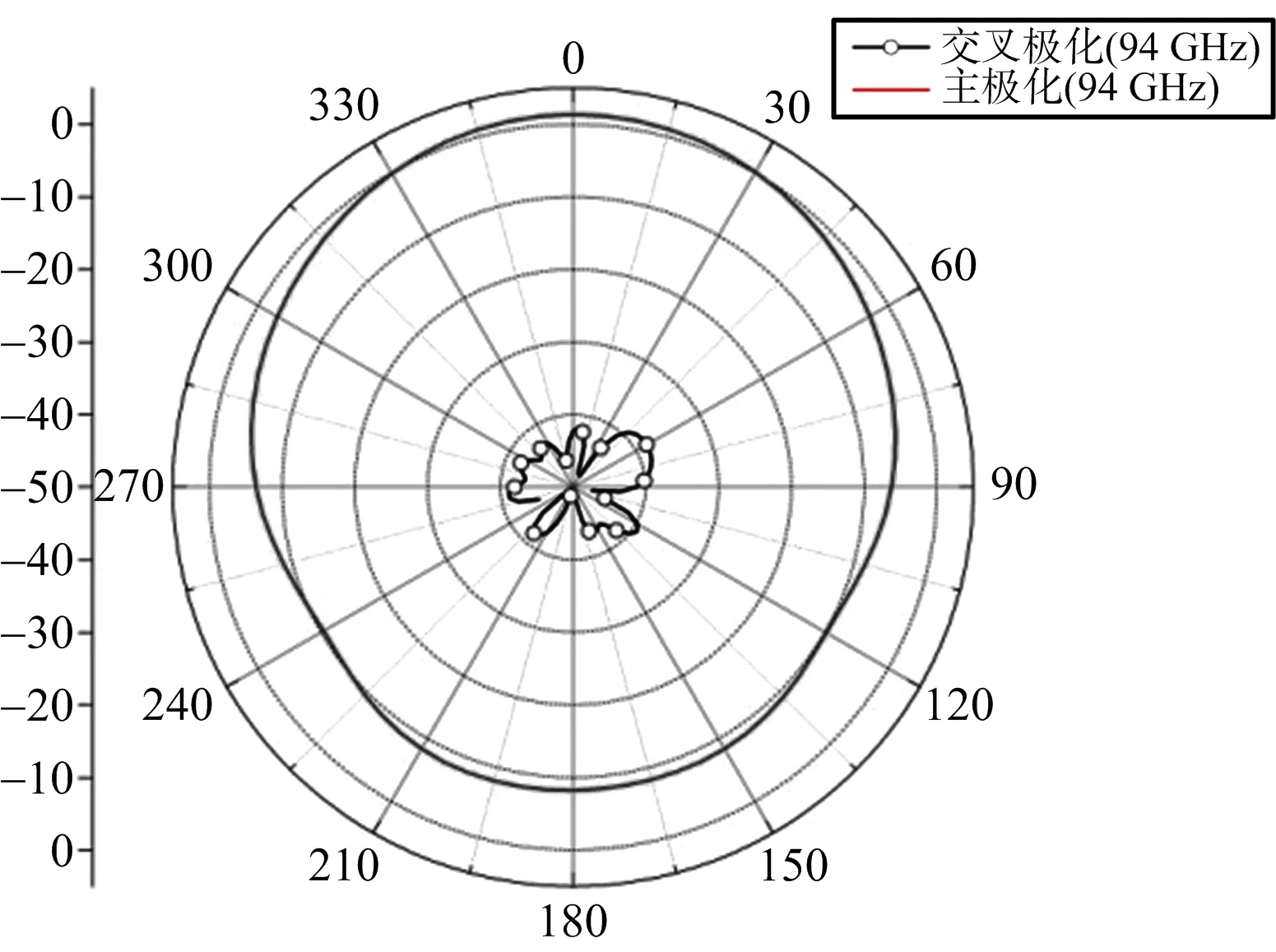

圖8給出了天線在80 GHz,94 GHz以及110 GHz三個頻點處的E面(YOZ平面)和H面(XOZ平面)的主極化與交叉極化方向圖。該天線在80 GHz處E面的3 dB波束寬度為110°,H面3 dB波束寬度為120°;在94 GHz處E面的3 dB波束寬度為90°,H面3 dB波束寬度為130°;在110 GHz處的E面3 dB波束寬度為102°,H面3 dB波束寬度為160°。

XOZ平面

YOZ平面(a) 80 GHz

XOZ平面

YOZ平面(b) 94 GHz

XOZ-平面

YOZ平面(c) 110 GHz圖8 天線仿真方向圖

圖9給出了該天線在工作帶寬內的仿真增益特性和輻射效率。該天線在94 GHz頻點處的增益為1.35 dB,效率為46.3%。在工作帶寬為77~117.6 GHz內天線增益大于-2 dBi,天線效率大于25%。

圖9 天線仿真增益帶寬和輻射效率

4 天線性能對比

表4給出了本文設計的片上天線與已發表文獻中的幾種基于CMOS工藝的片上天線性能的對比。本文提出的基于0.18 μm CMOS工藝的94 GHz片上天線具有較寬的阻抗帶寬以及較高的輻射增益。

表4 與部分已發表文獻中的基于CMOS工藝片上天線的性能對比

5 結束語

本文設計了一種基于0.18 μm CMOS 工藝的94 GHz寬帶片上天線,通過采用全波仿真軟件HFSS,分析片上天線襯底不同尺寸對天線阻抗和輻射性能的影響,為天線及天線陣列設計提供分析數據。本文所設計的天線其相對阻抗帶寬為45.5%,94 GHz頻點處的增益為1.35 dBi。該天線具有工作頻帶寬、輻射性能好等特性,可實現天線與IC芯片的一體化片上集成,滿足寬帶無線通信系統或毫米波雷達系統高集成度、小型化的應用需要。