基于PSoC編碼檢測器的設計及實現

2018-07-31 01:33:58劉亦萍李德運何學誠陳陶龍康楊奇凡

電氣自動化

2018年2期

劉亦萍, 李德運, 何學誠, 陳陶, 龍康, 楊奇凡

(上海第二工業大學 工學部,上海 201209)

0 引 言

CYPRESS公司在全球率先實現了在單芯片內的“模擬和數字全混合陣列”[1],對未來電子系統的設計方法產生了深遠的影響,在半導體技術高速發展的今天,芯片集成度越來越高,使得在單芯片上實現復雜系統成為可能,Cypress公司率先在業界實現了完全意義上的PSoC解決方案,即在單芯片上實現了MCU、數字和模擬系統的高度集成[2]。PSoC技術的不斷發展將大大推動電子系統設計方法的創新,并且對未來嵌入式系統設計領域帶來深遠的影響。

本項目研究有限自動狀態機(Finite State Machine,FSM),利用摩爾狀態機設計編碼檢測器[3],用PSoC芯片實現數字編碼檢測器。

本文將介紹通過控制邏輯電路,對計數器控制查找表產生的1001序列進行檢測,再通過編寫代碼實現在LCD屏幕上顯示出檢測到1001的次數。圖1是編碼檢測系統總框圖。

圖1 編碼檢測系統總框圖

1 檢測信號發生

圖2中a模塊是設計集成的十六進制計數器,通過Q3,Q2,Q1,Q0狀態輸出控制查找表LUT實現所需1001信號的發生[4]。

圖2 信號發生集成圖

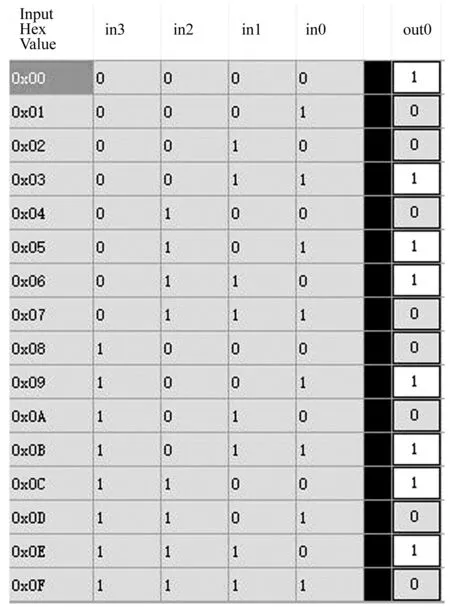

圖3為由查找表設計的檢測信號,in3,in2,in1,in0為Q3,Q2,Q1,Q0控制,Out0為檢測信號的輸出,其中含有2個1001序列。

圖3 1001檢測信號設計

2 序列檢測模塊

設計1001序列檢測器的邏輯電路圖[5],因為檢測器通過分析有5種獨立的狀態,所以使用了3個D觸發器(當n=3時會產生23=8種狀態)。

表1是檢測器的狀態轉換表,狀態轉換表列出了數據輸入端(Data_In)情況,并且狀態機將隨著輸入信號變化到兩種可能的下一狀態中的其中一個。……

登錄APP查看全文

猜你喜歡

鴨綠江(2021年35期)2021-04-19 12:24:18

考試與評價·高一版(2020年6期)2020-11-02 02:45:24

藝術啟蒙(2018年7期)2018-08-23 09:14:18

電子制作(2018年11期)2018-08-04 03:25:42

海峽姐妹(2017年7期)2017-07-31 19:08:17

Coco薇(2017年5期)2017-06-05 08:53:16

海峽科技與產業(2016年3期)2016-05-17 04:32:12

鑿巖機械氣動工具(2016年3期)2016-03-01 04:00:25

舒適廣告(2008年9期)2008-09-22 10:02:48