一種具有分段曲率補償的帶隙基準電路

秦晉豫 ,呂 堅 ,周 云 ,闕隆成 ,田 雷

(1.電子科技大學光電科學與工程學院,成都610054;2.中國電子科技集團公司第四十九研究所,哈爾濱150009)

1 引言

隨著深亞微米集成電路技術的不斷發展,芯片集成規模越來越大,為了保證整體系統的正常工作,帶隙基準源的精度起著至關重要的作用,它的溫度特性直接決定了整體電路的精度和性能。而傳統的帶隙基準源通常采用一階的補償方法,其溫度系數在20~100ppm/℃,傳統的帶隙基準無論在精度、穩定性,還是在功耗上,都遠遠無法滿足現在微電子系統的需求。因此,提高帶隙基準源的精度是十分重要的[1-3]。

針對傳統帶隙基準源的問題,已經有很多人提出了曲率補償的辦法。文獻[4]用具有不同溫度特性的電阻對基準源進行曲率校正,但是過分依賴于電阻的溫度特性,對工藝要求較高。文獻[5]提出一種低壓曲率補償基準電壓源,但是該電路使用的晶體管多,結構復雜。文獻[6]提出一種具有高的PSRR的曲率補償電路,但是該補償電路經過曲率補償后,精度提升小,電路結構復雜,極大地增加了系統的功耗。采用分段曲率補償技術在傳統Borkaw帶隙基準源的結構上進行改進,對帶隙基準電壓溫度特性曲線在高、低溫段進行曲率補償,得到一種結構簡單、功耗低、具有高精度的溫度特性的基準源。

2 傳統帶隙基準源結構和原理

雙極晶體管的基極—發射極電壓(PN結二極管)的正向電壓VBE具有負溫度特性。室溫下,有兩個雙極晶體管工作在不相等的電流密度下,它們基極-發射極電壓的差值就與絕對溫度成正比其中兩個雙極晶體管電流密度之比為n/1[7]。利用得到的正、負溫度系數電壓,可以得到一個零溫度系數的基準電壓將該式對溫度求導,選擇適當的系數K,使求導值在特定的溫度下為0,從而得到零溫度系數的基準電壓。

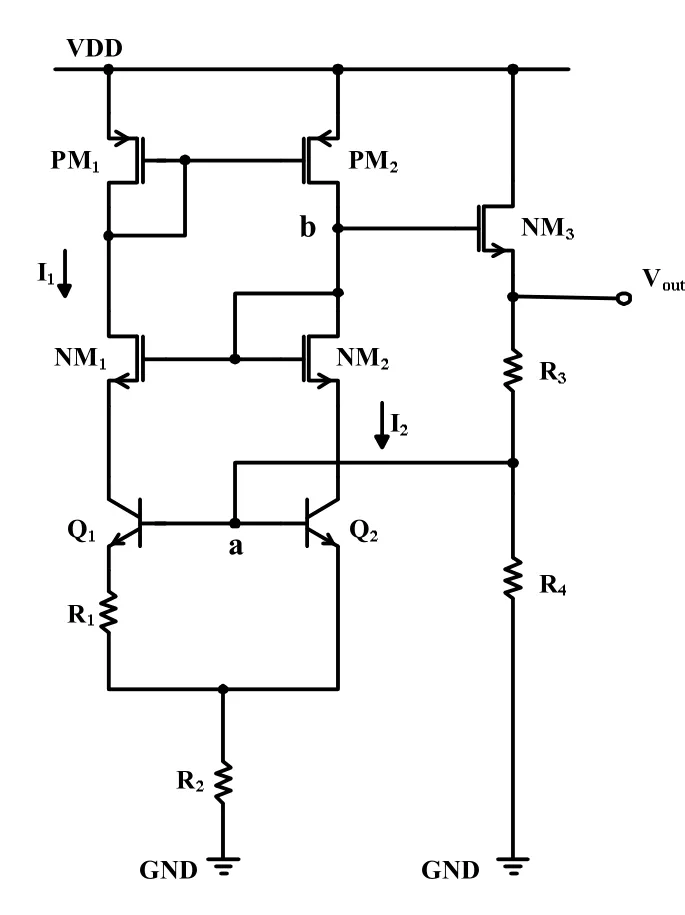

基于上述原理,已經有很多經典的帶隙基準電路產生,其中傳統Brokaw結構的具有較好的溫度特性溫度。傳統的Brokaw結構示意圖如圖1所示。

圖1 傳統Brokaw帶隙基準結構示意圖

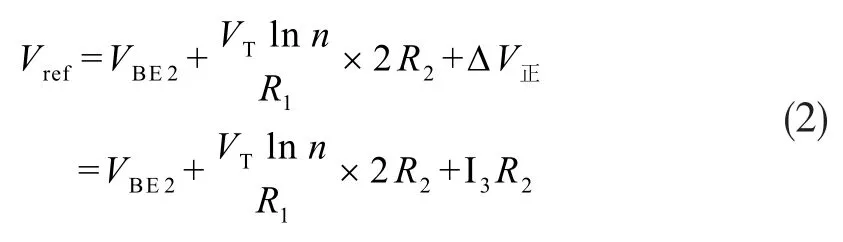

Borkaw帶隙基準電壓源是1974年由A.Paul Brokaw在Widlar帶隙基準電壓源的基礎上提出來的。與Widlar帶隙基準電壓源相比較而言,Brokaw基準可以產生兩倍的PTAT電流,減小了Q1和Q2大的發射區面積比所帶來的器件失配,具有更好的電壓溫度特性[8-9]。如圖 1 所示,PM1、PM2和 NM1、NM2構成電流鏡,產生與電源無關的偏置,保證流過Q1和Q2的電流其中,所以兩倍的正溫度電流I1流過R2產生正溫度系數電壓可以得到基準電壓為:

將上式對溫度求導,并在室溫下令等式結果為零,就可以確定出所需的R2和R1的比值,從而得到室溫下溫度系數為零的參考電壓。

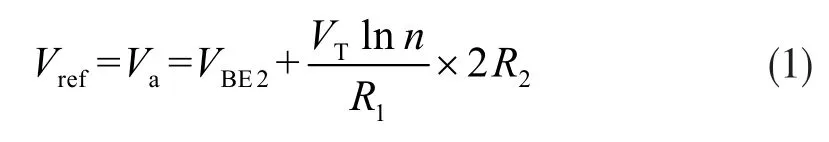

由圖2的傳統帶隙基準結構的仿真結果,可以看出,傳統的帶隙基準電壓源在-40~+125℃的溫度范圍中,最大和最小值之差僅為7.519mV,平均溫度系數為37.07ppm/℃,該傳統的帶隙基準源在精度上已經無法滿足大規模集成系統的要求。同時,該傳統帶隙基準結構在室溫下溫度系數為零,當溫度大于或者小于室溫時,負溫度系數大于正溫度系數,導致參考電壓減小,造成精度減小。所以提出的改進型帶隙基準源結構在溫度大于或者小于室溫時,分段對正溫度系數進行補償,以此提高帶隙基準電路的精度。

圖2 傳統Brokaw帶隙基準結構的仿真結果

3 改進型帶隙基準源結構

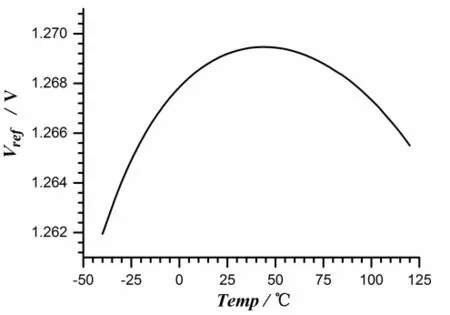

針對傳統的Borkaw帶隙基準電壓源精度低,同時芯片集成規模越來越大,幾個系統集成于一個芯片中,對帶隙基準電壓源的要求高。設計一種改進型的帶隙基準源結構,通過這一結構,可在溫度大于或者低于室溫時,對正溫度系數進行分段補償,從而提高帶隙基準源的精度。這一改進型帶隙基準源的具體結構如圖3所示。

圖3 改進型帶隙基準源結構示意圖

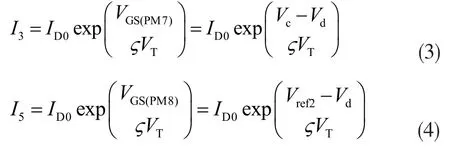

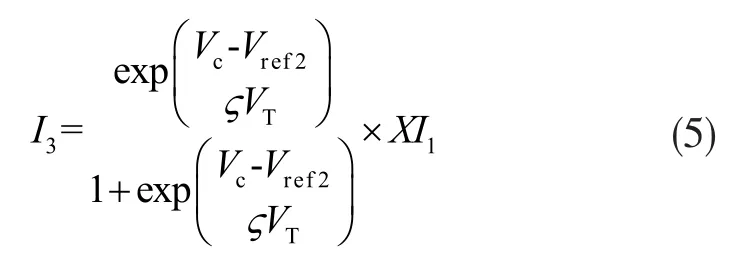

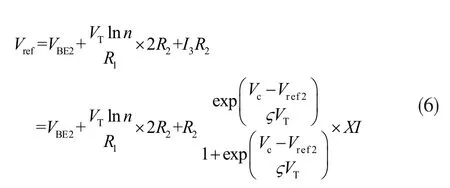

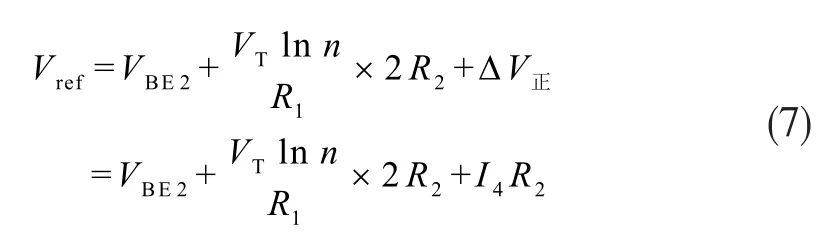

圖中,由 PM1、PM2、NM1、NM2、Q1、Q2、R1、R2構成帶隙基準核心電路,該核心電路的工作原理與上述傳統帶隙基準電路相同;虛線框內所示的電路為溫度補償電路,由PM3、PM4與PM1構成電流鏡,流過PM3電流為X倍的I1電流,流過PM4的電流為Y倍的I1電流,(其中式中n表示Q1的有效發射面積是Q2的n倍)。當溫度小于室溫時,Vc電壓降低,與Vref1和Vref2比較(其中電流I4趨近于0,I3電流增大,補償正溫度電壓為所以在低補償后的Vref為:

其中,當溫度小于室溫時,PM7和PM8工作在亞閾值區,得到下式:

將式(5)帶入式(2),可得在低于室溫時,補償后的基準電壓:

選擇合適的Vref2值和X值,產生合適的正溫度補償電流I3,從而對基準電壓源進行合適補償。

當溫度大于室溫時,Vc電壓升高,與Vref1和Vref2比較(其中電流 I3趨近于0,I4電流增大,補償正溫度電壓為所以在高溫補償后的Vref為:

其中,當高溫時的分段補償正溫度系數電流I4的推理與低溫補償電流I3的推理同理,選取合適的Vref1和Y值可以得到合適的補償電流I4,從而對基準電壓源進行合適補償。

4 改進型帶隙基準源仿真結果與分析

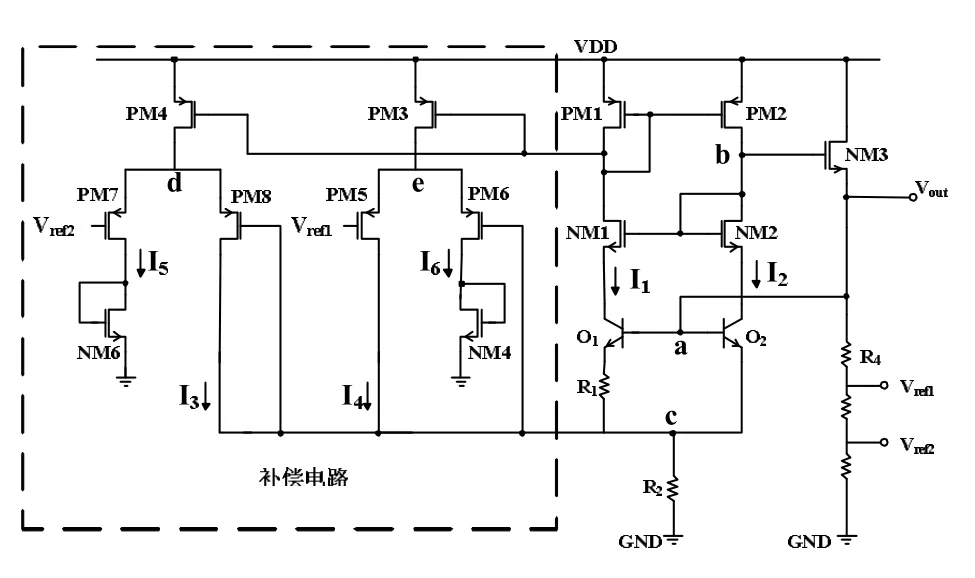

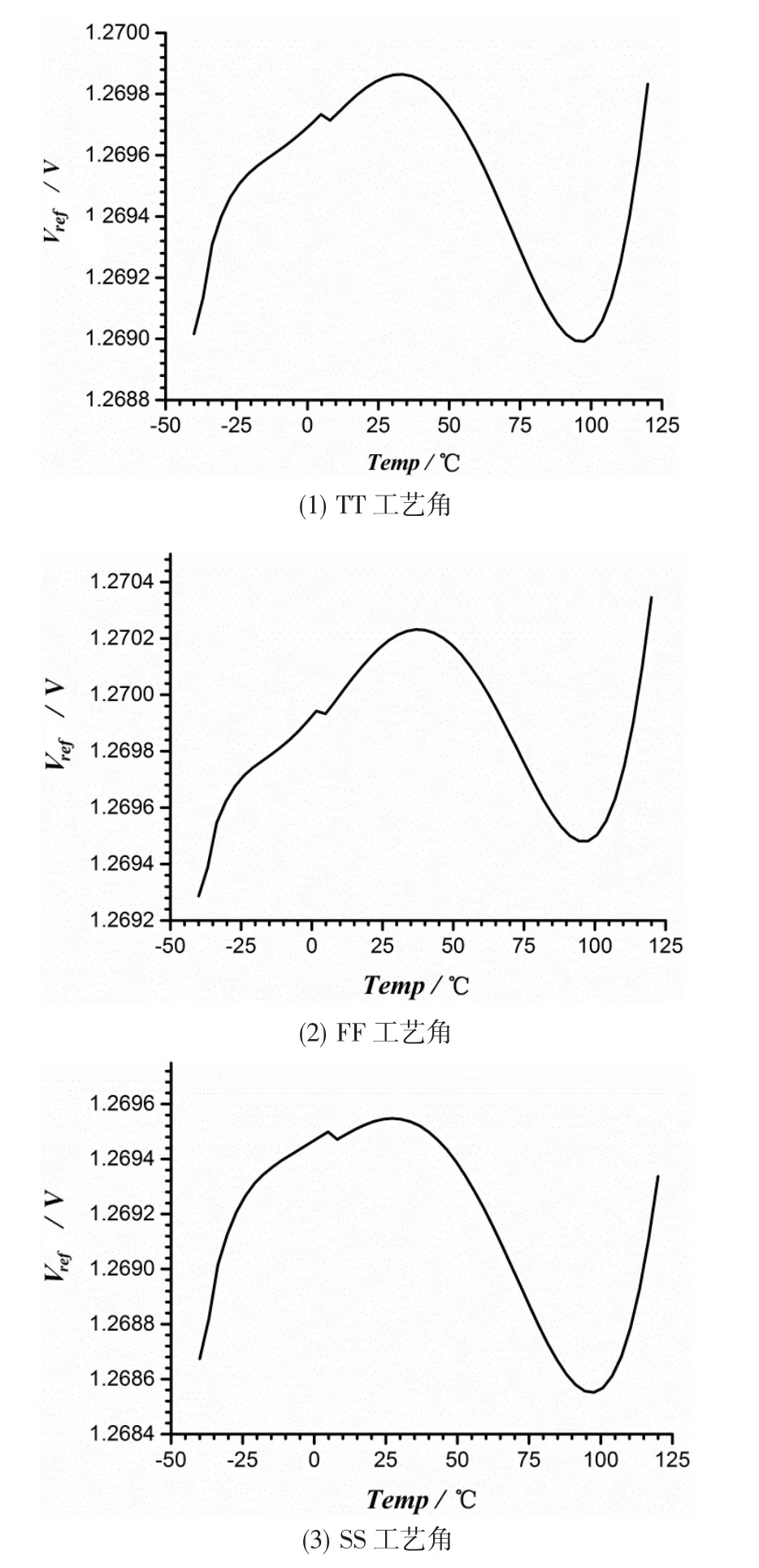

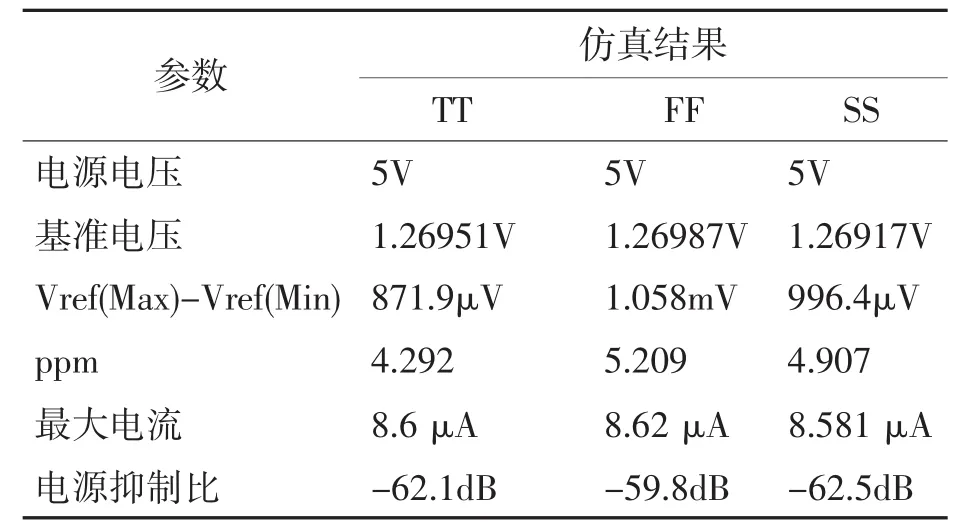

基于Nuvoton的0.35μm BCD工藝模型,使用Cadence的Specture工具對電路進行仿真分析。圖4給出了在高溫和低溫下,補償的正溫度系數電流曲線。圖5給出了在TT、FF、SS的工藝角下,補償后的帶隙基準電壓溫度特性曲線。仿真數據結果見表1。

圖4 高溫、低溫下補償的正溫度系數電流曲線

仿真結果表明,在不增加電路的復雜性的基礎上,可實現一種具有高精度的帶隙基準電路。經過在低溫和高溫分段正溫度系數電流的補償,在-40~+120℃的溫度范圍中,最大和最小值之差僅為871.9μV,平均溫度系數為4.292ppm/℃。從表1的結果可見,在不同的工藝角下仿真,改進型帶隙基準電路具有良好的穩定性。

圖5 輸出基準電壓在不同工藝角下的溫度曲線

表1 帶隙基準源在不同工藝角下的仿真結果

5 結束語

分析傳統Brokaw帶隙基準電路和改進型溫度補償帶隙基準電路,在理論上闡述了傳統帶隙基準源在高溫和低溫下基準電壓隨溫度變化大的不足,提出了一種具有正溫度補償的改進型帶隙基準電路。通過一系列仿真結果顯示,經過正溫度系數補償,帶隙基準電壓的溫度系數明顯減小,帶隙基準源精度得到了提高。改進型帶隙基準電路可以很好地滿足集成電路系統對帶隙基準源的低溫度系數日益增長的需求。

參考文獻:

[1]CHAHARDORI M,ATARODI M,SHARIFKHANI M.A sub 1V high PSRR CMOS bandgap voltage reference[J].Microelectronics Journal,2011,42(9):1057-1065.

[2]李睿,馮全源.一種高性能曲率補償帶隙基準源的設計[J].微電子學,2016,03:328-331.LI Rui,FENG Quanyuan.Design of a high performance curvature compensation bandgap reference[J].Microelectronics,2016,03:328-331.

[3]LIU Xi,LIU Qian,JIN Xiaoshi,et al.Negative voltage bandgap reference with multilevel curvature compensation technique[J].Journal of Semiconductors,2016,37(5):055008.

[4]SANBORN K,MA D,IVANOV V.A Sub-1V low noise bandgap voltage reference[J].IEEE Journal of Solid-State Circuits,2007,42(11):2466-2481.

[5]SU Kai,GONG Min,QIN Huaibin,et al.A multiple transistor combination low-voltage curvature-corrected bandgap reference[J].Journal of Semiconductors,2013,34(6):065010.

[6]ZHOU Q,YAN K,LIN J,et al.Novel high-PSRR highorder curvature-compensated bandgap voltage reference[J].Journal of China Universities of Posts&Telecommunications,2016,23(2):66-72.

[7]畢查德·拉扎維.模擬CMOS集成電路設計[M].陳貴燦,程軍,張瑞智,等譯.西安:西安交通大學出版社,2002.RAZAVI B.Design of Analog CMOS and Integrated Circuits[M].CHEN Guican,CHENG Jun,ZHANG Ruizhi,et al,transl.Xi'an:Xi'an jiaotong university press,2002.

[8]BROKAW A P.A simple three-terminal IC bandgap reference[J].IEEE Journal of Solid-State Circuits,1974,9(6):388-393.

[9]楊琦,張國俊.一種帶有數字修調的高精度帶隙基準電路[J].微電子學,2016,03:320-323.YANG Qi,ZHANG Guojun.A high precision bandgap reference circuit with Digital Trimming[J].Microelectronics,2016,03:320-323.