TEOS的應用對接觸電阻的穩定性問題研究

闞志國,周衛宏

(華越微電子有限公司,紹興312000)

1 引 言

在Bipolar IC中,由于發射區注入工藝具有結深易控、橫向擴散小的特點,往往被應用在特征尺寸小或淺結工藝的產品中。這類工藝熱氧化擴散后生長的氧化膜厚度較薄,通常需要再淀積一層氧化膜作為金屬布線下方的隔離介質。

華越生產線主要以中溫LPCVD SiO2(以下簡稱LP-SiO2)作為金屬布線下方的疊加介質層,由于這種工藝的LPCVD爐管溫度梯度大,導致發射區結深波動大,使得部分產品表現出片間放大倍數(β值)波動大。經分析論證,使用相比此工藝的爐管溫度低、梯度小的低壓熱解TEOS(正硅酸乙酯)工藝方法淀積SiO2(以下簡稱TEOS),可以有效減小放大倍數(β值)的波動性。此替代工藝實施后,產品放大倍數(β值)改善明顯。但是隨著后續產品種類增加,批量生產過程中陸續出現接觸電阻不穩定的問題。問題嚴重的,表現出工藝監測數據接觸特性open,直接影響產品及加工的穩定性,增加上機失效的風險。

2 現象及原因分析

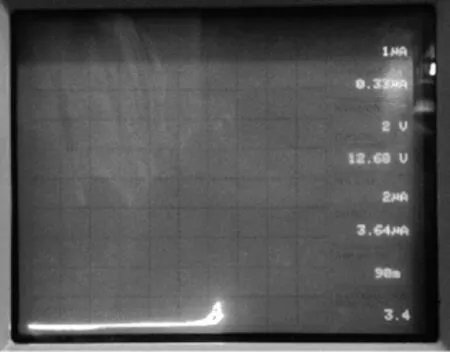

此種接觸電阻的不穩定性問題,隨著應用TEOS不同產品的上量,表現的越來越突出。同一工藝平臺生產的產品有好有壞,統計發現特征尺寸越小的產品,接觸電阻異常現象表現的越嚴重,嚴重異常出現時的工藝監控測試接觸電阻曲線如圖1,即使將測試電壓加至300V左右仍顯示電阻值無窮大。

圖1 N型接觸電阻異常曲線

由測試數據和曲線看,極大可能是金屬與孔間的歐姆接觸[1]出了問題,而根據理論和實踐分析,影響此類問題主要涉及幾種情況:

1)在干法刻蝕時,反應生成的有機聚合物難以去除,導致其殘存在孔內形成高阻夾層;

2)有較厚的SiO2殘留在接觸孔內,從而接觸電阻顯著增加;

3)刻蝕孔的臺階形貌不良[2],使得濺射金屬層未與孔形成有效接觸。

3 實驗設計與結果

為了找到TEOS引起接觸電阻波動的真正原因,進而有針對性的解決問題。根據上述分析結果,將“孔內存在難去除生成物”、“孔內氧化層殘留”及“孔形貌影響金屬覆蓋性”三種影響因素作為重點進行實驗比對分析。

3.1 孔內難去除生成物分析

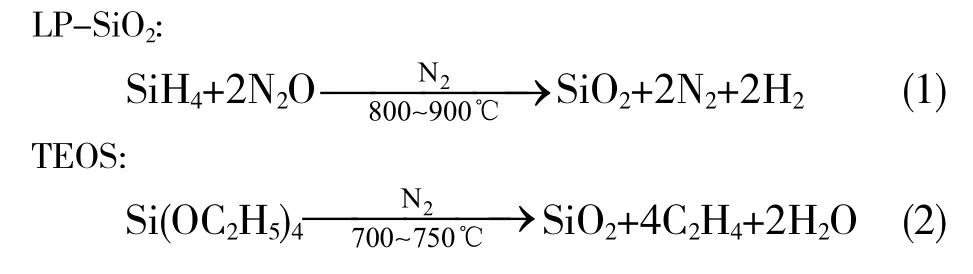

由于采用LP-SiO2介質層時無此類問題,主要對TEOS與LP-SiO2的生長產物對比分析,此兩種膜質的生長淀積標準化學式[3]如下:

以上反應生成物都屬于易刻蝕、易揮發的物質,未生成難以去除的有機聚合物。再對兩種膜質進行模擬淀積,并在刻蝕后對接觸孔進行染色觀察,孔內顏色一致。因此,首先排除TEOS工藝孔內存在難刻蝕生成物。

3.2 孔內氧化層殘留分析

如果孔內有氧化層殘留,那么可能的原因有兩個:其一,刻蝕時間不充分,即過刻量不足;其二,殘留光刻膠底膜,阻擋有效刻蝕。

TEOS工藝孔刻蝕的標準過刻蝕時間為30%,針對第一點可能性,進行工藝拉偏驗證,設計過刻蝕時間以10%為梯度,逐級增加至100%,后續工藝按標準工藝進行流水完成,然后進行參數評測,結果所有結果均NG。針對第二點可能性,首先進行帶膠圖形產品顯微鏡鏡檢,在鏡檢無異常發現的情況下,進行光刻膠底膜預灰拉偏驗證[4]。生產線常規的光刻膠預灰時間為2分鐘,設計預灰時間以1分鐘為梯度,逐級增加至10分鐘,后續仍按標準工藝進行流水完成并進行參數評測,結果仍是均NG。以上實驗說明孔內不可能有氧化層殘留。

3.3 孔形貌影響金屬覆蓋性分析

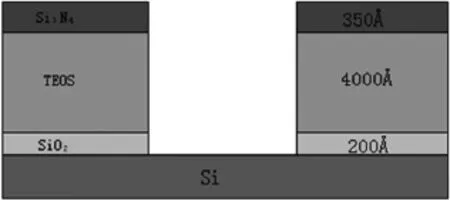

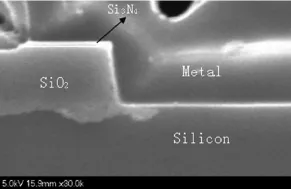

以上兩項實驗結果證明接觸電阻不穩定的主要原因可能是孔形貌影響了金屬的覆蓋性。首先,需要明確孔的介質層結構和介質層的刻蝕特性。接觸孔的介質層結構見圖2。

圖2 接觸孔的介質層結構示意圖

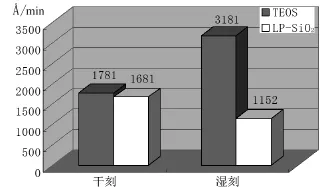

由圖2可知,表層是一薄層Si3N4(此類產品設計用Si3N4做電容,而且不需要Si3N4反刻),中間是最厚的TEOS,最下層是極薄的SiO2。由于出現接觸電阻的穩定性問題是由TEOS替代LP-SiO2所引起,因此,重點對TEOS與LP-SiO2的干刻和濕刻特性進行比對分析。制備樣片,進行相同條件實驗,記錄兩者干刻和濕刻的速率,對比結果見圖3。

圖3數據顯示TEOS和LP-SiO2的干法刻蝕速率很接近。但是TEOS的濕法腐蝕速率特別快,同一腐蝕液中速率是LP-SiO2的2.8倍[5],這就意味著其橫向腐蝕量較大。

按照傳統工藝,對于用Si3N4做電容的產品,孔刻蝕的工藝為干法主刻+濕法后處理。這里的濕法,通常為在BOE(緩沖氧化硅腐蝕液)中腐蝕30秒。由于在干法中介質層已刻蝕干凈,濕法屬于一個過刻的后處理過程。

圖3 TEOS和LP-SiO2的干法和濕法刻蝕速率

而BOE對Si3N4是無腐蝕性的,這樣一來很可能使得Si3N4下面橫向被切入,影響孔的臺階形貌,導致金屬的覆蓋性差。但是,濕法后處理畢竟時間很短,實際會有多大的影響呢?

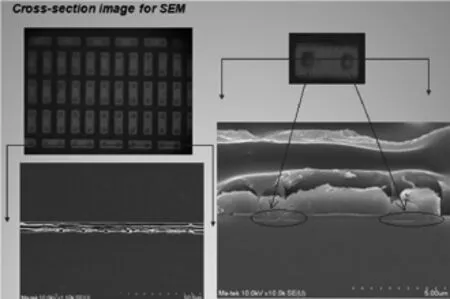

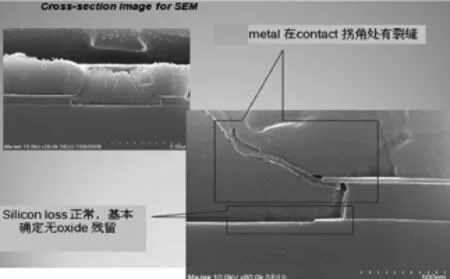

于是,按標準工藝設計實驗進行仿真模擬加工,同時針對較小的2μm×2μm的接觸孔做掃描電鏡(SEM)來分析斷面的形貌,如圖4和圖5。

圖4 2μm×2μm的接觸孔縱向剖面

圖5 2μm×2μm的接觸孔局部放大剖面

由圖5放大剖面觀察,孔內無異物而且硅也存在一定的過刻量,證明了經分析后得出的接觸電阻不穩定并不是孔內有難刻蝕的生成物,也不是孔內有氧化層殘留的結論是正確的。

同時,圖片中發現窗口處金屬Al有明顯裂縫,嚴重影響接觸特性。原因就是:BOE對TEOS的濕法腐蝕速率甚大[6],而對Si3N4基本無腐蝕性,使得TEOS橫向腐蝕較深,留下了一段明顯的Si3N4“翹板”[7],正是這段氮化硅,造成了在金屬Al濺射時形成覆蓋死角,甚至留下斷裂縫隙。

綜合以上的實驗分析,知道了TEOS替代LP-SiO2導致接觸電阻不穩定的根本原因。同時由于BOE的速率是在一定的區間內波動的,所以“底切”[8]的量也會隨之相應波動,而且特征尺寸越小的產品越敏感,最終導致接觸電阻隨之波動,表現出穩定性差。

4 解決方案與驗證結果

4.1 解決方案

為解決TEOS的應用對接觸電阻的穩定性造成影響的問題,主要需要對現有接觸孔刻蝕工藝細節進行優化改進:

1)在有Si3N4電容工藝時,BOE對TEOS接觸孔形貌的影響是致命性的,所以接觸孔的刻蝕過程需要將原工藝的濕法30秒后處理取消。

2)為了保證過刻蝕充分,將干法Over etch 30%提升為Over etch 40%。

3)Al濺射有含HF的前處理工藝,這也相當于一步濕法腐蝕的過程,同樣存在風險。原Al前處理時間為25秒,為了避免出現橫向“底切”現象,將前處理時間縮減為10秒。

4.2 產品驗證及統計結果

按解決方案的流程仿真加工,并通過掃描電鏡分析接觸孔的實際形貌,見圖6。

圖6 改善后的接觸孔剖面

可見,經過工藝細節優化改進,接觸孔形貌良好,未出現“底切”現象,Al覆蓋良好。

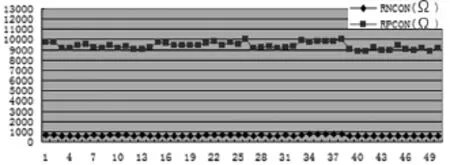

經上述措施改善后,對應用TEOS產品的50個LOT進行接觸電阻測試統計,具體數據見圖7。

圖7 N型和P型接觸電阻數據統計

產品設計規則要求N型接觸電阻1kΩ以下,P型接觸電阻12kΩ以下。圖7顯示,RPCON、RNCON接觸電阻參數完全在規格值內,而且非常穩定,滿足產品要求。同時實測的產品成品率亦很高。

5 結束語

對于TEOS的應用對接觸電阻出現穩定性問題,進行了一系列工藝分析論證,結果表明:對于TEOS和Si3N4的介質層組合(尤其是特征尺寸在2微米及以下的產品),在孔刻蝕工藝加工過程要采取相應措施規避含氫氟酸溶液的濕法處理,同時要保證足夠的過刻量;在金屬濺射前處理工藝時,務必合理控制、縮短前處理時間,同時避免前處理返工操作。

以上工藝細節的優化改進與實施,有效地解決了TEOS應用中接觸電阻大阻抗甚至open的不穩定性問題。

[1]王印月.半導體物理學[M].蘭州:蘭州大學出版社,1999.WANG Yinyue.Semiconductor physics[M].Lanzhou:Lanzhou University Press,1999.

[2]馬宏,鄭閩.用于VLSI的接觸孔/通孔形貌控制技術[J].微電子技術,1993,21(1):36-41.MA Hong,ZHENG Min.Shape control technology of contact holeandthroughholeforVLSI[J].MicroelectronicTechnology,1993,21(1):36-41.

[3]章曉文,恩云飛.半導體集成電路的可靠性及評價方法[M].北京:電子工業出版社,2015.ZHANG Xiaowen,EN Yunfei.Reliability and evaluation method method of semiconductor integrated circuits[M].Beijing:Publishing House of Electronics Industry,2015.

[4]潘桂忠.MOS集成電路工藝與制造技術[M].上海:上海科學技術出版社,2012.PAN Guizhong.MOS integrated circuit technology and manufacturing technology[M].Shanghai Scientific&Technical Publishers,2012.

[5]盧靜.集成電路芯片制造實用技術[M].北京:機械工業出版社,2011.LU Jing, Practical technology for integrated circuit chip manufacturing[M]. Beijing: China Machine Press, 2011.

[6]郭文濤,譚滿清,焦健,等.PECVD提高SiO2薄膜致密性的研究[J].人工晶體學報,2013,42(4):577-581.GUOWentao,TANManqing,JIAOJian,etal.Studyonimproving the compactness of SiO2thin film by PECVD[J].Journal of Synthetic Crystals,2013,42(4):577-581.

[7]恩云飛,來萍,李少平.電子元器件失效分析技術[M].北京:電子工業出版社,2015.ENYunfei,LAIPing,LIShaoping.Failure analysistechnology of electronic components[M].Beijing:Publishing House of Electronics Industry,2015.

[8]張汝京.納米集成電路制造工藝[M]. 北京:清華大學出版社,2017.ZHANG Rujing.Manufacturing technology of nanoscale integrated circuit[M].Beijing:Tsinghua University Press,2017.