真空燒結粘片芯片脫落失效分析

寇凌霄

(中國電子科技集團公司第四十七研究所,沈陽110032)

1 引言

真空燒結是指在一定的真空度下,利用熔點低于被焊接材料的合金做釬料,通過加熱使釬料熔化,靠毛細作用將液態焊料填充到焊接接觸面的間隙中,通過液態焊料與被焊金屬之間相互擴散溶解形成金屬間化合物,最后經過冷卻形成高可靠的焊接[1]。某型集成電路采用真空燒結工藝粘接芯片封裝后,進行篩選試驗和質量一致性檢驗。在質量一致性檢驗中分組試驗選取樣管開蓋試驗,發現樣管芯片碎裂、脫離底座。就此問題進行失效分析定位和失效機理分析,形成糾正措施以免再次發生失效。

2 故障描述

某型電路封裝完成后,進行了篩選試驗和質量一致性檢驗。篩選試驗程序按試驗順序包括高溫貯存、溫度循環、恒定加速度、電測試、老化、密封試驗。按規范要求質量一致性檢驗抽取15只樣管,在B4分組時按GJB 548B-2005方法2014對1只樣管進行內部目檢和機械檢查,開蓋后發現芯片碎裂。出現問題后對剩余的14只樣管進行開蓋處理,另有1只芯片碎裂,2只芯片脫離底座,11只樣管芯片無異常。

2.1 失效樣管描述

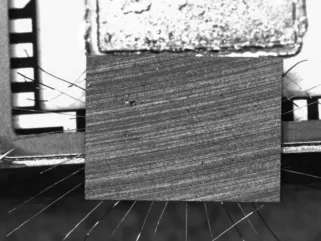

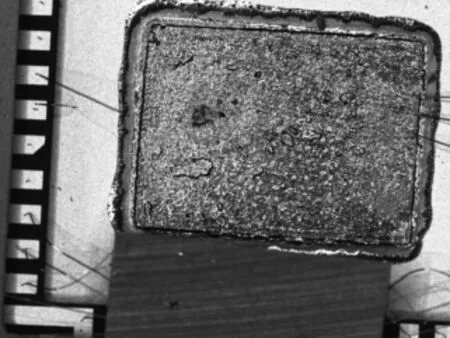

該電路采用真空燒結工藝粘接芯片,開蓋的失效電路在36倍顯微鏡下觀察失效電路內部結構,芯片背面及管殼焊接界面狀態見圖1、圖2。

圖1 失效電路的芯片背面狀態

圖2 失效電路的管殼焊接界面狀態

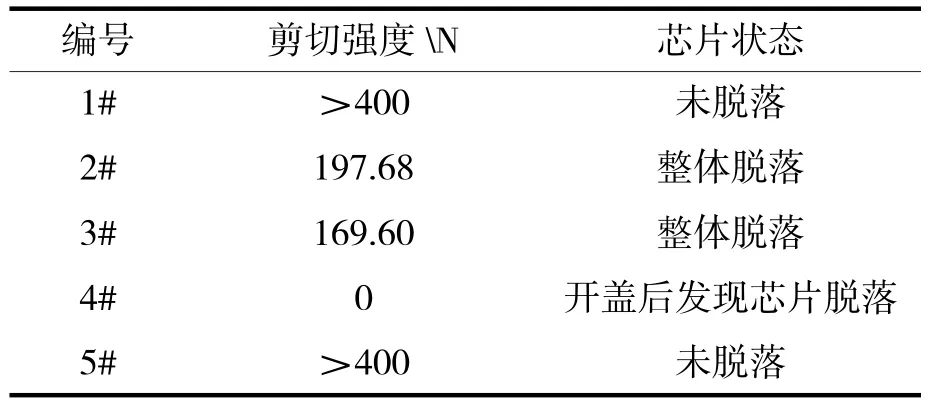

在開蓋芯片無異常的11只樣管中抽取5只(編號1#~5#)進行剪切強度試驗。使用剪切強度/鍵合強度測試儀進行剪切強度測量,測量方法及檢驗標準按照GJB548B-2005方法2019的要求執行[2]。為檢驗真空燒結粘片工藝的粘接強度是否異常,將剪切強度試驗量程設定為400N,確保試驗能將芯片剪切掉并得到實際數值。試驗結果見表1。

表1 芯片粘接剪切力強度

由表1可見,試驗結果顯示不同樣管之間剪切強度數值差別很大。芯片的剪切強度測試是判斷芯片粘接質量的常用方法。以芯片在應力作用下產生的失效類型,芯片脫離管座后殘留的芯片附著材料和管殼各粘接界面的形貌進行判斷。在此次剪切力試驗中,芯片粘接強度一致性很差,并且芯片脫離狀態不理想,無法滿足芯片粘接可靠性的要求。

2.2 加工過程追溯

該電路采用真空燒結工藝粘接芯片,原材料均檢驗合格并在有效期內;真空共晶回流焊粘接芯片設備正常運行,工藝溫度可控無異常;操作及檢驗人員均持證上崗;封裝過程在超凈間進行且環境滿足要求[3];篩選試驗和質量一致性檢驗的方法和條件均符合電路設計要求和GJB 548試驗方法。

3 故障定位

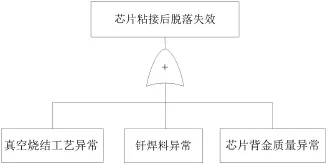

基于以上分析定位,該問題出現在真空燒結芯片粘接過程中,分析可得芯片粘接后脫落失效故障樹如圖3。

圖3 芯片粘接后脫落失效故障樹

3.1 故障排查

由故障樹可知,導致“芯片粘接后脫落失效”的故障有三種可能,下面分別進行排查。

3.1.1 對“真空燒結工藝異常”的排查

經查封裝記錄,該批問題電路封裝周期為2017年3月份至6月份。在同時期內,采用同種粘接工藝的某電路封裝1600只,封裝過程中真空燒結工藝參數、粘接材料(釬焊料)、設備狀態、人員配置、技術狀態均未發生變化。目前已完成篩選試驗及質量一致性試驗,篩選試驗程序與該問題電路篩選試驗程序一致,1600只電路未發生芯片脫落失效。通過以上排查,排除故障樹“真空燒結工藝異常”分支。

3.1.2 對“釬焊料異常”的排查

在排查故障樹“真空燒結工藝異常”分支的過程時,經查1600只某電路與問題電路采用同種、同批次粘接材料-釬焊料(Pb-In-Ag),未發生芯片脫落失效,因此,排除故障樹“釬焊料異常”分支。

3.1.3 對“芯片背金質量異常”的排查

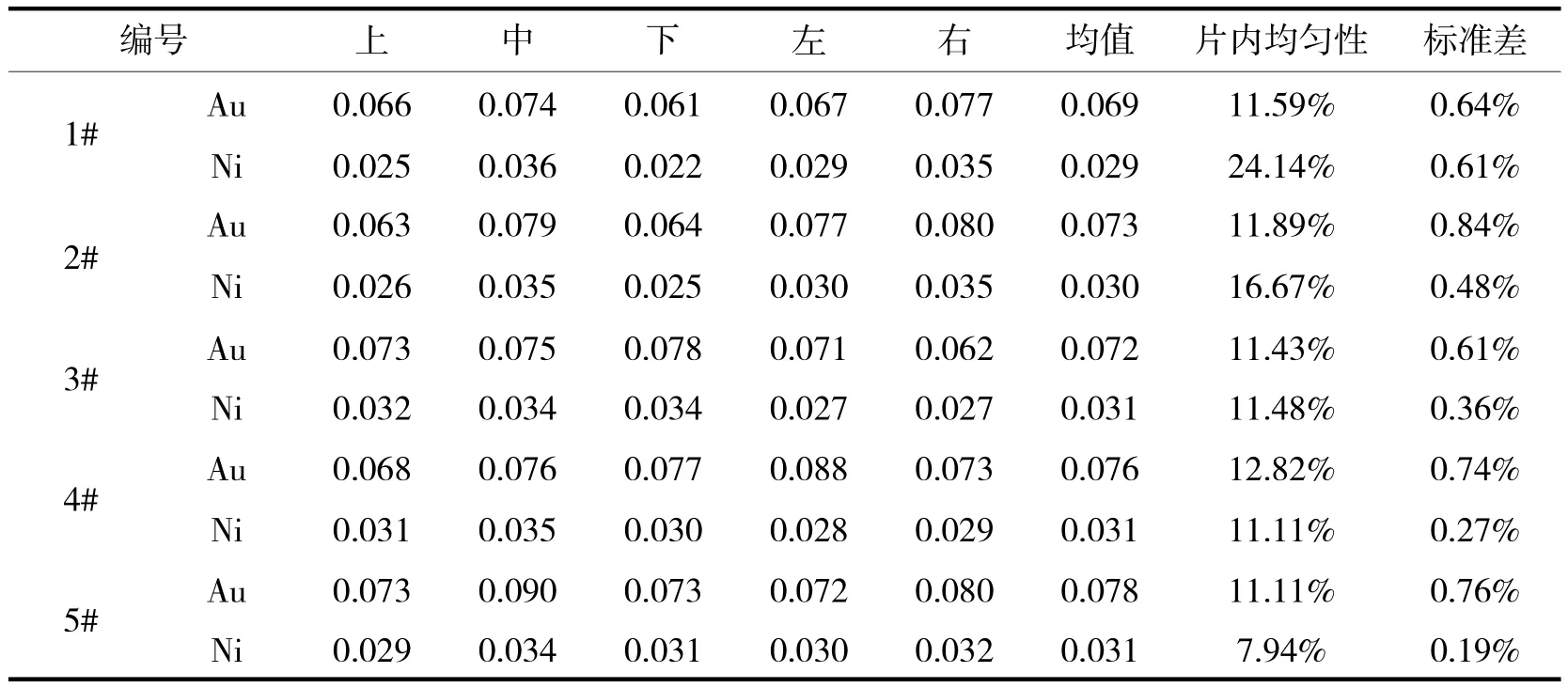

在該批電路未進行封裝的晶圓片中,隨機抽樣5片晶圓片(編號1#~5#),使用X射線熒光光譜儀測量晶圓片背金厚度。為檢驗問題芯片背金是否異常,每個晶圓片片選取測量上、中、下、左、右五個位置的背金厚度,確保試驗能測量出背金厚度并掌握其均勻性[4],測量結果見表2。

由表2可見,該電路背金層厚度約為鎳層0.022~0.035μm,金層 0.090~0.061μm。按照芯片加工背金工藝要求,背金為鎳-金兩層結構,技術指標應為鎳層 0.050μm,金層 0.300μm,鎳層、金層厚度均不符合工藝要求。由此,可確定“芯片粘接后脫落失效”是由于芯片背金厚度不足所致。

表2 問題電路芯片背金厚度 單位:μm

4 機理分析

金/鎳體系的一個獨有特點是它在組裝過程和隨后的使用壽命中暴露在較高溫度下時具有較好的穩定性[5]。若鍍層過薄或鍍層的均勻性差,鍍層對芯片表面的保護功能降低,導致芯片真空燒結粘片時芯片背金與釬焊料潤濕性較差,才會出現芯片背面無釬焊料殘留的現象。

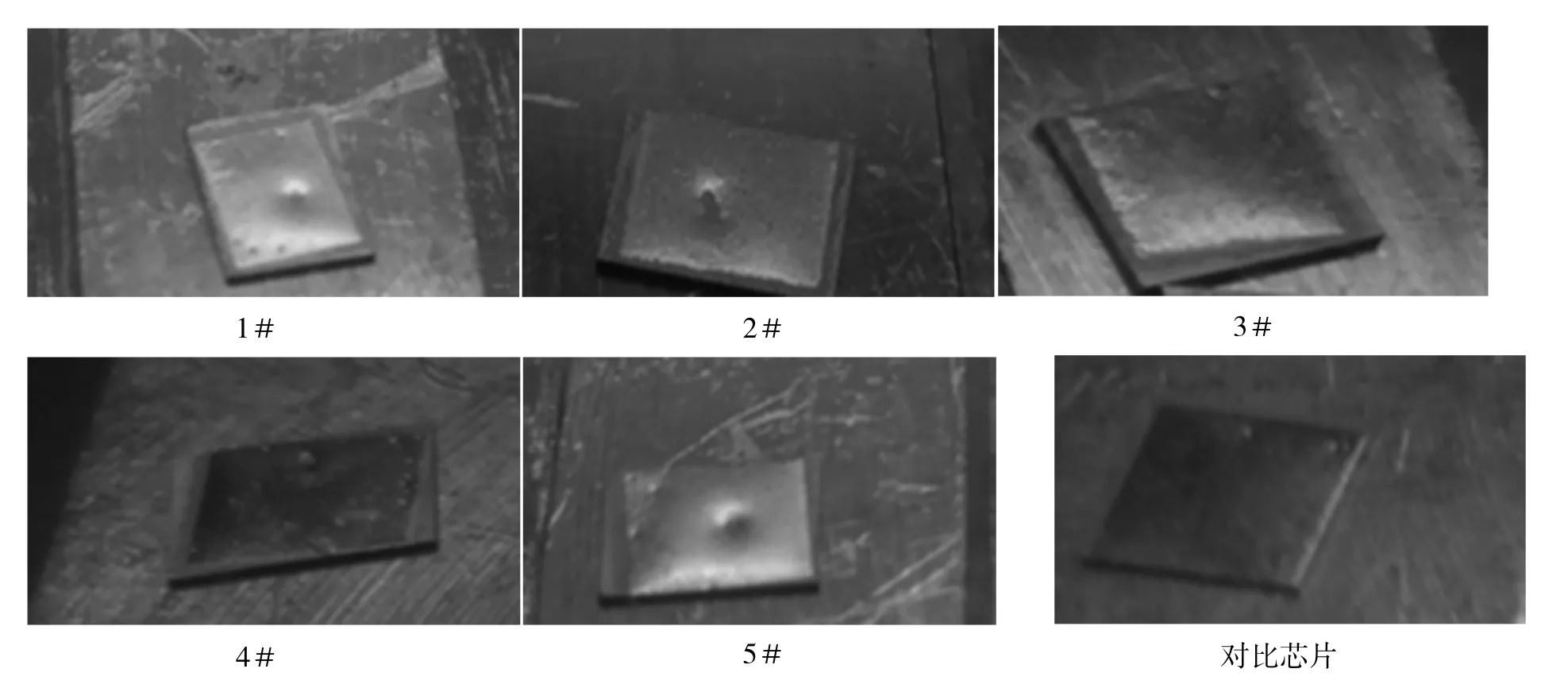

在該批電路未進行封裝的晶圓片中,隨機抽樣5只芯片(編號1#~5#),采用芯片背金可焊性試驗模擬真空燒結粘片過程,同時增加同種封裝工藝但不同時期加工的1只芯片,進行對比試驗。

抽樣芯片背金面向上并放置釬焊片,放進真空共晶回流焊設備里。按照真空燒結粘片工藝要求設定工藝參數,進行燒結。燒結完成后,觀察芯片背金與釬焊料潤濕狀態[6],真空燒結完成后芯片試驗照片如圖4。

圖4 釬焊料潤濕狀態比較

由圖4可見,熔融釬焊料在芯片背金表面鋪展開后又發生收縮,形成一個粗糙和不規則的表面,其表面上存在與薄釬焊料層相連的較厚釬焊料隆起現象[7]。對比芯片背金與釬焊料形成良好的潤濕,通過目檢可以看到背金表面上形成一個平滑、均勻和連續的釬焊料涂覆層,而抽樣芯片(1#~5#)圖片上出現粗糙、隆起和針孔現象。同時,在圖1和圖2中可見管殼上的釬焊料熔融形狀規則,表面平整,芯片背面無釬焊料殘留,呈現出暗銀色,釬焊料超出芯片棱邊的流淌區域寬度為1mm~2mm。

經上述試驗分析,該問題電路的背金質量在片間及片內存在較大差異。鎳層薄會影響鎳層活性,金層薄或不夠致密,造成空氣穿過金層將鎳層表面氧化,導致芯片可焊性差。真空燒結工藝粘片后,在篩選試驗過程中經過環境與應力試驗,將可焊性差的質量隱患放大,導致部分電路芯片脫落。

5 結束語

針對此次產品失效采取糾正預防措施,現已增加了背金工藝監控設備,確保芯片加工過程中背金工藝的穩定性。同時,封裝過程中加強了首件檢驗觀察及分析,對于較嚴重的背金質量問題,做到早期發現,減少損失,以達到提高成品率和可靠性[8],降低全壽命周期成本的目的。

[1]杜長華,陳方,黃福祥,等.電子微連接技術與材料[M].北京:機械工業出版社,2008.DU Changhua,CHEN Fang,HUANG Fuxiang,et al.Electronic micro bonding technology and materials[M].Beijing:China Machine Press,2008.

[2]劉洪濤.真空燒結技術研究[J].微處理機,2015,36(6):9-11.LIU Hongtao.Study on technology of vacuum sintering[J].Microprocessors,2015,36(6):9-11.

[3]杜中一.電子制造與封裝[M].電子工業出版社,2010.DU Zhongyi.Electronics manufacturing and packaging[M].Beijing:Publishing House of Electronics Industry,2008.

[4]胡正明.集成電路中的現代半導體器件[M].英文版.科學出版社,2012.Hu ChenmingCalvin.Modernsemiconductor devices for integratedcircuits[M].Science Press,2012.

[5]許并社.材料界面的物理和化學[M].北京:化學工業出版社,2006.XUBingshe.Materialphysicsandchemistryoftheinterface[M].Beijing:Chemical Industry Press,2006.

[6]吉列奧.MEMS/MOEMS封裝技術——概念、設計、材料及工藝[M].北京:化學工業出版社,2008.Gilleo,K.MEMS/MOEMS packaging:concepts,designs,materials,and processes[M].Beijing:Chemical Industry Press,2008.

[7]哈珀.電子封裝與互聯手冊[M].賈松良,蔡堅,沈卓身,等譯.北京:電子工業出版社,2009.CharlesA H.Electronic packaging and interconnection handbook[M].Jia Songliang,Cai Jian,Shen Zhuoshen Transl.Beijing:Publishing House of Electronics Industry,2009.

[8]婁文忠,孫運強.微機電系統集成與封裝技術基礎[M].北京:機械工業出版社,2007.LOU Wenzhong,SUN Yunqiang.Micro-electro-mechanical system integration and packaging technology[M].Beijing:China Machine Press,2007.