開關電源SiP技術應用研究

袁柱六,張 崎,袁寶山,曲明山,王 寧,劉云鵬

(1. 中國電子科技集團公司第四十三研究所,安徽 合肥 230088;2. 成都宏明電子科大新材料有限公司,四川成都 610100)

開關電源SiP技術應用研究

袁柱六1,張 崎1,袁寶山1,曲明山2,王 寧1,劉云鵬1

(1. 中國電子科技集團公司第四十三研究所,安徽 合肥 230088;2. 成都宏明電子科大新材料有限公司,四川成都 610100)

通過對開關電源內部標準單元電路構成和內部元器件的特性分析研究,結合SiP技術,采用LTCC/HTCC工藝技術制作多層3D結構,實現開關電源電路中標準單元電路3D結構設計,有效提高了空間利用率,減小了體積。同時對該結構的熱力載荷進行了可靠性分析,最后通過實際產品設計驗證,證明SiP技術在開關電源中應用的可行性。

SiP;LTCC;HTCC;標準單元電路;可靠性;開關電源

微系統技術包含系統級封裝(System in Package-SiP)和系統級芯片(System on Chip-SoC),他們是當今電子系統發展趨向小型化、高性能、多功能、高可靠性和低成本等強力需求驅動下的產物,共同點是最終都以一只集成芯片的形式實現不同功能模塊的集成,不同的是實現方式,SoC是在芯片上實現,而SiP則是在封裝上實現。近年來SoC正面臨極大的技術發展瓶頸,如研發周期、費用和風險等急劇增加,特別是異質元件的集成。由此,兼具尺寸與開發靈活性優勢的 SiP躍然而起,成為后摩爾定律時代的典型代表[1]。

SiP英文全稱是“System in Package”,指在一個封裝體內能夠實現一個系統或子系統功能,能把多個集成電路芯片和無源元器件以及其他支撐元器件綜合于一體。SiP技術是以“異質異構集成、高密度互連、三維封裝”為主要技術手段,主要包括芯片堆疊技術、埋置元器件技術、IPD(Integrated Passive Device)技術、TSV(Through-Silicon-Via)硅通孔技術、POP(Package on Package)技術等。使得它比標準的SMT體積更小、性能更優,而和SoC相比,SiP可降低一次性設計費用,縮短新產品開發和推廣使用的周期,降低成本[2]。美國、歐洲以及日本、韓國、新加坡等國家對SiP技術的研究始于20世紀90年代,美國將其列為重點發展的十大軍民兩用高新技術之一。國內華為、中興等廠商走在 SiP技術發展的前列。由此,SiP技術廣泛應用于RF無線電、傳感器、網絡及計算機技術和高速數字等手機、穿戴設備消費市場等產品領域。

SiP技術在高可靠混合集成開關電源產品領域尚處于研究階段,鮮見相關的報道。為了實現開關電源小型化設計,縮短研發周期和降低成本,作者通過對開關電源單元電路標準化設計以及元器件特性分析研究,提出單元電路標準化、通用化和模塊化設計思路,同時采用 SiP技術對標準單元電路的微型化提出一種三維結構設計方法,旨在提高空間利用率,減小體積,縮短設計周期和降低設計成本,同時對該結構開展了熱力載荷可靠性仿真分析,最后通過實際產品設計驗證,證明 SiP技術在混合集成開關電源產品中應用的可行性。

1 SiP總體架構設計思路

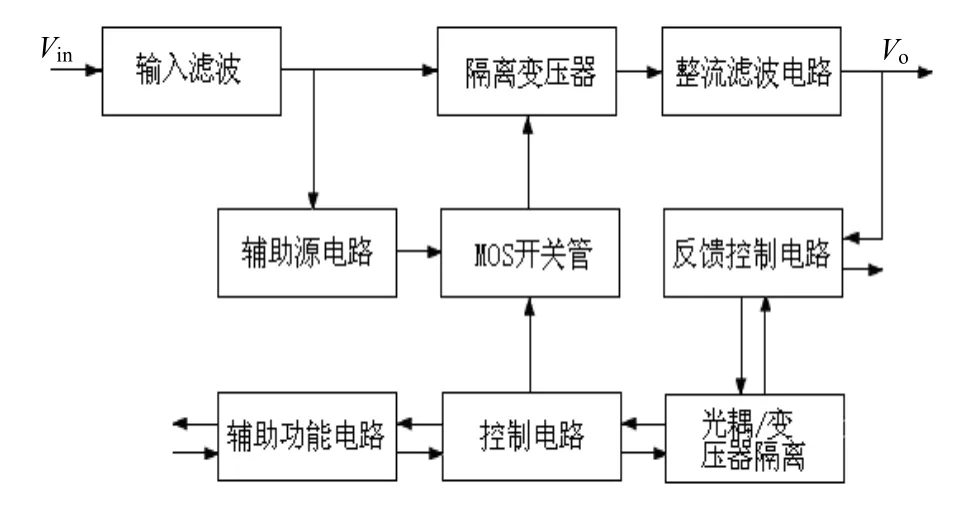

開關電源的基本單元電路組成框圖如圖1所示。

圖1 基本單元電路組成框圖Fig.1 Circuit diagram of basic unit

總體架構設計思路:充分發揮 SiP技術優勢,研究分析開關電源電路內部標準單元電路構成和內部元器件的規格特性,將磁性器件等以“面積”換取“高度”和控制類器件以“高度”換取“面積”的思路。

SiP總體架構設計剖面如圖2所示,通過分析內部標準單元電路構成和內部元器件的規格特性,將開關電源電路標準劃分為標準控制單元電路(如反饋控制電路、控制電路、輔助功能電路以及輔助源電路等)及標準功率單元電路(如功率MOS管、功率變壓器、功率電感、功率整流管等)。因開關電源屬功率電路,在總體架構設計時,充分考慮散熱、功率器件的規格特性和內部立體空間,將標準功率轉換電路直接布局在散熱熱沉上,利用3D多腔體結構將微功耗的標準控制單元電路布局于成膜基板或功率器件上(如MOS管、整流管)。

圖2 SiP總體架構設計剖面示意圖Fig.2 Scheme of SiP overall architecture

標準控制單元電路采用LTCC/HTCC工藝3D多層或多腔體結構、厚膜光刻技術、微組裝技術(包含0402、0201及01005小尺寸阻容器件、芯片間互連、芯片堆疊、多溫度梯度焊接、基板堆疊、BGA焊接)等技術方式,充分利用立體空間來減小體積,提高組裝密度和功率密度,達到“一體化設計架構”或與系統“融合式(嵌入式)設計架構”。結構上以輕、薄為主,最大限度不占用系統的體積和質量,滿足系統的“微、小、輕、薄”需求。

2 單元電路標準化設計

由圖1所示開關電源電路的基本組成,依據SiP總體架構設計思路,將開關電源電路劃分為標準控制單元和功率單元電路。

標準控制單元電路如圖3所示,主要是以脈寬調制器為核心,包含其外圍電路、供電電源、輔助功能單元電路等。

圖3 標準控制單元電路Fig.3 Standard control unit circuit

標準反饋控制單元電路如圖4所示,主要是以運算放大器為核心,包含其外圍阻容器件構成的比例、積分和微分網絡、供電電源、輔助功能單元電路等。

圖4 反饋控制電路Fig.4 Feedback control circuit

兩個標準控制單元電路基本是以集成芯片為核心,外圍一些阻、容器件及部分三極管和二極管構成,通過電路分析和器件特性研究,單元電路功耗小,器件體積小,易于集成,同時具有較強的通用性,可形成開關電源標準單元電路模塊,后期整體設計形同“堆積木”。

3 標準單元三維立體結構設計

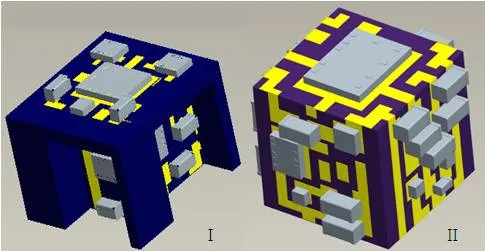

傳統混合集成DC/DC變換器是基于Al2O3成膜基板多芯片組件(Multi-Chip Module, MCM),即在Al2O3成膜基板上組裝元器件,實現電路性能指標,如圖5所示。但在封裝腔體的內部空間的利用率小,難以提高功率密度。由此通過對開關電源內部標準單元電路劃分,由平面向空間轉換(由 2D—MCM向3D—MCM轉換),三維立體結構應用設計如圖6,有效面積將減小達75%以上。

圖5 MCM平面結構Fig.5 MCM plane structure

圖6 SiP 3D多層結構Fig.6 SiP 3D multilayer structure

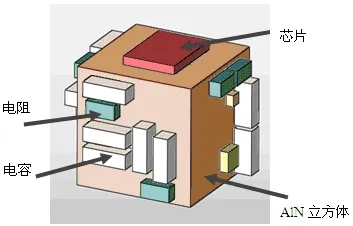

三維立體結構是基于LTCC/HTCC多層基板實現六面體結構,將芯片、電阻以及電容等電子元器件布局于結構件六個面上,通過表面及內部的金屬化連線,實現電子元器件的電氣連接,底部設計BGA(或焊接面),實現與Al2O3成膜基板上功率電子元器件的電氣連接。圖6所示是設計的兩種立體結構,從工藝制作和工藝組裝等方面綜合考慮,優選第二種。在微組裝工藝技術上,應用了多溫度梯度組裝技術、多層次功能基板一次焊接技術、基于熱沉的多器件焊接技術、芯片堆疊技術、芯片與芯片間的互連技術、小尺寸元器件高密度組裝技術(以0402/0201/01005器件為代表)、三維立體結構件BGA互連技術等。

4 熱與力仿真分析

SiP技術在高可靠混合集成開關電源產品應用尚處于研究階段,產品的質量可靠性,需滿足GJB2438A—2002《混合集成電路通用規范》和GJB548B—2005《微電子器件試驗方法和程序》要求,為此對三維立體結構件集成化的設計需要結合力學進行結構分析,結合熱學進行熱平衡設計,提高產品可靠性和環境適應性[3-4]。

運用PRO-E軟件對三維立體結構件進行建模,如圖7所示,圖中材料組成:三維立體結構件材料為氮化鋁(AlN)、陶瓷電容器材料為鈦酸鋇(BaTiO3)、電阻材料為氧化鋁(Al2O3)、厚膜陶瓷基板材料為氧化鋁(Al2O3)、封裝外殼材料為10#鋼、集成芯片材料為硅(Si),借助 Ansys仿真軟件對三維立體結構件進行力、熱結構可靠性有限元分析[5-6]。

圖7 結構模型圖Fig.7 Structure model

GJB548B—2005規定H級混合集成電路的力、熱環境試驗項目和條件要求如下[3-4]:

(1)溫度循環:條件C,–65~+150 ℃,100次,t1=(20±1)min,t2≤1 min;

(2)機械沖擊:14.7 N(1500 g),半正弦波,持續時間1 ms,y1方向5次;

(3)恒定加速度:49 000 m/s2,y1方向1 min。

4.1 溫度循環仿真分析

溫度循環試驗主要是考核三維立體結構件與表貼元器件之間以及三維立體結構件與厚膜 Al2O3基板之間的熱匹配性和器件所承受極端溫度的能力[4]。150 ℃是整體結構影響最大的溫度點,圖8是150 ℃等效應力云圖和形變大小云圖。

圖8 等效應力云圖(左)和形變大小云圖(右)Fig.8 Equivalent stress nephogram(left) and deformation size nephogram(right)

由于BaTiO3熱膨脹系數為(10~12)×10–6/℃,Si熱膨脹系數為 2.5×10–6/℃,與 AlN熱膨脹系數(4.4×10–6/℃)接近,同時電容、電阻選用最大尺寸為 1 mm×0.5 mm(0402),多為 0.6 mm×0.3 mm(0201),集成芯片最大尺寸為2.5 mm×1.8 mm,仿真結果等效應力最大值約為18 MPa,遠小于其斷裂模量。厚膜 Al2O3基板熱膨脹系數為 6.7×10–6/℃,與AlN相差較小,仿真結果等效應力最大值約為9.4 MPa,遠小于其斷裂模量。封裝材料10#鋼熱膨脹系數為(10~12)×10–6/℃,從仿真的結果看,等效應力最大位置為 Al2O3基板與封裝管殼接觸面約為 110 MPa,小于Al2O3陶瓷的抗壓強度1500 MPa、抗拉強度300 MPa,該結構件基體本身強度可靠,不會碎裂。實際工程中采用軟固定連接方式(粘接和焊接工藝),為此,滿足溫度循環試驗考核要求。

4.2 機械沖擊仿真分析

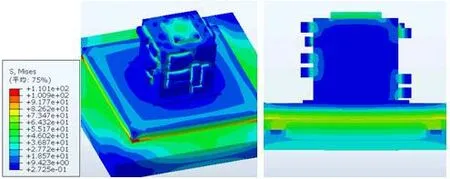

機械沖擊試驗主要是考核三維立體結構件與表貼元器件之間以及三維立體結構件與厚膜 Al2O3基板之間所承受突然受力或運動狀態突然變化而產生沖擊力的能力[4],圖9是14 700 m/s2最大加速度時等效應力云圖和形變大小云圖。

圖9 最大加速度時等效應力云圖(左)和形變大小云圖(右)Fig.9 Equivalent stress nephogram(left) and deformation size nephogram(right)at maximum acceleration

三維立體結構件標貼元器件尺寸小,最大質量僅為2.3 mg,仿真得到最大應力值約為12 MPa,小于元器件的粘/焊接強度(不小于24 MPa)。三維立體結構件尺寸小(為4 mm×4 mm×4 mm),整體質量約0.3 g,仿真得到最大應力值約為69 MPa,集中于三維立體結構件的角點處,遠小于AlN陶瓷的斷裂強度,為此,滿足機械沖擊試驗考核要求。

4.3 恒定加速度

恒定加速度試驗主要是考核沖擊和振動試驗時不一定能檢測出的結構和機械類型的缺陷,此應力試驗是測定三維立體結構件與表貼元器件之間以及三維立體結構件與厚膜 Al2O3基板之間的機械強度極限值[4]。圖10是294 000 m/s2最大加速度時等效應力云圖。

圖10 等效應力分布云圖Fig.10 Equivalent stress distribution nephogram

由于設計的三維立體結構件尺寸小,所設計選用的元器件尺寸小,整體質量小,同時采用軟固定連接方式(粘接和焊接工藝),仿真的最大等效應力約為1.35 MPa,小于元器件的粘/焊接強度,為此,滿足恒定加速度試驗考核要求。

4.4 熱仿真分析

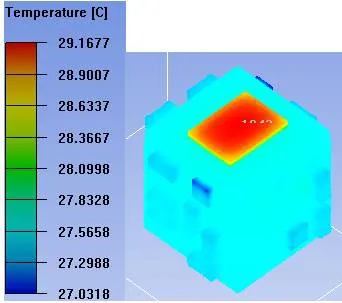

通過對電路元器件的功率損耗計算,運用軟件對元器件進行熱耗分析,結果滿足三維立體結構件材料選擇合理性和元器件在結構件上熱源布局合理性要求。圖11所示為模擬仿真該結構溫度分布情況。

圖11 溫度分布云圖Fig.11 Temperature distribution nephogram

電路分析標準單元電路的各元器件的功耗,通過計算,脈寬調制器功耗最大約為0.2 W,考慮其在整體電路中尺寸最大,制約三維立體結構的整體尺寸,為此布局于結構件的頂部,在結構件的材料選用上,在考慮導熱率同時兼顧工藝實施,選用 AlN材料,其導熱率達140~230 W/(m·℃),仿真在環境溫度25 ℃時,最高溫度約29.16 ℃,溫升為4.16 ℃,在125 ℃環境溫度下,其溫度達130 ℃,滿足熱設計合理性和器件布局合理性要求。

5 應用驗證

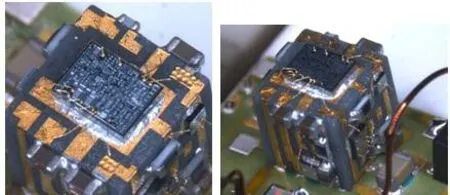

本實例應用是在37 mm×28 mm×8 mm的體積內集成兩路獨立輸出的DC/DC變換器,將開關電源電路中的標準單元電路劃分為標準控制單元電路、標準反饋控制單元電路,采用AlN多層基板,實現六面金屬化互連,尺寸為≤4 mm×4 mm×4 mm,在基板表面進行組裝芯片等元器件,實物如圖12所示。

圖12 產品實物圖Fig.12 Product picture

應用樣品電性能測試如表1所示。

表1 樣機電性能測試結果Tab.1 Electrical measurements of a prototype

通過對原理樣機的電性能測試,對比設計指標,達到研制目標要求。應用樣品環境試驗結果如表2所示。

表2 樣機環境試驗Tab.2 Environmental tests of a prototype

對原理樣機按H級環境實驗條件驗證,達到環境試驗考核要求。

6 結論

采用 SiP技術對混合集成開關電源的微型化提出一種三維結構設計方法,通過融合設計、集成化設計、減小系統中的過渡和連接,從而降低了寄生參數的影響,提高產品的性能指標,通過優化設計合理布局,結合熱力學分析,解決結構的環境應力問題,最后通過實際產品設計驗證,證明了 SiP技術在混合集成開關電源產品中應用的可行性。通過SiP技術將混合集成電路設計由平面向空間轉換,可以提高空間利用率,減小產品體積。通過標準單元電路模塊化設計,可以縮短設計與加工周期,降低成本。

[1] PEDDER D J. System-in-package: a guide for electronics design engineers [R]. London: TWI Ltd, 2009.

[2] 李揚, 劉楊. SiP系統級封裝設計與仿真 [M]. 北京: 電子工業出版社, 2012: 21-24.

[3] 中國人民解放軍總裝備部. GJB2438A—2002: 混合集成電路通用規范 [S]. 北京: 中國標準出版社, 2003.

[4] 中國人民解放軍總裝備部. GJB548B—2005: 微電子器件試驗方法和程序 [S]. 北京: 中國標準出版社, 2005.

[5] 黃志新, 劉成柱. ANSYS Workbench 14.0: 超級學習手冊 [M]. 北京: 人民郵電出版社, 2013.

[6] 鐘日銘. Pro/ENGINEER Wildfire 5.0從入門到精通 [M].北京: 機械工業出版社, 2015.

SiP technology application research in switch power supply

YUAN Zhuliu1, ZHANG Qi1, YUAN Baoshan1, QU mingshan2, WANG Ning1, LIU Yunpeng1

(1. The 43thResearch Institute of CETC, Hefei 230088, China; 2. Chengdu Hongming & UESTC New Materials Co.,Ltd, Chengdu 610100, China)

By means of studying characteristics of the inner standard unit circuit and the components of switch power supplies with SiP technology, multiple three-dimensional structure was made by LTCC or HTCC techniques, fulfilling IP core circuit 3D structure design in switch power supplies with small size and high space efficiency. Meanwhile, the thermal and force loads reliabilities of this 3D structure were analyzed. Then the verification of an actual product design was passed, and the feasibility of SiP technologies in switch power supplies were testified.

SiP; LTCC; HTCC; standard unit circuit; reliability; switch power supply

10.14106/j.cnki.1001-2028.2018.01.013

TN405

A

1001-2028(2018)01-0066-05

2017-12-01

袁柱六

袁柱六(1980-),男,安徽廬江人,高級工程師,主要研究混合集成開關電源與微系統電源。

(編輯:陳渝生)