基于FPGA 的浮點LMS 自適應濾波算法的設計與實現

齊志強*

(中國空空導彈研究院,河南洛陽,471009)

基于FPGA 的浮點LMS 自適應濾波算法的設計與實現

齊志強*

(中國空空導彈研究院,河南洛陽,471009)

針對定點LMS(最小均方誤差)自適應濾波算法動態范圍小,運算精度差的弊端,提出了一種基于FPGA的浮點LMS自適應濾波算法的實現方法。該方法能夠有效降低量化誤差造成的性能損失,避免了采用DSP實現算法造成的硬件開銷,降低了系統設計復雜度,提高了系統可靠性,同時還具有可移植性強,應用靈活等優點。

自適應;抗干擾;浮點;最小均方誤差;FPGA

引言

自適應濾波器是統計信號處理的一個重要組成部分,其性能通常遠優于常規方法設計的固定濾波器,因此被廣泛應用于通信、雷達、控制、聲吶、地震和生物醫學等領域[1-2]。最小均方(LMS)自適應濾波算法因其設計簡單,性能高效,魯棒性強而得以廣泛應用[3-5]。傳統的自適應濾波算法大多基于DSP芯片實現,但存在抗干擾性能差和實時性差的問題[6-7]。隨著 FPGA集成度的不斷提高,LMS自適應濾波算法逐漸采用FPGA實現,通常采用定點數作為運算的數據格式。但定點運算方式在進行整型化時會引入誤差,導致精度下降[8],并且動態范圍較小,難以滿足一些對系統性能要求高或對動態范圍要求大的應用。對系統性能要求高或對動態范圍要求大的應用一般采用FPGA+DSP的硬件架構,系統電路設計復雜,可靠性差。

雖然浮點運算用 FPGA實現占用資源較多,但隨著大規模FPGA的普及,資源問題已不再成為問題的瓶頸[9]。本文提出了一種基于FPGA的浮點LMS自適應濾波算法的設計與實現方法,在硬件上去掉了 DSP芯片及其外圍電路,電路大大簡化,電路面積可減少約40%。由于不再需要FPGA與DSP間通過大量總線進行信息交互,提高了系統的可靠性,在不失靈活性的前提下提升了運算的性能[10],適用于對性能要求較高的應用場合。

1 LMS自適應濾波算法

LMS自適應濾波算法是一種基于梯度的算法,假定有一個構建好的二次性能表面,當性能表面是天線陣權值的二次函數時,性能表面呈橢圓形的拋物面形狀,其中有一個最小值。利用梯度法求最小值,通過求均方誤差可構建代價函數。本文以4通道輸入信號為例,其中一路作為期望信號,其它三路加權后與期望信號做差,使輸出最小即可達到消除干擾的目的[11],如圖所示。

圖1 LMS自適應濾波系統

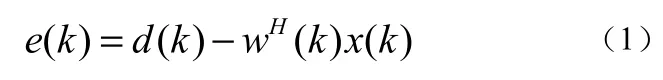

誤差為[12]:

其平方誤差為:

去掉與時間相關的符號,則代價函數為:

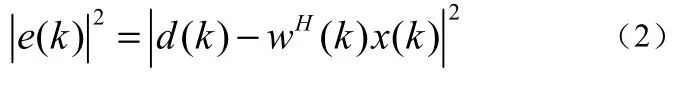

采用梯度法可求式(3)的最小值,(3)式的梯度

當梯度為零時,權值是最優維納解,用下式表示:

式(5)是按照知道所有信號的統計數據并計算出相關矩陣為基礎的,事實上我們不可能知道這些統計數據,而只能用瞬時估計值來代替,瞬時估計值為:

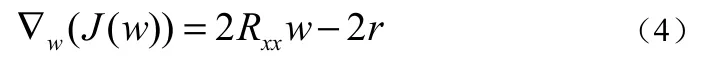

采用最陡下降法的迭代技術可近似求出代價函數的梯度,最陡下降方向為梯度向量的反方向。最陡下降法可用Widrow所提出的最小均方算法的權值來近似,最陡下降迭代近似由下式給出[13]:

其中,是步長,?w是性能表面的梯度。

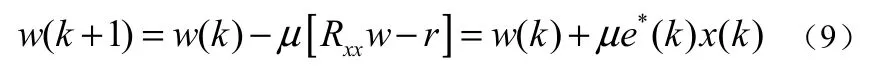

將式(4)代入式(8)中,得[14-15]:

其中e(k)=d(k)? wH(k) x(k)表示誤差信號,在本系統中作為消除干擾后的信號輸出。當迭代次數趨于無窮時,濾波器的權系數逼近維納解。式(9)中LMS算法的收斂性與步長 成正比。如果步長太小,則收斂速度緩慢,甚至出現過阻尼情況;如果步長太大,則收斂不到最優權值,權值在最優權值附近振蕩[16]。研究表明,要想使算法穩定,需滿足[17-18]:

其中λmax為相關矩陣R的最大特征值。由上述分析可知,算法的核心是求出各路權值,權值由式(9)經多次迭代求得,步長因子 由仿真確定。該算法基于浮點運算,故無需仿真確定各級信號位寬。由于LMS算法是一種迭代運算,無法一個時鐘輸出一次權值,所以計算權值時需要對輸入信號進行抽取。為了提高數據有效率,輸出數據并不抽取,只需一段數據對應同一組權值即可,即采用分塊計算的LMS算法。

2 LMS自適應濾波算法的FPGA實現

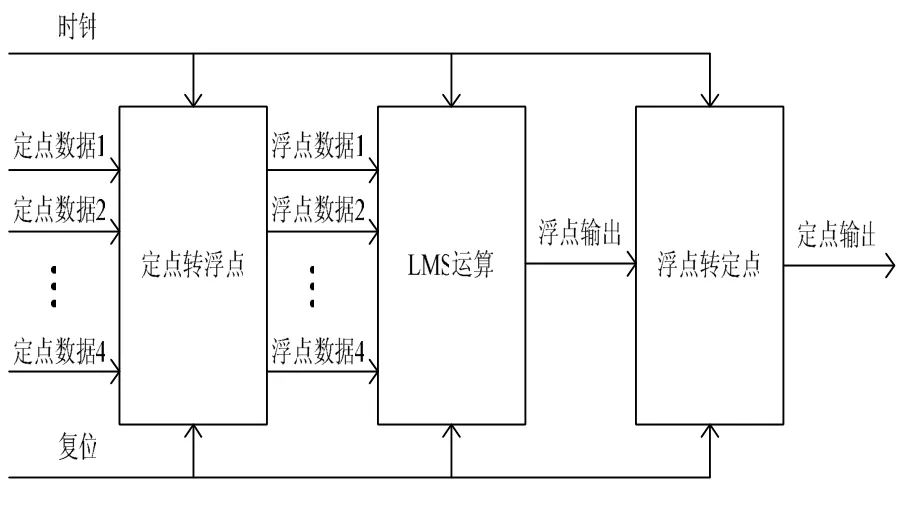

浮點運算包括單精度運算和雙精度運算,考慮到運算需求和資源消耗等因素,我們采用單精度運算,FPGA選用Altera公司的Cyclone V系列5CEFA9實現。浮點LMS自適應濾波算法的FPGA實現大體分三個步驟:第一步是將輸入的定點數據轉換為浮點數;第二步是進行浮點LMS運算;第三步是將輸出的浮點數轉換為定點數。浮點LMS自適應濾波算法頂層模塊視圖如圖2所示:

圖2 浮點LMS自適應濾波算法頂層模塊視圖

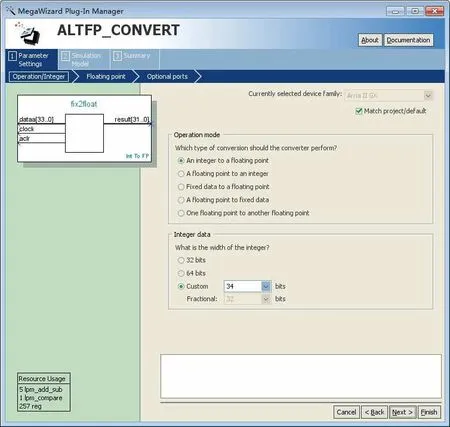

定點數轉浮點數和浮點數轉定點數可以調用Quartus中的免費IP核ALTFP_CONVERT來實現,如圖3所示,通過配置IP核ALTFP_CONVERT中的參數,即可實現定點數轉浮點數和浮點數轉定點數。

圖3 ALTFP_CONVERT IP核

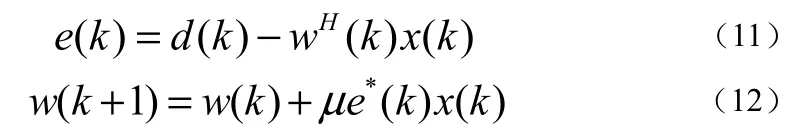

從LMS算法的描述可以看出,實現LMS算法只需要完成式(11)和式(12)兩個算式的計算。

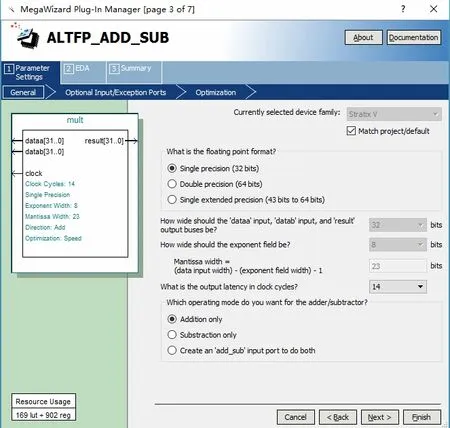

上面兩個算式均為浮點復數運算,只包含加法、減法和乘法三種運算,三種運算均可以調用Quartus中的免費IP核來實現。浮點加法和減法均可以通過調用Quartus中的ALTFP_ADD_SUB IP核來實現,如圖4所示。通過配置不同的選項即可實現浮點加法和浮點減法。

圖4 ALTFP_ADD_SUB IP核

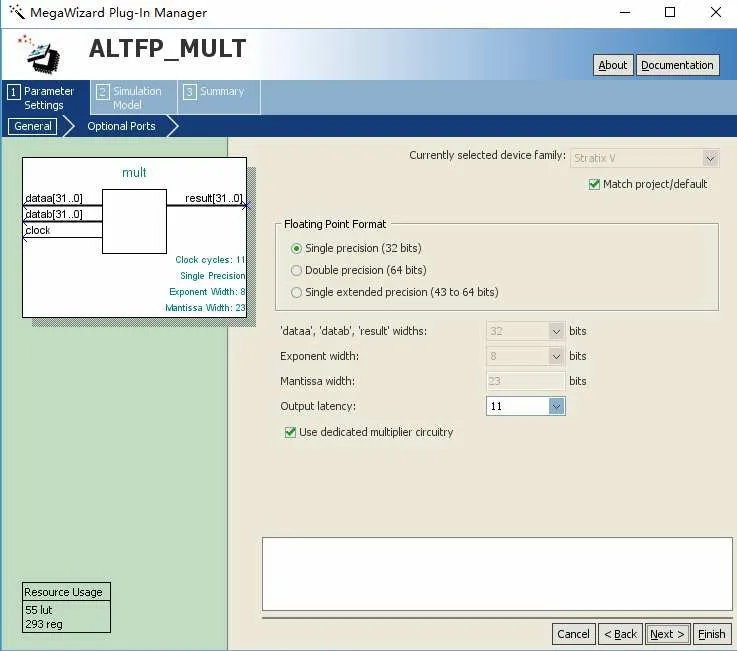

浮點乘法可以通過調用Quartus中的ALTFP_MULT IP核來實現,如圖5所示。

圖5 ALTFP_MULT IP核

Quartus中的浮點加法,減法和乘法IP核均可根據需要選擇單精度或雙精度類型,其輸出延遲幾個時鐘,面積優先還是速度優先等參數均可以根據需要進行配置,根據不同的配置方案,其消耗的資源也各不相同,消耗資源情況可以在配置框圖中看到。

算式(11)為LMS算法的輸出結果,采用流水線處理方式,可實現每個時鐘節拍輸出一個數據;算式(12)為權值更新算式,由于e(k)的輸出無法用1個時鐘周期完成,所以權值的更新需要多個時鐘周期。用 1個控制模塊來產生各運算模塊的控制信號,以實現內部各運算模塊的運算控制,保證各模塊之間數據銜接穩定、正確,以有效地控制模塊的計算,得到準確的計算結果。通過模塊化的IP 核配置,并配以簡單的時序控制,就可以方便的實現算法。

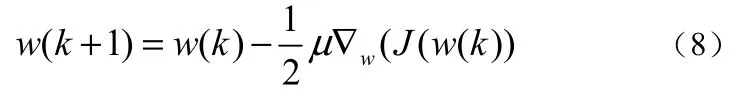

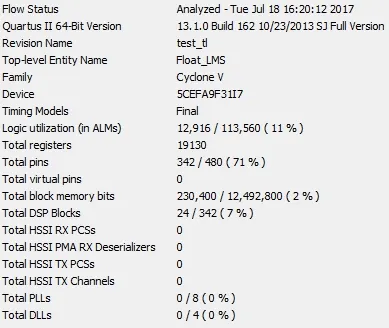

浮點LMS自適應濾波算法的資源消耗情況如圖6所示。

圖6 浮點LMS自適應濾波算法的資源消耗情況

從綜合仿真結果來看,實現4路浮點LMS自適應濾波算法占用FPGA邏輯資源11%,占用乘法器資源7%,占用存儲器資源2%。所選FPGA僅為Altera公司的低端型號,實現4路浮點LMS自適應濾波算法占用資源比例不高,因此該方案具有很強的實用性。

3 結束語

本文所述的基于FPGA的浮點LMS自適應濾波算法,在不降低自適應算法性能,不增加系統功耗和成本的前提下,將原來用DSP實現的浮點運算用FPGA實現,大大減小了電路板面積,簡化了電路設計,降低了系統設計復雜度,提高了系統的可靠性。同時該算法可以封裝成IP核,可以方便的移植到Altera公司的各系列FPGA中,在后續設計中直接調用,不用再重新編寫和調試,縮短了產品開發時間。該方法已在工程上實現,其性能穩定,效果良好,該方法不但可以應用于空域抗干擾算法,也適用于空時抗干擾算法,應用前景廣泛。

[1]齊志強. 全球定位系統的抗干擾技術研究[J]. 電子設計工程,2011,19(19): 112-115.

[2]齊志強. 自適應波束形成技術在 GNSS抗干擾中的應用[J]. 電光與控制,2014,21(10): 110-113.

[3]赫金著. 自適應濾波器原理(第 5版)[M]. 北京. 電子工業出版社,2016,5.

[4]李鵬程,等. 基于 PI算法的自適應調零天線抗干擾技術研究[J]. 電子科學技術,2016,3(4): 471-474.

[5]初明陽. 自適應調零天線衛星定位抗干擾算法仿真研究[J]. 航空兵器,2014,(3): 44-47.

[6]陳亮,等. LMS自適應算法的FPGA設計與實現[J]. 微計算機信息,2012,(7): 22-23+29.

[7]董祥雷,袁上策,王玲. 一種改進LMS算法的高速FPGA實現[J]. 電子信息對抗技術,2015,(3): 72-75.

[8]程龍,等. 基于FPGA的浮點FIR濾波器設計[J]. 電測與儀表,2015,(18): 80-84.

[9]王強. 快速浮點運算在FPGA中的實現[J]. 銅仁學院學報,2014,(4):104-106.

[10]許鵬,等. 基于FPGA的高性能浮點型FFT處理器設計[J]. 武漢大學學報(工學版). 2015,48(1): 120-124.

[11]何永前,李建璜. GPS抗干擾接收機自適應天線陣功率倒置算法研究[J]. 艦船電子工程,2012,32(6): 61-62.

[12]楊帆. 基于 LMS算法的天線波束方向圖仿真研究[J]. 現代導航,2013,(6): 430-433.

[13]聶曉鴻,等. 基于LMS的自適應數字波束形成的FPGA實現[J]. 南京信息工程大學學報,2013,5(3): 267-272.

[14]繆賁術,嚴接班,董蛟. 改進步長 LMS算法及其在衛星信號處理中的應用[J]. 艦船電子工程,2016,36(9): 39-41.

[15]解玲娜,戰勇杰,宋振宇. 基于改進 LMS自適應并行多址干擾消除[J]. 電子設計工程,2012,20(9): 19-22.

[16]田玉坤,等. 功率倒置自適應抗干擾算法的性能分析與仿真[J]. 電子信息對抗技術,2016,31(5): 66-70.

[17]張紅梅,韓萬剛. 一種新的變步長LMS自適應濾波算法研究及應用[J]. 儀器儀表學報,2015,36(8): 1822-1830.

[18]楊文革,等. LMS自適應濾波算法改進及其在連線干涉測量中的應用[J]. 遙測遙控,2016,37(5): 49-57.

Design and Implementation of LMS Adaptive Filtering Algorithm Based on FPGA

QI Zhiqiang*

(China Air to Air Missile Academy,Henan Luoyang,471009,China)

In view of the lower dynamic performance and bad accuracy operation of LMS adaptive filtering algorithm using fix-point,a design scheme of realize a LMS adaptive filtering algorithm using floating-point based on FPGA was introduced. It is successful to reduce the loss of the performance caused by quantization error,meanwhile,the additional hardware cost is avoid if using DSP to realize. This design method has not only reduce the complexity and enhance the reliability of the system,but also has powerful portability and great flexible application.

Adaptive; Anti-jam; Floating-point; LMS(Least-Mean-Square); FPGA

TN973.3

A

1672-9129(2017)06-0075-03

10.19551/j.cnki.issn1672-9129.2017.06.026

齊志強. 基于FPGA的浮點LMS自適應濾波算法的設計與實現[J]. 數碼設計,2017,6(6): 75-77.

Cite:QI Zhiqiang. Design and Implementation of LMS Adaptive Filtering Algorithm Based on FPGA[J]. Peak Data Science,2017,6(6): 75-77.

2017-01-23;

2017-03-07。

齊志強(1982-),男,河南南陽人,碩士,高級工程師。研究方向:研究方向為衛星定位及抗干擾技術。

Email:kdzp001@163.com