一種基于FPGA的多通道復用鑒相器的設計與實現

張秀清,康亞楠,劉 巖,王曉君

(1.河北工業大學電氣工程學院,天津 300130;2.河北科技大學信息科學與工程學院,石家莊 050000)

一種基于FPGA的多通道復用鑒相器的設計與實現

張秀清1,2*,康亞楠2,劉 巖2,王曉君2

(1.河北工業大學電氣工程學院,天津 300130;2.河北科技大學信息科學與工程學院,石家莊 050000)

針對導航接收機中多通道鑒相器資源占用較多與生產成本較高的問題,提出了一種基于FPGA的多通道復用鑒相器方案。該方案通過仲裁單元與FIFO緩存器對多通道相關結果進行仲裁與緩存,首先將多通道并行結果緩存排序為單通道串行結果,隨后將FIFO中的串行結果輸入到鑒相器中,最終使多通道復用同一鑒相器進行計算與處理。整個跟蹤環路中的鑒相器個數由原來的每一通道配置一個變為多個通道復用一個,從而降低了資源占用與生產成本。

多通道鑒相器;資源占用;生產成本;通道復用;仲裁單元;FIFO

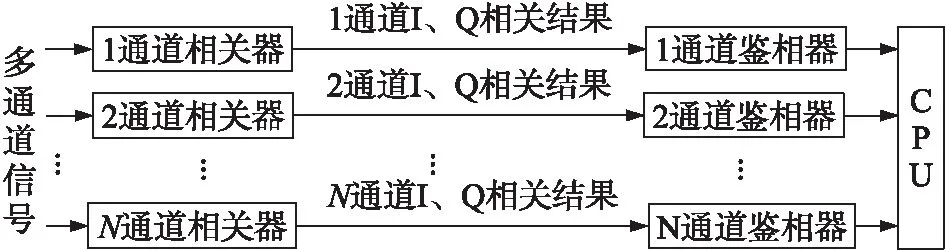

在FPGA設計中,尤其在數字導航接收機多通道信號鑒相處理時,通常都是先設計一個單通道信號的鑒相單元,然后再通過復制鑒相單元來實現并行多通道信號的鑒相處理[1]。這種并行多通道鑒相器結構具體如圖1所示,在這種結構中所有通道的鑒相過程是并行執行的,每一個通道相互獨立工作,互不干擾,產生各自的相關結果,并將相關結果輸入至鑒相器得到鑒相結果,最終將鑒相結果交由CPU來處理[2-3]。并行結構設計相對簡單,調試容易,但當處理通道增加時,每一個通道均會占用一定資源,因此需要的FPGA芯片成本就會相應的增加,這無疑會增加整個開發過程中的成本,當需要的處理通道達到一定數量時,即使等級很高的芯片也無法滿足工程需要,因此多通道復用鑒相器功能就能很好的解決資源占用與成本消耗問題,并且需要的芯片等級也會相應的降低[4-5]。

圖1 并行多通道鑒相器結構

1 多通道復用鑒相器結構設計

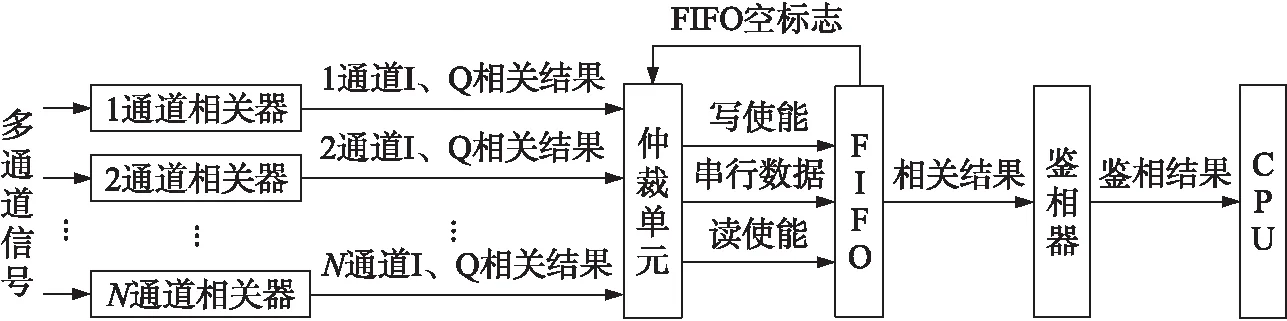

通道I、Q兩支路的相關結果需要輸入至相應通道的鑒相器進行計算,而后得到相應通道的鑒相結果,然而鑒相器并不是實時的對相關結果進行處理,而是每隔1 ms或者更長一段時間進行鑒相處理,因此鑒相器可以通過復用來使整個設計資源占用減少,從而使整個開發過程成本降低[6-8]。多通道復用鑒相器結構如圖2所示。該復用結構主要由仲裁單元、FIFO緩存器與鑒相器3部分組成。仲裁單元主要是對多通道相關結果進行判斷與排序,通過產生讀寫使能來對FIFO輸入數據與輸出數據進行相應控制,從而使鑒相器能夠及時處理每一通道的相關結果。FIFO是將相關結果進行緩存,防止數據丟失,在仲裁單元控制下將多通道的并行相關結果轉換為串行相關結果。鑒相器是將經過仲裁的通道串行相關結果進行鑒相處理,最終CPU利用鑒相結果進行相應的計算與調整。整個復用結構的協調中心在仲裁單元,該單元完成對整個數據鏈的調配與控制,而FIFO與鑒相器是相對獨立的模塊,需要在仲裁單元的控制下進行數據緩存與處理。

圖2 多通道復用鑒相器結構

圖4 仲裁排序模塊內部結構圖

2 仲裁單元設計

在整個復用過程中,相關結果的緩存與鑒相處理必須協調工作,而整體控制由仲裁單元完成,仲裁單元包括仲裁排序模塊與仲裁讀取模塊,主要通過控制FIFO來完成相關結果緩存與串行輸出,控制鑒相器來完成鑒相處理,從而保證整個設計能夠有序穩定的工作。

2.1 仲裁排序模塊

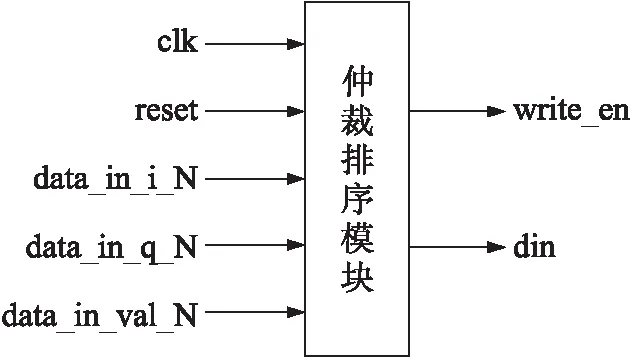

仲裁排序模塊引腳邏輯如圖3所示,該模塊輸入分別為時鐘信號(clk)、復位信號(reset)、N通道i支路相關結果(data_in_i_N)、N通道q支路相關結果(data_in_q_N)與N通道相關結果有效使能(data_in_val_N),該模塊輸出為FIFO寫使能(write_en)與FIFO輸入數據(din)。

圖3 仲裁排序模塊引腳邏輯圖

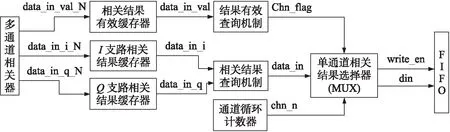

仲裁排序模塊內部結構如圖4所示。多通道相關器將N個通道相關結果有效(data_in_val_N)并行輸入至相關結果有效緩存器,N個i支路相關結果(data_in_i_N)與N個q支路相關結果(data_in_q_N)也并行輸入至I支路相關結果緩存器與Q支路相關結果緩存器;緩存器生成的data_in_val經過結果有效查詢機制得到單通道相關結果選擇器(MUX)的通道有效條件判斷使能(Chn_flag),同時,兩個結果緩存器生成的data_in_i與data_in_q經過相關結果查詢機制得到MUX的數據輸入(data_in),其中data_in由同一通道的i支路相關結果與q支路相關結果拼接而成;通道循環計數器不斷的向MUX實時的輸入通道計數值chn_n;MUX根據chn_n在Chn_flag中的有效位來生成FIFO寫使能(write_en)與FIFO輸入數據(din),其中din由通道號(chn_n)、相應通道的i支路相關結果與q支路相關結果拼接而成,這樣一個通道的數據就緩存至FIFO中,其他通道數據依據同樣邏輯進行緩存,整體實現了并串轉換的過程。

2.2 仲裁讀取模塊

仲裁讀取模塊引腳邏輯如圖5所示,該模塊輸入分別為時鐘信號(clk)、復位信號(reset)、FIFO空信號(empty)與FIFO的輸出數據(dout_temp),該模塊輸出為FIFO讀使能(read_en)、輸出結果有效使能(data_val)、通道號(chnn)、i支路相關結果(data_out_i)與q支路相關結果(data_out_q)。

圖5 仲裁讀取模塊引腳邏輯圖

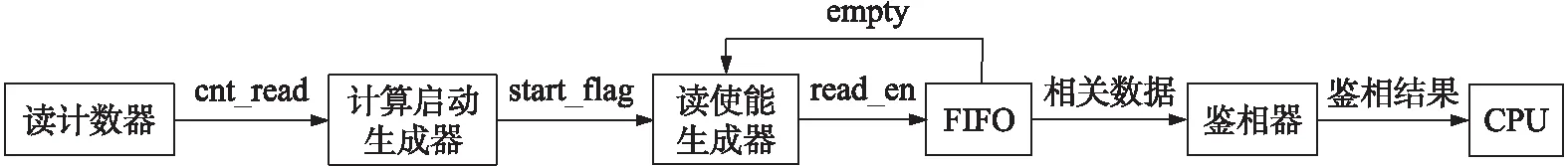

仲裁讀取模塊內部結構如圖6所示。設置鑒相器單元的工作時鐘數,讀計數器生成的計數器值(cnt_read)在計算啟動生成器中與工作時鐘數比較,達到此值時會生成計算啟動標志(start_flag);讀使能生成器會在start_flag的作用下,判斷FIFO反饋回來的空信號(empty)是否有效來生成讀使能(read_en),若empty無效則讀取FIFO緩存的相關結果;相關結果經過鑒相器將鑒相結果輸入至CPU,最終CPU來進行相關的處理與調整。

圖6 仲裁讀取模塊內部結構圖

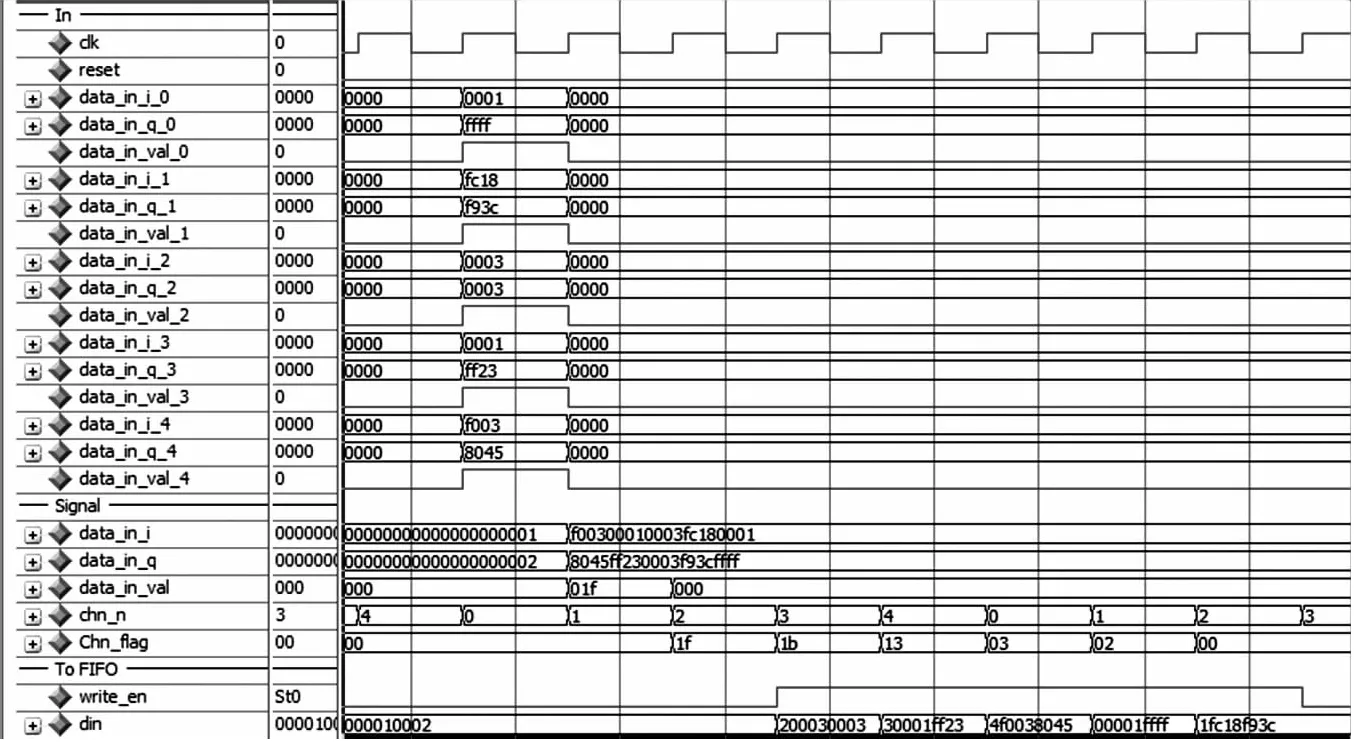

3 行為仿真

利用modelsim軟件對仲裁單元進行行為仿真來驗證其正確性,將仲裁單元行為仿真分為仲裁排序模塊仿真與仲裁讀取模塊仿真。仲裁排序模塊仿真結果如圖7所示,該仿真是對同時到達的5個通道的相關結果進行仲裁排序,輸入信號為5個通道的相關結果與相關結果有效使能;將相關結果輸入至data_in_i與data_in_q,并且有效使能輸入至data_in_val;經過查詢機制與MUX最終得到FIFO寫使能與輸入數據,其中chn_n為MUX提供查詢通道有效使能的變量。

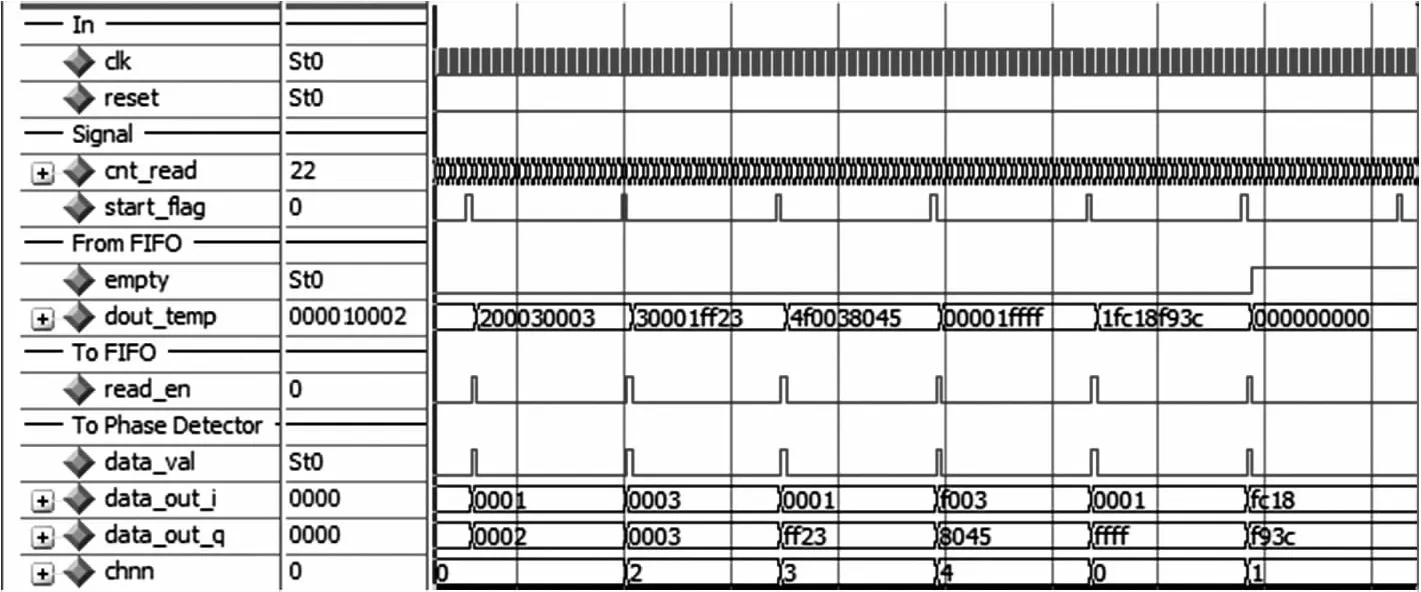

仲裁讀取模塊仿真結果如圖8所示,設置鑒相器工作時鐘數為28,當cnt_read值與鑒相器工作時鐘數相等時,start_flag啟動讀取過程,empty無效時,將FIFO輸出結果(dout_temp)拆分為chnn、data_out_i與data_out_q,同時輸出結果有效使能(data_val)供鑒相器判斷處理。

圖8 仲裁讀取模塊行為仿真

圖7 仲裁排序模塊行為仿真

4 結束語

在FPGA中實現多通道并行結構有著實現簡單,調試容易的特點,但是會增加資源消耗與開發成本。因此本方案從資源消耗與開發成本做綜合考慮分析,利用仲裁單元實現對FIFO緩存器與鑒相器的控制,將并行多通道相關結果變為串行相關結果,共同復用一個鑒相器,資源很大程度上得到了減少。因此本設計具有較高的工程設計參考價值。

[1] 劉純武,黃芝平. 一種多通道信號處理復用結構及其FPGA實現方法[J]. 電子測量與儀器學報,2008,22(1):72-75.

[2] 王黎明,劉貴忠,劉龍,等. 一種基于FGPA的并行流水線FIR濾波器結構[J]. 微電子學,2004,34(5):582-585.

[3] 薛立勤,鄒雪城,陳朝陽. 一種提高微控制器IP可復用性的核內總線設計[J]. 計算機工程與應用,2005,41(2):107-108.

[4] 謝剛. GPS原理與接收機設計[M]. 北京:電子工業出版社,2009:237-241.

[5] Elliott D Kaplan. Understanding GPS:Principles and Applications[EB/OL].

[6] 關紅賓,李晨航. 復用跟蹤通道數字信號處理[J]. 科技視界,2013(9):87-90.

[7] 王東升,李在銘. 基于FPGA的實時視頻運動背景補償校正技術[J]. 電子測量與儀器學報,2006,20(5):69-72.

[8] 熊承義,田金文,柳健,等. 基于線掃格式的JPEG2000小波變換的VLSI結構[J]. 微電子學,2005,35(1):47-50.

DesignandImplementationofaMulti-ChannelMultiplexedPhaseDetectorBasedonFPGA

ZHANGXiuqing1,2*,KANGYanan2,LIUYan2,WANGXiaojun2

(1.School of Eflectrical Engineering,Hebei Universityof Technology,Tianjin 300130,China;2.Hebei University of Science and Technology,Shijiazhuang 050000,China)

For the problem of more resource consumption and production costs of multi-channel phase detector in the navigation receiver,a multi-channel multiplexed phase detector based on FPGA is proposed. The multi-channel related results are arbitrated and cached by the arbitration unit and FIFO buffer. The multi-channel parallel data is transformed into single-channel serial data to send to FIFO,which send the serial data to the phase detector,and the same phase detector is used to calculate and process by multi-channel. The number of phase detector is decreased seriously to only one in the tracking loop,and resource consumption and production costs are saved correspondingly.

multi-channel phase detector;resource consumption;production cost;channel multiplexing;arbitration unit;FIFO

10.3969/j.issn.1005-9490.2017.05.011

2016-08-16修改日期2016-10-23

TN43;TN407

A

1005-9490(2017)05-1104-04

張秀清(1979-),男,博士在讀,河北科技大學信息學院講師,主要從事導航信號處理的研究,894367585@qq.com;

康亞楠(1990-),男,河北科技大學碩士研究生。