ARINC429總線控制器HI—3582接口設(shè)計(jì)

許波強(qiáng)+袁維力+趙亞軍

【摘 要】本文簡(jiǎn)要介紹了ARINC429總線和HI-3582總線控制器的特點(diǎn),結(jié)合工程實(shí)際,給出了基于FPGA的ARINC429總線控制器HI-3582接口設(shè)計(jì)思路和方法。

【關(guān)鍵詞】 ARINC429總線;FPGA;狀態(tài)機(jī)

引言

ARINC429總線是美國(guó)航空無(wú)線電公司制定的民用航空數(shù)字總線傳輸標(biāo)準(zhǔn),它規(guī)定了使用該總線的航空電子設(shè)備的信息流向和基本數(shù)據(jù)字的格式。ARINC429總線為單向傳輸總線,信息只能從通信設(shè)備的發(fā)送口輸出,經(jīng)傳輸總線傳至與它相連的需要該信息的其他設(shè)備的接收口。在需要兩個(gè)通信設(shè)備間雙向傳輸時(shí),則在每個(gè)方向各用一根獨(dú)立的傳輸總線。ARINC429通信采用雙極性歸零制的三態(tài)碼調(diào)制方式,具有接口方便、數(shù)據(jù)傳輸可靠的特點(diǎn),目前已廣泛應(yīng)用于導(dǎo)航定位系統(tǒng)、通信系統(tǒng)等機(jī)載電子設(shè)備中。本文結(jié)合工程實(shí)際,介紹了HOLT公司推出的ARINC429總線控制器芯片HI-3582的特點(diǎn),并給出了基于FPGA的接口設(shè)計(jì)思路和方法。

1 .HI-3582總線控制器簡(jiǎn)介

HOLT INTEGRATED CIRCUITS公司生產(chǎn)的HI-3582是一款性能價(jià)格比較高的ARINC429協(xié)議芯片。該器件的主要特點(diǎn)有:

符合ARINC429總線協(xié)議;

3.3V邏輯電平工作,可直接與LVTTL電平接口;

具有獨(dú)立的雙向接收器和發(fā)送器接口;

無(wú)需驅(qū)動(dòng),可直接連接ARINC429總線;

可編程識(shí)別標(biāo)牌,每個(gè)接收器具有16個(gè)標(biāo)牌存儲(chǔ)單元;

對(duì)接收的數(shù)據(jù)可進(jìn)行奇偶狀態(tài)校驗(yàn);并可對(duì)發(fā)送數(shù)據(jù)奇偶狀態(tài)進(jìn)行設(shè)置;

2 .FPGA與HI-3582的接口設(shè)計(jì)

2.1 接口原理介紹

目前實(shí)現(xiàn)與HI-3582的接口通用的方案是采用單片機(jī)或DSP直接控制接收和發(fā)送數(shù)據(jù)。該方案的缺點(diǎn)是:由于HI-3582的離散控制信號(hào)較多,需要占用大量通用I/O端口,這在系統(tǒng)通用IO資源緊張的情況下,實(shí)現(xiàn)較為復(fù)雜;并且當(dāng)數(shù)據(jù)量較大、發(fā)送及雙接收通道同時(shí)工作時(shí)占用系統(tǒng)處理時(shí)間較長(zhǎng),影響系統(tǒng)工作效率,且容易造成數(shù)據(jù)丟失。為此本文提出了采用FPGA與HI-3582進(jìn)行接口設(shè)計(jì),利用FPGA豐富的I/O接口,將HI-3582芯片上所有和FPGA有關(guān)的接口管腳都以IO的形式直接連接,在FPGA內(nèi)建立狀態(tài)控制機(jī)制,實(shí)現(xiàn)對(duì)HI-3582芯片的數(shù)據(jù)收發(fā)控制處理。該設(shè)計(jì)能極大減少對(duì)單片機(jī)或DSP的I/O資源占用,提高了單片機(jī)/DSP的工作效率;同時(shí)提高了對(duì)HI-3582芯片中斷請(qǐng)求的響應(yīng)速度。

2.2 軟件設(shè)計(jì)及實(shí)現(xiàn)

2.2.1 軟件整體設(shè)計(jì)。

本設(shè)計(jì)中ARINC429總線傳輸速率采用12.5k低速率,數(shù)據(jù)的更新由DSP通過(guò)地址線、數(shù)據(jù)線完成。

設(shè)計(jì)采用在FPGA內(nèi)部建立一個(gè)發(fā)送FIFO緩存和一個(gè)接收FIFO緩存,分別用來(lái)存儲(chǔ)DSP傳來(lái)的待發(fā)送數(shù)據(jù)和兩路ARINC429總線接收到的數(shù)據(jù)。在發(fā)送FIFO不為空時(shí)啟動(dòng)數(shù)據(jù)的發(fā)送,產(chǎn)生HI-3582的發(fā)送時(shí)序。接收數(shù)據(jù)時(shí),F(xiàn)PGA依次根據(jù)HI-3582的接收狀態(tài)標(biāo)志D/R1、D/R2判斷并讀取數(shù)據(jù),當(dāng)D/R1或D/R2為低電平時(shí)啟動(dòng)數(shù)據(jù)接收,產(chǎn)生HI-3582的接收時(shí)序讀取HI-3582相應(yīng)接收緩沖器中的數(shù)據(jù),再將讀取到的數(shù)寫入接收FIFO。當(dāng)FIFO緩沖器中的存儲(chǔ)數(shù)據(jù)量達(dá)到編程設(shè)置的觸發(fā)深度時(shí),產(chǎn)生DSP中斷信號(hào)通知DSP讀取數(shù)據(jù)。

2.2.2 數(shù)據(jù)讀寫狀態(tài)機(jī)的設(shè)計(jì)。

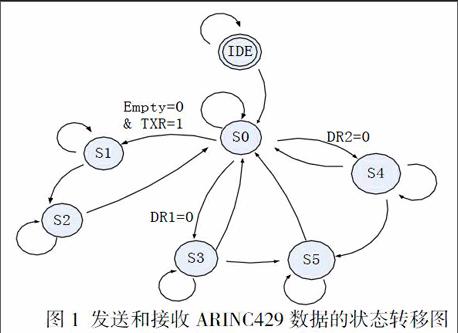

由于對(duì)HI-3582的讀寫操作具有嚴(yán)格的邏輯順序和時(shí)序關(guān)系,非常適合采用狀態(tài)機(jī)來(lái)描述;所以本設(shè)計(jì)采用有限狀態(tài)機(jī)來(lái)實(shí)現(xiàn)讀寫HI-3582數(shù)據(jù)。圖2為讀寫HI-3582數(shù)據(jù)的狀態(tài)轉(zhuǎn)移圖。

IDE:初始化控制寄存器。當(dāng)系統(tǒng)上電或復(fù)位時(shí)首先進(jìn)入寫控制寄存器狀態(tài),通過(guò)產(chǎn)生CWSTR控制時(shí)序?qū)I-3582控制寄存器進(jìn)行初始化;

S0:收發(fā)控制。檢測(cè)HI-3582發(fā)送空閑標(biāo)志TXR及發(fā)送FIFO數(shù)據(jù)標(biāo)志empty,如果TXR為高電平說(shuō)明HI-3582發(fā)送處于空閑狀態(tài),發(fā)送FIFO標(biāo)志empty為低電平,說(shuō)明有數(shù)據(jù)要發(fā)送,進(jìn)入讀數(shù)據(jù)操作狀態(tài),否則檢測(cè)HI-3582接收狀態(tài)標(biāo)志D/R1、D/R2,如果D/R1為低電平,進(jìn)入讀取接收通道1數(shù)據(jù)狀態(tài),如果D/R2為低電平,進(jìn)入讀取接收通道2數(shù)據(jù)狀態(tài);

S1:讀取發(fā)送數(shù)據(jù)。產(chǎn)生一個(gè)FIFO讀信號(hào),讀取一個(gè)待發(fā)送的429數(shù)據(jù)字,進(jìn)入發(fā)送數(shù)據(jù)時(shí)序;

S2:發(fā)送控制。依次控制PL1、PL2、ENTX產(chǎn)生HI-3582所需的發(fā)送控制時(shí)序,將數(shù)據(jù)發(fā)送出去。發(fā)送結(jié)束后返回收發(fā)控制狀態(tài);

S3:接收控制1。依次控制SEL、EN1產(chǎn)生HI-3582所需的接收控制時(shí)序,讀取接收通道1一個(gè)接收數(shù)據(jù)字,進(jìn)入緩存接收數(shù)據(jù)狀態(tài);

S4:接收控制2。依次控制SEL、EN2產(chǎn)生HI-3582所需的接收控制時(shí)序,讀取接收通道2一個(gè)接收數(shù)據(jù)字,進(jìn)入緩存接收數(shù)據(jù)狀態(tài);

S5:緩存接收數(shù)據(jù)。產(chǎn)生一個(gè)FIFO寫信號(hào),將讀取的429數(shù)據(jù)字寫入接收FIFO,并檢測(cè)FIFO中存儲(chǔ)數(shù)據(jù)量是否達(dá)到編程設(shè)置的觸發(fā)深度,當(dāng)滿足編程設(shè)置的觸發(fā)深度時(shí),產(chǎn)生中斷信號(hào),通知DSP讀取數(shù)據(jù)。結(jié)束后返回收發(fā)控制狀態(tài)。

2.2.3 收發(fā)控制時(shí)序設(shè)計(jì)。

對(duì)HI-3582進(jìn)行讀操作時(shí),由于本設(shè)計(jì)中ARINC429總線采用12.5k低速率,在FPGA中用1MHz時(shí)鐘同步一個(gè)計(jì)數(shù)器,在第一個(gè)時(shí)鐘上升沿置SEL為低,HI-3582數(shù)據(jù)線為高阻;在第二個(gè)時(shí)鐘上升沿置EN1為低,并將HI-3582數(shù)據(jù)線上的值賦給32位臨時(shí)寄存器低16位;在第三個(gè)時(shí)鐘上升沿置SEL、EN1為高,HI-3582數(shù)據(jù)線為高阻;在第四個(gè)時(shí)鐘上升沿置EN1為低,并將HI-3582數(shù)據(jù)線上的值賦給32位臨時(shí)寄存器高16位;在第五個(gè)時(shí)鐘的上升沿置EN1為高;到第六個(gè)時(shí)鐘的上升沿FIFO的寫信號(hào)置低,產(chǎn)生一個(gè)FIFO寫脈沖將臨時(shí)寄存器值寫入FIFO。這樣讀取一個(gè)ARINC429數(shù)據(jù)字的有效時(shí)間為6個(gè)時(shí)鐘周期(6us),完全滿足其讀時(shí)序的要求。

同樣,對(duì)HI-3582進(jìn)行寫操作時(shí),按照上述方法產(chǎn)生PL1,PL2、ENTX時(shí)序啟動(dòng)發(fā)送操作,并檢測(cè)TXR為高時(shí)繼續(xù)發(fā)送下一個(gè)ARINC429數(shù)據(jù)字。

3. 結(jié)論

按照本文介紹的方法, 在Xilinx公司Virtex?-4 系列FPGA芯片XC4VLX40-FFG668的基礎(chǔ)上已成功實(shí)現(xiàn)與HI-3582的ARINC429航空總線接口設(shè)計(jì),并已應(yīng)用到實(shí)際設(shè)備中,滿足系統(tǒng)要求。

參考文獻(xiàn):

[1] SZ-01數(shù)字信息傳輸系統(tǒng),HB6096-86,中華人民共和國(guó)航空工業(yè)部標(biāo)準(zhǔn).

[2]HI-3582, ARINC 429 System on a Chip, HOLT INTEGRATED CIRCUITS.

[3] Virtex-4 User Guide, UG070 (v2.3) August 10, 2007.

[4] VHDL:Programming by Example,Douglas L.Perry,F(xiàn)ourth Edition.endprint