ETC系統中HDLC協議解碼控制器的Verilog HDL實現

鄧昌晟,劉 昱,李海洋,王小松,張海英

(1. 中國科學院微電子研究所 新一代通信射頻芯片技術北京市重點實驗室,北京 100029;2. 中國科學院大學 微電子學院,北京 100049)

ETC系統中HDLC協議解碼控制器的VerilogHDL實現

鄧昌晟1,2,劉 昱1,2,李海洋1,王小松1,張海英1,2

(1. 中國科學院微電子研究所 新一代通信射頻芯片技術北京市重點實驗室,北京 100029;2. 中國科學院大學 微電子學院,北京 100049)

電子不停車收費系統(Electronic Toll Collection, ETC)是解決目前交通擁堵問題最有效的手段。為規范ETC設計,統一國內ETC標準,我國制定了電子收費專用短程通信國家標準(Dedicated Short Range Communications, DSRC)。DSRC數據鏈路層采用由國際標準化組織(ISO)制定的高級數據鏈路控制規程(High-Level Data Link Control, HDLC)。文章遵循DSRC短程通信協議數據鏈路層標準規范,采用硬件描述語言Verilog HDL實現了一種基于串行結構的HDLC解碼電路,并對其中‘0’比特刪除模塊、CRC校驗模塊著重分析,設計較短時延的解碼電路。在解碼時鐘為256 kHz時,可以在0.2 ms時間內完成解碼和讀取工作。

電子不停車收費系統;DSRC;HDLC;Verilog HDL; CRC

0 引言

不停車收費系統(ETC)由路邊讀寫設備(Road Side Unit, RSU)、車載單元(On Board Unit, OBU)、專用短程通信技術(DSRC)組成,如圖1所示。

圖1 ETC系統組成

DSRC通信協議遵循開放系統互聯(Open System Interconnection, OSI)模型,將DSRC協議分為三層模型,即應用層、數據鏈路層、物理層。

數據鏈路層需要提供向下物理層的接口,同時也要向上為應用層提供服務,為此,數據鏈路層需要穩定的數據傳輸協議。DSRC中數據鏈路層采用高級數據鏈路控制協議HDLC。HDLC是一種面向比特的高級鏈路層控制協議。在通信領域中 , HDLC協議是應用最廣泛的協議之一,具有強大的差錯檢測、流量控制、高效和同步傳輸的功能[1]。

使用硬件編程語言實現HDLC協議是比較理想的方式,相對于軟件方式實現,有著更快的執行速度,更好的時序同步性;而相對于使用專用芯片有著更好的靈活性[2]。

1 HDLC協議

1.1HDLC協議幀結構

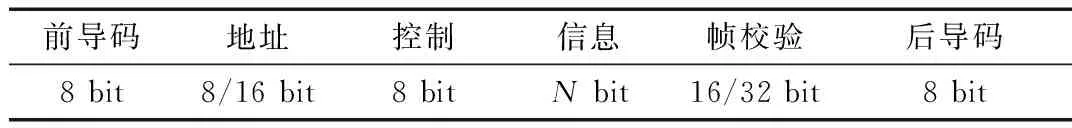

HDLC是面向比特字節數據的傳輸協議,與其他數據鏈路層傳輸協議相比,HDLC協議不依賴字符集,且較利于用硬件電路實現。HDLC協議以幀格式進行數據傳輸,數據幀格式如表1所示[3]。

表1 HDLC協議幀結構

HDLC幀格式由如下幾位組成:

前后導碼:其格式均為二進制序列01111110(0x7E),前后導碼之間為信息位。如果解碼控制器收到多個連續的0x7E,則以最后一個作為幀的前導碼,表示數據起始。解碼控制器在接收的比特數據中找到前后導碼,就可以確定兩個導碼段中間為一幀完整的數據。

地址位:用于表示網絡中發送或接收該幀的設備地址。并且用全‘1’即0xFF或者0xFFFF表示廣播地址。

控制位:幀格式根據控制位的不同,將HDLC幀定義為不同類型的幀。

信息位:所需要傳輸的數據。字段長度取8 bit的整數倍。

幀校驗位:為保證數據的正確性傳輸,HDLC幀校驗位采用國際通行的CRC校驗,根據所選的生成多項式,通常是16 bit或者32 bit的校驗碼。CRC校驗不會對幀數據內容進行修改,但是可以通過校驗是否正確來選擇性接收這一幀數據[4]。

1.2‘0’比特插入機制

在前后導碼之間的比特流數據中,如果出現了與前后導碼一樣的0x7E的比特數據,那么就會被認為是幀的邊界,進而使接收的數據出錯。HDLC協議使用‘0’比特插入機制來避免出現誤檢測邊界的情況。當比特流數據中出現連續的5個‘1’時,在這5個‘1’的數據之后人為地插入一個無效位‘0’。這個位只在傳輸時存在,在設計HDLC解碼控制器時需要考慮這個數據‘0’的存在,解碼時要刪除這個‘0’位數據,還原真實的數據流[5]。

1.3CRC校驗

HDLC協議在每一幀數據后都加入了幀校驗序列,以保證數據的正確性傳輸。HDLC采用循環冗余校驗碼(Cyclic Redundancy Check, CRC)。本設計中采用CRC-CCITT的生成多項式,即:

P(x)=x16+x15+x5+1

在HDLC協議中,除了前后導碼和插入的‘0’比特無效位,所有的信息都要參與CRC校驗[6]。

2 HDLC協議解碼控制器設計

如圖2所示,HDLC協議解碼控制器采用串行結構。

圖2 HDLC協議解碼器框圖

HDLC解碼模塊在接收了來自物理層的FM0解碼數據后,經過刪除前后導碼、刪‘0’、串并轉換、CRC校驗、FIFO各個模塊后完成解碼,將解碼的數據存儲在FIFO中,方便外部MCU讀取。

2.1刪除前后導碼模塊

通過找到連續的01111110的標志字段來判斷數據的開始與結束,接收機只有在前導碼和后導碼中處理有效的數據。并且接收機會將01111110的前后導碼和不是前后導碼中的有效數據都刪除,以防止在后面的刪0模塊中誤檢測到連續的5個“1”后將后導碼刪除[7]。

如圖3所示,刪除前后導碼模塊通過一個標志位flag來標志數據是否有效,初始狀態標志位為0,當檢測到輸出了01111110(0x7E)時,將標志位翻轉為1;再次檢測到01111110(0x7E)時將標志位翻轉為0,在標志位為1時其中的數據就是后續電路需要的有效數據,并用data_start表示有效數據段。data_start位寄存器和數據位一起傳入后面待處理的模塊,用于標志數據流中的有效數據[8]。

圖3 刪除前后導碼流程圖

2.2‘0’比特刪除模塊實現

HDLC數據中除了前后導碼中會出現連續的6個1,在HDLC編碼中一幀數據的有效數據中如果出現連續的5個1,則不管后面的數據是0還是1都在連續的5個1之后插入一個0以區別前后導碼。所以在接收機中要通過判斷有效數據中是否出現連續的5個1并且刪除掉連續5個1以后的一個0[9]。

刪除串行數據中的0會導致串行數據提前:當前的數據是0并且將其刪除了,但是下一位的數據并沒有來到。為了解決這個問題,可以設計一個足夠長的FIFO來緩存接收到的串行數據,在檢測到刪0條件滿足時就停止一位FIFO的輸入,但是由于信息域長度不可知,有效數據中有多少個需要刪除的0并不知道,FIFO的大小難以確定,太小的FIFO會造成數據的丟失和出錯,太大的FIFO會造成過大的時鐘延遲,所以用FIFO緩存不是一個理想的方案。

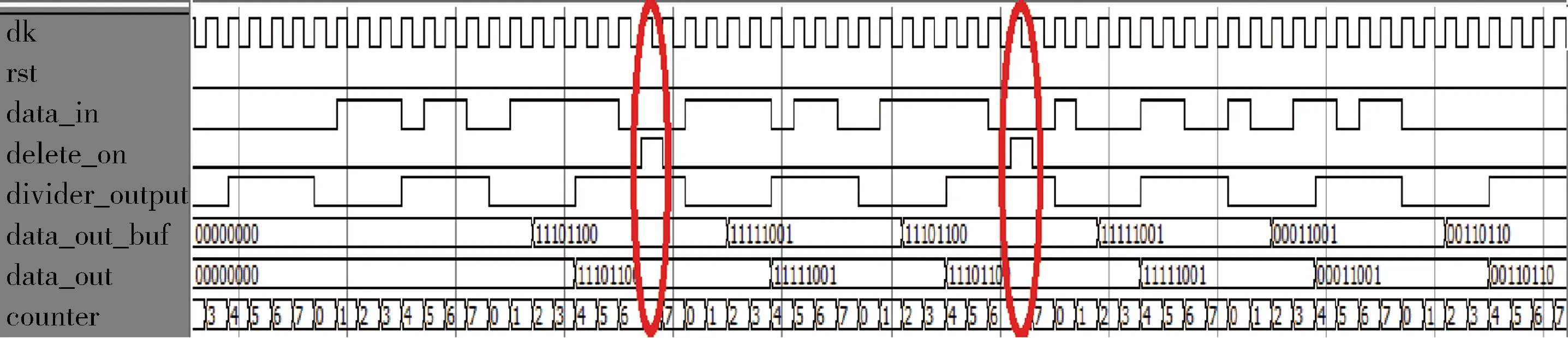

1 bit的串行數據需要通過串并轉換模塊轉換為8 bit的并行數據,以方便后續CRC校驗和FIFO緩存電路使用。串并轉換的模塊通過連續的8個D觸發器實現,時鐘上是通過計數器進行8分頻實現。如圖4所示,結合串并轉換模塊,可以在串并轉換的同時利用D觸發器的可以緩存數據的特性進行刪0模塊中數據的“提前”。用并行數據的低5位與0x1F做比較,如果相同就產生一個脈沖信號給用于時鐘分頻的計數器,這個脈沖信號可以給串并轉換模塊的計數器一個暫停的信號,使得計數器停止一個時鐘周期的計數,并且用于輸出的D觸發器不儲存當前的輸入值,即要被刪除的0數據。這樣就可以達到刪0的目的。

圖4 刪‘0’模塊框圖

假設一幀數據中有效的數據一共有nbit,無效的‘0’位數據有mbit,一個時鐘周期時間為t,電路本身造成的其他延遲為T。則采用FIFO緩存實現‘0’比特刪除模塊時產生的時間延遲為:

而采用與串并轉換結合的方式實現‘0’比特刪除模塊時產生的時間延遲為:

T2=T+m×t

當且僅當n=5×m時,T1=T2,即比特率數據的有效位全為1時,兩者的延遲相等。然而實際情況中一幀數據幾

乎不可能出現全1的情況,即在絕大部分的情況下T1>T2。

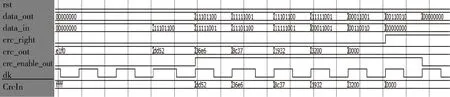

2.3CRC模塊實現

串行CRC校驗實現較為簡單,但是處理速度相對較慢,所以本設計中采用并行CRC校驗,能夠在一個時鐘周期內完成數據CRC校驗。并行CRC校驗原理與串行CRC相同,由于CRC各個位之間可以獨立運算,并行的CRC輸入可以在一個時鐘周期中完成1 B的CRC校驗,這樣的效果與串行CRC校驗的結果是相同的,但是相比串行CRC實現延遲能夠減少8倍。對于生成多項式為gx=x16+x12+x5+1,其移位寄存器如圖5所示。

3 仿真結果與分析

本文采用modelsim SE 10.0a 進行電路仿真,編寫testbench文件進行仿真,模擬輸入已編碼的字符串0x ECF9ECF91932,其中0x32為CRC校驗碼。

3.1刪除前后導碼模塊仿真結果

如圖6所示,data_in是數據輸入端,data_out是數據輸出端,data_start表示數據的有效位。在除去前后導碼后,data_out相比data_in延遲8個串行時鐘周期。則刪除前后導碼模塊的延遲為:

T1=16t

3.2‘0’比特刪除模塊

如圖7所示,data_in是串行數據輸入端,data_out是并行數據輸出端,counter是串并轉換用于時鐘分頻的計數器,如圖中圈出delete_on是發生‘0’刪時候的標志。當發生‘0’刪事件的時鐘,counter會停止計數,略過這一位,同時并行時鐘輸出端也會相應地延遲。總的延遲周期為:T2=11t。

圖5 CRC移位寄存器示意圖

圖6 刪除導碼電路仿真結果

圖7 ‘0’比特刪除模塊仿真結果

3.3CRC校驗模塊

如圖8所示,data_in是數據輸入端,data_out是數據輸出端,通過CRC校驗模塊以后data_out與data_in相比減少了后8位的校驗碼,并且crc_right被置高,表示CRC校驗正確,會被寫入后續的FIFO中。CRC模塊占用一個并行周期:T3=8t。

圖8 CRC校驗仿真結果

3.4仿真結果分析

通過解碼電路,能夠在FIFO輸入端 rd_data 讀取到解碼后正確的并行數據0x ECF9ECF919。在使用256 kHz時鐘時,一個時鐘周期約為t=3.9 μs,因為FIFO的讀取還占用了2個并行時鐘周期,所以解碼一共用時T=51 t個時鐘周期,整個解碼所占用時鐘約為51×3.9 μs=199 μs。

4 結論

本文介紹了HDLC協議的原理,重點分析了HDLC中刪‘0’模塊,CRC校驗模塊的原理和設計實現。并且使用modelsim 仿真設計模塊,驗證了電路功能正確。并且能夠在0.2 ms的時間內完成解碼工作。

[1] 應三叢, 張行. 基于FPGA的HDLC協議控制器[J]. 四川大學學報(工程科學版), 2008, 40(3):116-120.

[2] 李曉娟, 黃翌. 基于FPGA的HDLC設計實現[J]. 現代電子技術, 2007, 30(6):35-37.

[3] LI G, TAN N. Design and implementation of HDLC protocol and manchester encoding based on FPGA in train communication network[C]. Third International Conference on Information and Computing. IEEE Computer Society, 2010:105-108.

[4] NAGPURWALA A H, SUNDARESAN C, CHAITANYA C. Implementation of HDLC controller design using verilog HDL[C]. International Conference on Electrical, Electronics and System Engineering. IEEE, 2013: 7-10.

[5] 邱婷. 電子不停車收費系統基帶電路的設計與實現[D]. 南京:南京理工大學, 2009.

[6] GB/T 20851.1-2007[S]. 電子收費 專用短程通信 第1部分:物理層.2007.

[7] GB/T 20851.2-2007[S]. 電子收費 專用短程通信 第2部分:數據鏈路層.2007.

[8] 賈輝. HDLC幀收發器在TDM/以太網接口電路中的應用[D]. 成都:西南交通大學, 2013.

[9] 劉杰宇. 基于FPGA技術的HDLC 幀收發器的設計與實現[D]. 北京:北京交通大學, 2010.

Verilog HDL implementation of HDLC protocol decoding controller in ETC system

Deng Changsheng1,2, Liu Yu1,2, Li Haiyang1, Wang Xiaosong1, Zhang Haiying1,2

(1. Beijing Key Laboratory of Radio Frequency IC Technology for Next Generation Communications,Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China;2. School of Microelectronics, University of Chinese Academy of Sciences, Beijing 100049, China)

Electronic toll collection system is the most effective way to solve the current traffic problem. In order to uniform the standard of ETC, China has developed the national standard for Dedicated Short Range Communications (DSRC). The DSRC data link layer uses a High-Level Data Link Control protocol developed by the International Organization(ISO). This paper follows the standard specification of dedicated short range communication protocol data link layer, and implements a HDLC decoding circuit based on serial pipeline structure using hardware description language Verilog HDL, and focuses on the 0-bit delete module and CRC module for designing a shorter delay circuit. When the decoding clock is 256 kHz, decoding and reading can be completed within 0.2 ms.

ETC; DSRC; HDLC; Verilog HDL; CRC

TN92

A

10.19358/j.issn.1674- 7720.2017.19.009

鄧昌晟,劉昱,李海洋,等.ETC系統中HDLC協議解碼控制器的verilog HDL實現[J].微型機與應用,2017,36(19):30-33.

2017-03-28)

鄧昌晟(1993-),男,碩士研究生,主要研究方向:數字電路設計。劉昱(1975-),男,博士,研究員,主要研究方向:射頻集成電路。