1553B容錯解碼器對抗干擾的可信賴性改進

楊福宇

(重慶工業自動化儀表研究所,重慶 401123)

1553B容錯解碼器對抗干擾的可信賴性改進

楊福宇

(重慶工業自動化儀表研究所,重慶 401123)

通過1553B通信協議各種解碼器設計方案討論了引起協議可信賴性不足的硬件的三個原因:沒有對干擾的容錯設計,拖尾電壓超過輸入下限以及缺少過0位置的修正能力。所以解碼器容錯能力的提高是改善1553B通信協議可信賴性的關鍵。文中介紹了容錯解碼器中對抗干擾的部分:將每8 slot組成兩個半位HB1和HB2。采用這種方法,在半位中連續干擾寬度為3 slot的可以排除掉,寬度小的干擾累加小于3 時也可濾除掉。對于增頻的1553B芯片(例如2 Mbps以上),這是更加重要的可信賴性改進。

1553B;容錯;解碼器

引 言

1553B是一種通信協議,它規定以Manchester2編碼對位(bit)進行編碼,以字(word)為基本單位進行傳送。關于1553B的內容可參照標準,對應的國標為GJB289A-97數字式時分制指令/響應型多路傳輸數據總線。

由于工業現場有傳導和輻射干擾,1553B標準對硬件抗擾能力的考慮較少,查錯能力不足,所以會引起應用的可依賴性不夠,詳見“1553B通信協議的可依賴性討論”[1]。但是這種協議已廣泛使用,業界還沒有準備好新的替代協議,所以如何在已有的條件下改進其可信賴性便是重中之重。

國外對譯碼器的設計是保密的。初步看來,1553B總線譯碼器的設計有三個主要薄弱環節:①缺少對外部進入的干擾的對抗能力;②由于變壓器漏磁等原因造成的字尾容許拖尾電壓超過輸入電壓的下限,造成出錯;③位值往往是在過0前后采樣比較得到,參照的理論過0時刻也可能受干擾,所以必須加以補償,否則會采錯。

如果可以實現容錯,可信賴性就能得到提高。僅僅判出錯而不能容錯,系統丟幀不減少,控制層面參與表決的有效消息數量會不足,使4冗余的控制系統降到少冗余無冗余,從而失效。錯誤檢不出時,會使參與表決的正確消息數量不足,例如輸入為30、30、20、20時,你不能判斷誰是正確值誰是錯誤值。有干擾時,兩種情況可能同一周期內發生,例如留下30、20、20,表決的結果20可能是漏檢的錯誤值。

1 外部干擾下的問題

1553B對抗干擾的測試要求見第4.5.2.1.2.4款:“終端收到的所有字按標準條款4.4驗收后,最大字錯率不超過10-7。”測試條件是疊加1 kHz~4 MHz的高斯噪聲,其幅度有效值為140 mV。測試處的信號電平峰-峰值為2.1 V。字錯包括所有使狀態字錯誤標志置位之錯,以及使終端不響應有效指令字之錯。這里有4個問題:①測試的環境是常規實驗室,并指出繼電器的切換通常看作最嚴重的脈沖干擾源[3],但是似乎是把140 mV看作了外部干擾源來分析的,忽略了輸出波動的影響;②其輸出波形上的(4.5.2.1.1.2)干擾幅度有±900 mV[3],折算到輸入上的有效值已占160 mV,測試的干擾幅度顯然不足;③以未報錯作成功是不對的,因為其中含有的漏檢錯不能代表出錯的全部情況;④1553B的歷史較早,當時還沒有功能安全的概念,從當今的角度看,即使字錯率是10-7也是不夠的。

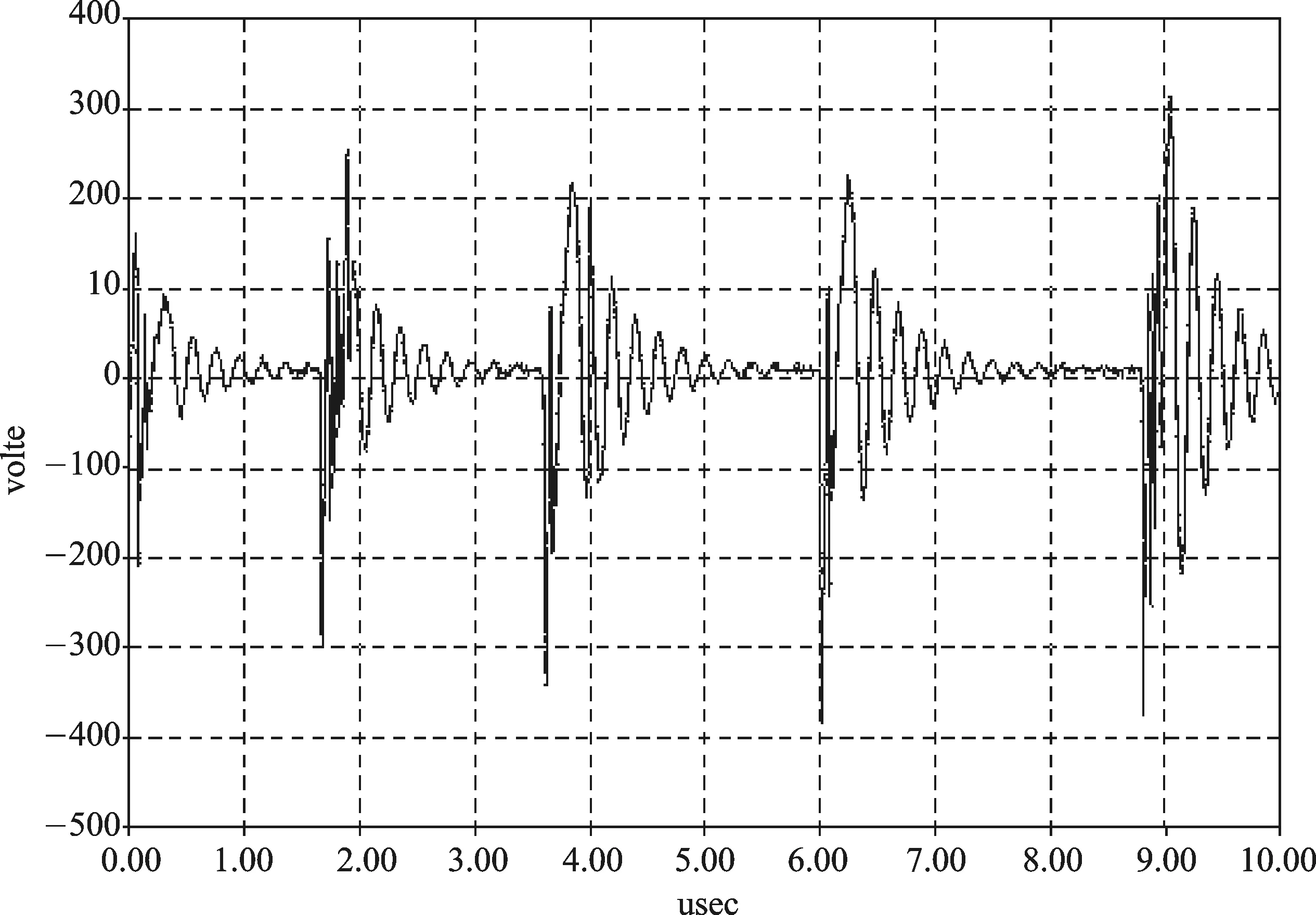

當開關為感性負載時,儲存在線圈中的能量要釋放,形成反電勢,在電源系統中來回反射。航空中用的電液閥具有與繼電器開閉時相似的干擾特性,返回彈簧儲能也要釋放。福特汽車公司認為[2]應該以實物作測試源:經驗表明,用福特建議的測試,可發現通過標準(ISO7637-2,ISO7637-3)的測試而未發現的一些異常。他們補充測試的波形有5種,如圖1、圖2所示,其中C為開關<0.4 A的感性負載。

圖1 Ford汽車公司對汽車電子設備要求的傳導干擾兼容測試波形之一

圖2 圖1中6~7 μs的局部放大

由圖2可見,如果設備無法對抗來自電源的幅度大于±50 V傳導干擾或輻射耦合干擾,那么就有分布在1 μs內的代表邏輯“1”的干擾,或者分散在0.5 μs內的多次單向干擾。在圖1的9~10 μs處可以見到幅度更大的干擾。

曼2碼過零點在1/2位處,我所見到的譯碼器方案一般是在1/4位和3/4位處對二次收發器輸出的數字電平進行采樣,如果圖2中“1”干擾可以大于總線上傳送的“0”電平,譯碼器將以干擾作為輸出。如果一個字發生了2次這樣的漏判,1553B的字的parity校驗是沒有能力發現的,這就引起了錯字漏檢,后果很嚴重。如果受到了干擾,就會報錯,使字及相關的消息作廢。

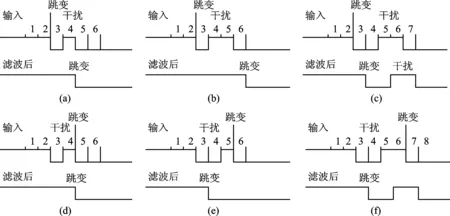

劉曙蓉[4]考慮了抗干擾的設計,他們采用移動窗口3中取2處理收發器輸出的采樣,這可以減少了一部分干擾,但仍不理想,效果如圖3所示。

圖3(a)~3(c)表示干擾在名義跳變沿后靠近地方的情形。圖3(a)中干擾發生在slot4,由123表決的結果,正常slot3被否定掉, 234表決結果干擾slot4仍保留,345表決結果slot5仍保留正常輸入值,其后一樣。所以干擾被理解為跳變前電平,跳變沿被推遲2slot。圖3(b)中干擾有2slot時長,345表決結果slot5仍保留干擾輸入值,456表決結果slot6否定正常輸入值,所以干擾被理解為跳變前電平,跳變沿被推遲4slot。圖3(c)中長干擾發生在slot5、slot6,234表決結果slot4仍保留正常輸入值,345表決結果slot5否定掉干擾,456表決結果slot6仍保留干擾,567表決結果slot7否定掉正常輸入值,678表決結果slot8仍保留正常輸入值,如此,跳變沿被推遲1slot,但是干擾仍存在并移動了位置。

圖3(d)~3(f)表示干擾在名義跳變沿前靠近地方的情形。圖3(d)中干擾發生在slot3,由123表決的結果,干擾slot3被否定掉,234表決結果slot4仍保留正常輸入值,345表決結果slot5仍保留正常輸入值,其后也是這樣。所以跳變沿不變,干擾被濾掉。圖3(e)中干擾發生在slot3、slot4,由123表決的結果,干擾slot3被否定掉,234表決結果slot4仍保留干擾,345表決結果slot5否定正常輸入值,456表決結果slot6仍保留正常輸入值,所以干擾仍存在并移動了位置,跳變沿被提前2slot。圖3(f)中長干擾發生在2 slot前的slot3和slot4,由123表決的結果,干擾slot3被否定掉,234表決結果slot4仍保留干擾,345表決結果slot5否定掉正常輸入值,456表決結果slot6仍保留正常輸入值,567表決結果slot7否定掉正常輸入值,678表決結果slot8仍保留正常輸入值,如是干擾仍存在并移動了位置,跳變沿被提前3slot。

圖3 3中取2的效果

總結一下3中取2的效果,如果干擾只占1 slot,那么隨干擾位置的不同,濾波后的跳變沿可能不變,或推后2 slot。如果干擾占2 slot,那么隨干擾位置的不同,濾波后的跳變沿可能推后1slot或4slot,或者提前1slot或3 slot,并且干擾仍然存在。

跳變沿是位同步的基準,由于濾波而引起的跳變沿變化本身就是一種不確定因素,如有同步機制使采樣位置錯誤跟隨就會產生譯碼錯誤。

即使沒有跳變沿位同步,2 slot的干擾也足以造成1/4、3/4位采樣的錯誤。例如圖3(b)中3/4位采樣位在slot6,本來采不到的錯,濾波后卻采到了。圖3(c)中3/4位采樣位在slot6,本來采到的錯,濾波后仍然采到了。

2 拖尾電壓的問題

硬件上,1553B節點采用變壓器與總線耦合方式來傳送模擬電平,總線空閑時其電平應該為0。但是由于變壓器繞組匝數誤差、漏磁的差別、雜散電容的差別、驅動電路切換點并不在位時間的正中點、系統中反射波的復雜影響造成切換點偏移和曼碼正負幅度的差異等等,空閑時的電平會有一個衰減或持續的波動。

標準的第4.5.2.1.1.4款為終端輸出電壓對稱性,規定在最后一個字的最后一位的位中過0點之后2.5 μs后測取點的電壓波動不超過±250 mV(簡稱拖尾tail-off)。但是并沒有規定結束測試的時刻,也就是講波動的持續時間可以延續到2.5 μs后很長的地方。據稱衰變的時間常數可達25 μs[3]。另一方面,第4.5.2.1.1.3款規定接收時或無電時測取點的噪聲小于14 mV RMS,但它并不能解釋為對拖尾有時間限制。

1553B終端輸出電壓和終端輸入電壓的測取點均在隔離變壓器與耦合變壓器的兩條連線間,繪法的差別只是反映了耦合變壓器阻抗變換的結果。在忽略總線上的衰減時可以導出終端輸出電壓的1/4送到另一個節點的終端輸入。由于一個節點A傳送后的250 mV的拖尾送到另一個節點B的輸入時已經衰減到63 mV,所以不會引起B產生誤動作。但是A本身的輸入電路必須監視總線上最早2.5 μs后到達的響應(4.3.3.8規定的響應時間為4~12 μs)。

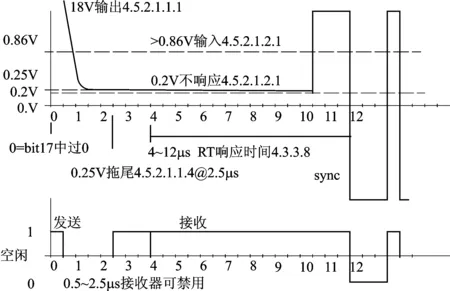

1553B第4.5.2.1.2.1款規定了終端輸入電壓的大小。節點必須對0.86~14 V的輸入差(峰-峰值,以下無專門說明均為峰-峰值)作出響應,對小于0.2 V的輸入差不作出響應。所以當拖尾電壓差為250 mV時,便可能產生不希望的非空閑的邏輯讀數,解釋為sync已經開始,從而引起后續定時的錯誤。單調衰減的拖尾過程如圖4所示。

圖4 單調衰減的拖尾過程

常見的譯碼器識別sync的方案有兩種:①以第一個跳變作sync邊界的方案,由于拖尾,當拖尾電壓極性與上一位不同時,第一個跳變立即出現,在4 μs時未見到sync中間跳變沿(實際sync還在后面開始時),認為新字錯誤,從而只能誤判。②以出現數據流00 0111(或11 1000)(以半位時間為單位)作sync識別的方案,當拖尾與新sync前半段電平不同時(例如11111),會見到與真正sync相連的111 1100 0111數據流,就會將11 1000錯讀為sync,將最后的11(1)讀為bit1,bit1內無跳變,也只能判錯。這2個方案還假設sync中的跳變沿未受干擾,如果其中有干擾被誤解為跳變沿,也會報錯,所以是不能容錯的。

現在估計一下這種出錯的概率。為了使接收器正確響應輸入電壓,它的切換點應設計在(0.86+0.2)/2=0.53 V處:大于0.53 V時應該輸出邏輯狀態,小于0.53 V應該不響應輸入,視為空閑。假定工藝的成品切換點的分布服從正態分布,那么為使成品率達到99.999 7%,這個方差為0.005 V。此時接收器會有1.5×10-6的概率對小于0.2 V的輸入作響應,有1.5×10-6的概率對大于0.86 V的輸入不作響應。根據此分布模型,按此工藝分布生產的接收器會有3.7×10-5的可能性對250 mV的輸入產生響應。如果沒有正確處理拖尾的方案,因此而產生的字錯率貢獻為3.7×10-5。注意:1553B標準沒有涉及因拖尾而造成字錯的測試條款。

當電源本身有紋波(例如30 mV)、電源有傳導干擾(例如30 mV)、經過未被75%屏蔽的輻射干擾進入(例如20 mV)、工作溫度變化引起接收器比較器切換點的漂移時(例如10 mV),相當于輸入波動幅度的增大。假定等效的輸入為0.3 V(在拖尾上再疊加50 mV),此時接收器會有5.7×10-4的可能性在應該是空閑時產生虛假的sync開始,不加容錯處理時,字錯率貢獻達到5.7×10-4,比1553B設計者容許的大5 700倍。

偏置比較器的切換點可以減小拖尾的影響,但實際上等效于收緊工藝誤差,提高產品成本。拖尾引起問題的事件是有記錄的,例如B1轟炸機的1553B系統中拖尾被終端理解為消息的有效部分而誤動作[3],后來靠改硬件而解決。全靠硬件選用和生產、維修檢查來消除拖尾是十分昂貴的,所以需要挽救與拖尾相連接的來自其他節點的有效sync,從而減少誤報錯。

3 跳變時間變化

連接在總線上的各分支處存在阻抗的不連續,在耦合變壓器連接分支時,變壓器的分支段也是同樣的特征阻抗Z0電纜,從總線側看,耦合變壓器的輸入阻抗應為2Z0。這個阻抗與兩個0.75Z0的限流電阻串聯后成為總線特征阻抗Z0的分流電阻。標準規定的Z0是75 Ω,所以有分支的地方阻抗突變為3.5Z0//Z0=58 Ω。

由傳輸線理論可知,阻抗減少時會產生一個反向的疊加電壓,這個反射電壓經過一段時間到達接收節點,所以又與分枝-接收節點的距離有關。1553B沒有規定總線長度,1553A規定的長度為300英尺,所以來回時間大概是600×1.6=960 ns,距離近時這個反射回來的時間也少。它可能和下一個跳變電壓疊加,使接收器輸入電壓的上升/下降過程提前或推遲,造成接收器輸出跳變時刻的變化。

標準4.5.2.1.2.1對輸入波形的兼容性規定是:容許的實際跳變沿對名義跳邊沿的變動幅度為±150 ns時仍能正常工作。

當用16M對每位采樣時,過0點在slot8,作1/4、3/4位處采樣就是slot4和slot12處。±150 ns時間變動相當于±3 slot,即過0點會在slot5~slot11處,對抗其余變動的余量僅1個slot。

驗收測試時,sync過0位置決定了采樣的基準位置。如果一條消息從總線空閑開始測試時受到干擾,取了一個偏移的位置,例如偏離真正值100 ns,那么在測試時最多可偏移250 ns,造成1/4、3/4位處采樣錯誤,從而通不過測試。

在實際應用時要考慮硬件時鐘精度。第4.3.3.3款規定1 s內的發送位速率穩定性至少為0.01%。如果一條消息有32個數據字,那么加上指令字或狀態字會有33個字的連續發送,到結尾時會有33×20×0.01%=0.066個位的變化,發送器與接收器可能差0.13位=132 ns。假定開始傳送受到干擾,偏離真正值100 ns再加反射可能偏移50 ns,這意味著1/4、3/4位采樣的出錯可能性很大。

所以在每個字中應該采取同步措施。用鎖相環同步方案有一個穩定的過渡過程,而且每個新字開始時sync有周期性的同步沿缺失,再加不規則的與信號幅度相當的大噪聲干擾,會使其不能滿足需要。

4 解決方案

全面改進的內容非常多,這里介紹解決方案中抗干擾的一部分。干擾的頻譜與容許的上升沿頻譜相當,用模擬濾波的方法是不適用的。

收發器有兩個輸出,以RX=1來表示輸入電平差為正(差>0.86 V時一定為1),RX=0來表示輸入電平為空閑(差<0.2 V時一定為0)。RXN=1表示輸入電平差為負(差<-0.86 V時一定為1),RXN=0來表示輸入電平為空閑(差>-0.2 V時一定為0)。當輸入電平差在某區間時,RX和 RXN均為0,這段時間稱為接收器空檔時間(Receiver gap time),輸入電平差為0.86 V時可以長達365 ns。任何跳變都會進入這個輸入電平差區間,所以都會遇到RX和RXN=0的情況,必須經過處理才能用作譯碼器采樣輸入。

將RXN和 RX作為RS觸發器的兩個輸入(R,S),而RS觸發器的1輸出(對應RX)作為譯碼器的邏輯輸入In。將RX和 RXN或非后作為總線狀態Idle,這樣當總線空閑時(RX=0 同時RXN=0),Idle=1。而總線非空閑時,Idle=0,才使用In。In沒有空檔,如果收發器輸入有干擾,RS觸發器會相應變化,In也變化,譯碼器就把干擾采進去了。

譯碼器用16M對In采樣,每8 slot組成半位(HB1和HB2)。理想狀態下,HB內8個slot為相同的值,有干擾時會有不同值。用多數表決的方法確定HB的狀態,例如8個slot中In=1有5~8次,那么HB=1。然后用得到的HB1和HB2來確定位值bit和是否出錯:①沒有平局時,當HB1=HB2時為出錯;否則bit=HB1。②如果HB1和HB2中有一個出現了平局(In=1和In=0各4次),那么按未出現平局的HB來決定:HB1有平局時bit=not HB2;HB2有平局時bit= HB1。③當兩個HB16 均為平局時為出錯。

在sync段寬度為3slot的干擾在原來的設計中有6/13的概率被采集到,從而報錯,而在新方法時全部容錯糾正。在原來的設計中,payload段寬度為4slot的干擾有8/12的概率被采集到;寬度為3slot的干擾有6/13的概率被采集到;寬度為2slot的干擾在原來的設計中有4/14的概率被采集到;3個寬度為1slot干擾在原來的設計中有3/8的概率被采集到,從而報錯。在新方法時全部容錯糾正。

[1] 楊福宇.1553B通信協議的可依賴性討論[J].單片機與嵌入式系統應用,2017(1):5-8.

[2] Ford Motor Company.Component and Subsystem Electromagnetic Compatibility Worldwide Requirements and Test Procedures ES-XW7T-1A278-AC,2003.

[3] Multiplex applications handbook:mil-hdbk-1553a.1,1998.

[4] 劉曙蓉.預測校正型曼II碼譯碼器技術研究與實現[J].微電子學與計算機,2005(9):141-143.

Improved Reliability of 1553B Fault Tolerant Decoder Against Interference

Yang Fuyu

(Chongqing Institute of Industrial Automation and Instrumentation,Chongqing 400123,China)

By discussing various 1553B decoder design,three hardware dependability defects are found:no fault tolerance design against disturbance,tail-off voltage higher than low range input threshold and lack of adaptation to zero-crossing change caused by disturbance.Hence the fault tolerance design of decoder is the key element to improve 1553B dependability.The anti-disturbance part of new design is disclosed in the paper.The new design can tolerant up to 3 slots disturbances.This is more important for enhanced 1553B chip which works at 2 Mbps or more.

1553B;fault tolerant;decoder

TP302

A

?士然

2017-04-05)